单相电机转动的原理,单相电机正反转的接线方法

有关单相电机的知识,单相电机转动的原理是什么,如果要实现电机的正反转,就必须搞清楚单相电机是如何启动的,单相电机正反转怎么接线,下面具体来看下。

一、单相电机转动的原理

三相电机正反转的关键是换相,让三相存在120°的相位差,从而实现电机的正反转。对于单相电机来说,如果要实现电机的正反转,就需要明白单相电机可以启动的原因。

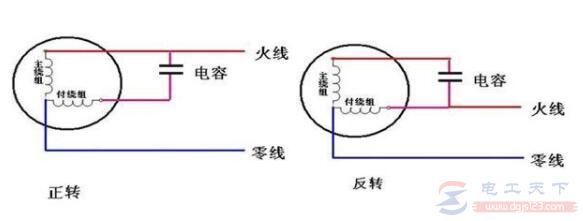

在启动绕组后,串联合适容量的电容,让两个绕组的相位差相差90°,从而产生磁场旋转,如果这个连接方式记为正转,那么调换一下接进电容的电源线,电机产生相反的磁场,就能实现电机反转。

单相电机正反转的要求:并非所有的单相电机都可以正反转,很多电机不能实现正反转,比如罩极电机、潜水泵电机等,这些电机也有电容,但由于用途的特殊性,在使用时会对电机加以改造,增加单向轴承、反转卡套等。

其他无论是双电容电机还是单电容电机,理论上都是可以实现正反转的,大家可以深入了解下电机的主绕组、副绕组、离心开关的作用,即可以掌握单相电机的转动原理。

二、单相电机正反转的接线

1、主副绕组的区分

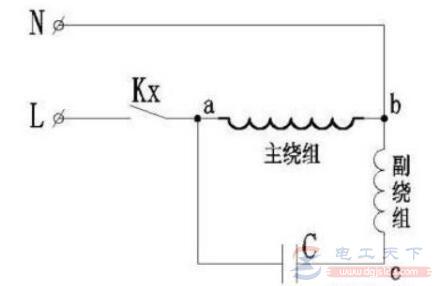

需要的工具为一块带测量电阻值的万用表,把万用表的电阻档位打到X10K,测量电机中引出的三根线,首先两两进行测量,阻值最大的为总绕组,余下一根是公共端。

然后,继续进行测量,阻值较小的是启动绕组(主绕组),阻值较大的为运行绕组(副绕组)。

2、正反转接线方法

分清楚了主绕组和副绕组,那么电容到底怎么连?

启动电容的并联在主绕组和副绕组上,即三根线中测量的电阻值最大的两根线,电容中一根接入电源火线,公共端接入电源零线,如果此转向记为正转,那么把火线接入电容的另外一根,就是反转。

总结:

并不是所有的单相电机都支持正反转,如果电线出头是四根线,甚至是五根线,就必须先弄清楚哪几根用来调速,哪几根是绕组,然后再进行接线。

https://www.dgjs123.com/diandongji/23832.html

单相电机通过启动绕组和电容产生相位差以实现转动。正反转接线关键是主副绕组的区分,通过改变电容的连接方式可实现电机转向。但并非所有单相电机都支持正反转,如罩极电机、潜水泵电机等。

单相电机通过启动绕组和电容产生相位差以实现转动。正反转接线关键是主副绕组的区分,通过改变电容的连接方式可实现电机转向。但并非所有单相电机都支持正反转,如罩极电机、潜水泵电机等。

1767

1767

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?