应用场景:FPGA+dp83867e+pc。

使用原因:为了节省FPGA的pin,使用千兆网口dp83867e芯片的SGMII模式。

一、IP核的GUI界面配置

下面直接描述该IP如何使用(只对关键配置界面进行解释):

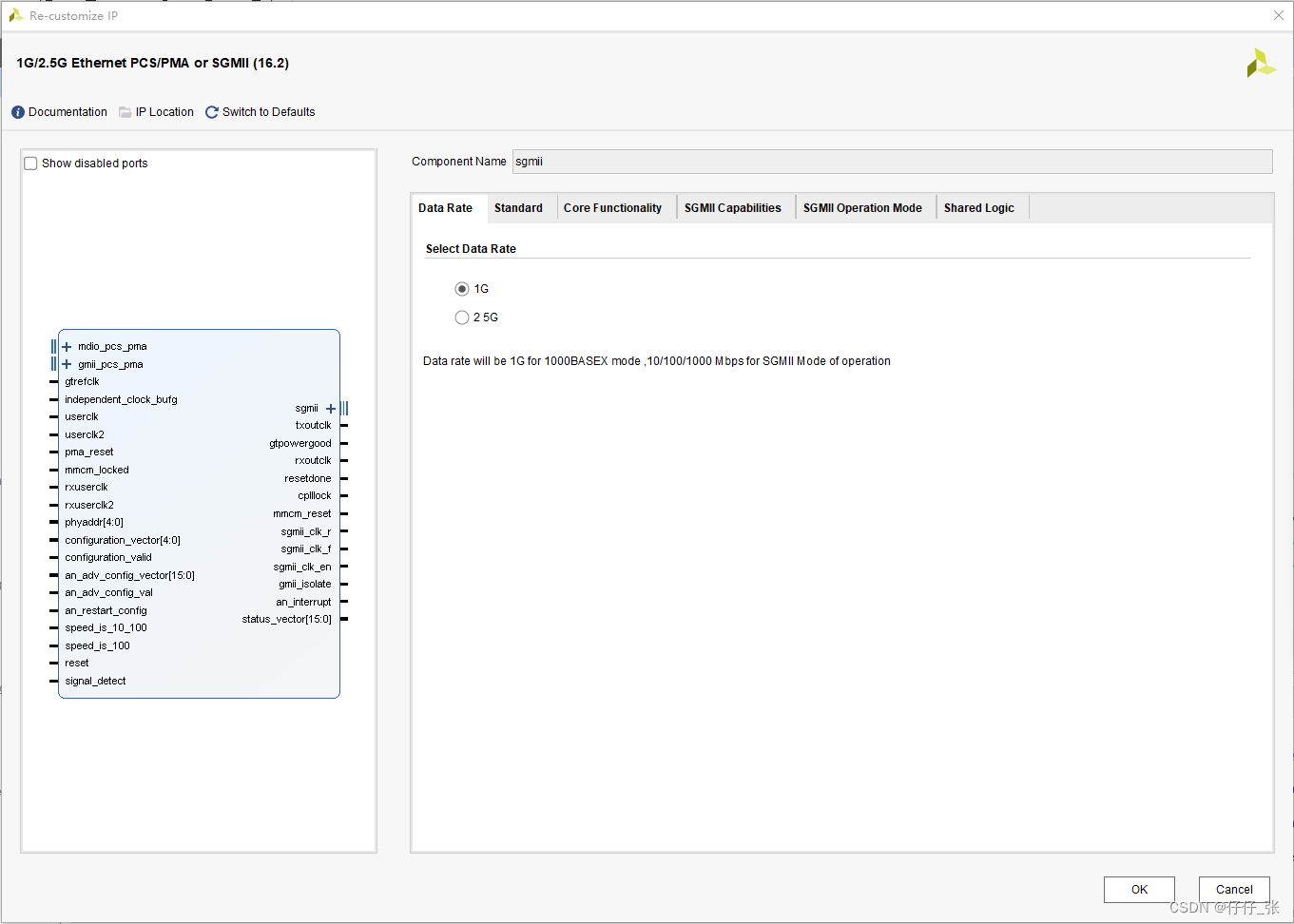

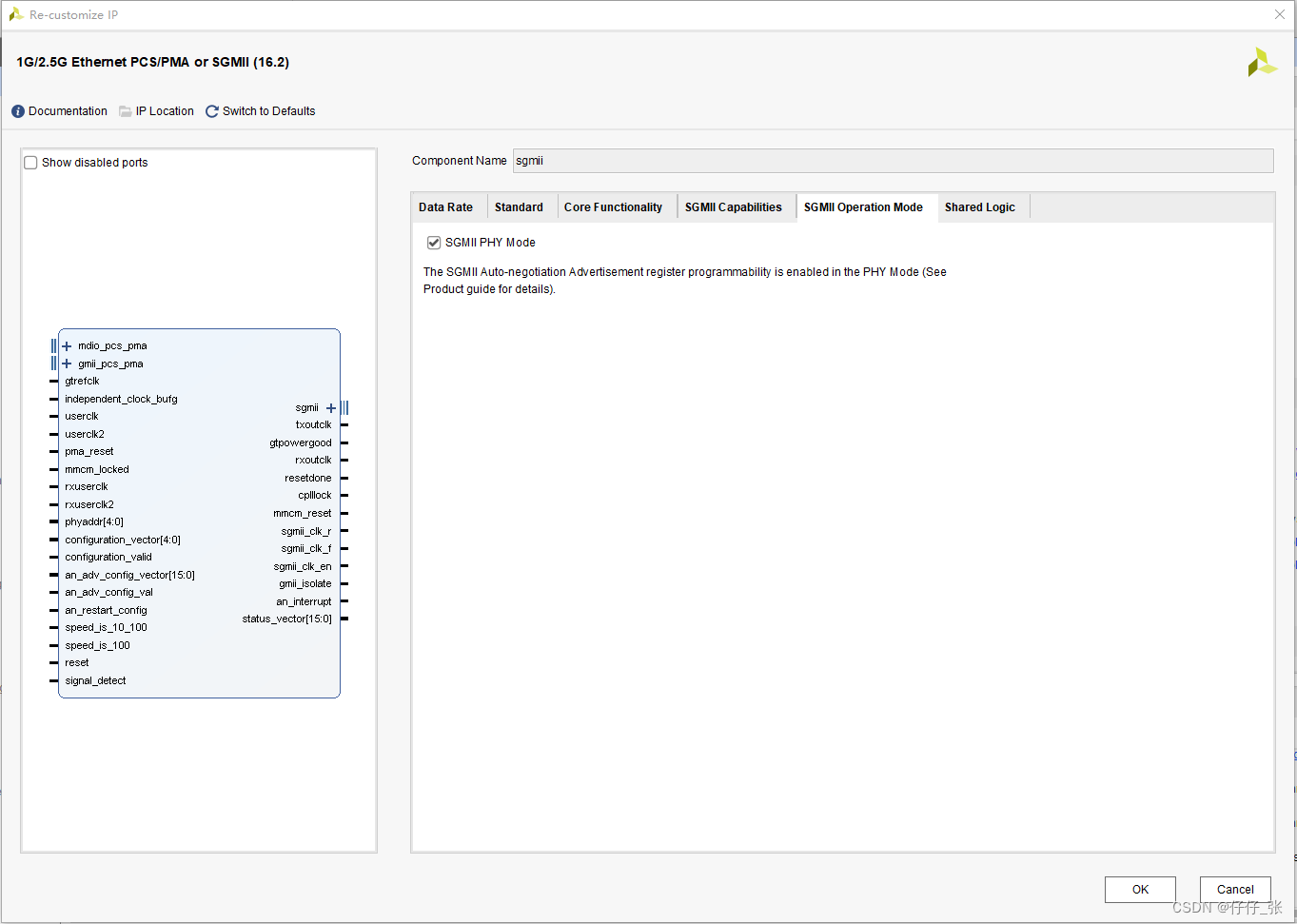

(1)

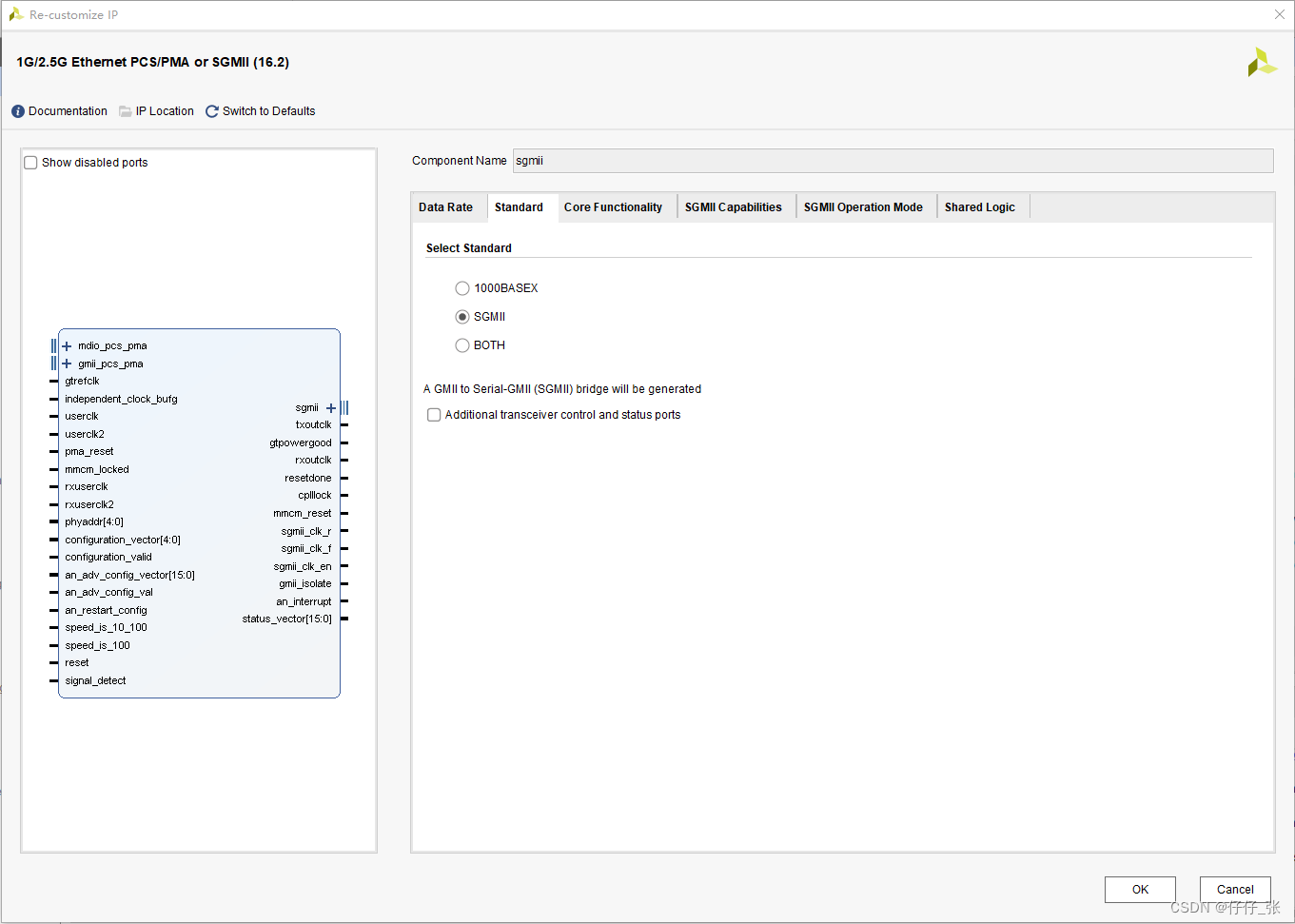

(2)在工程中使用了具有sgmii接口的PHY芯片,所以选择SGMII标准。

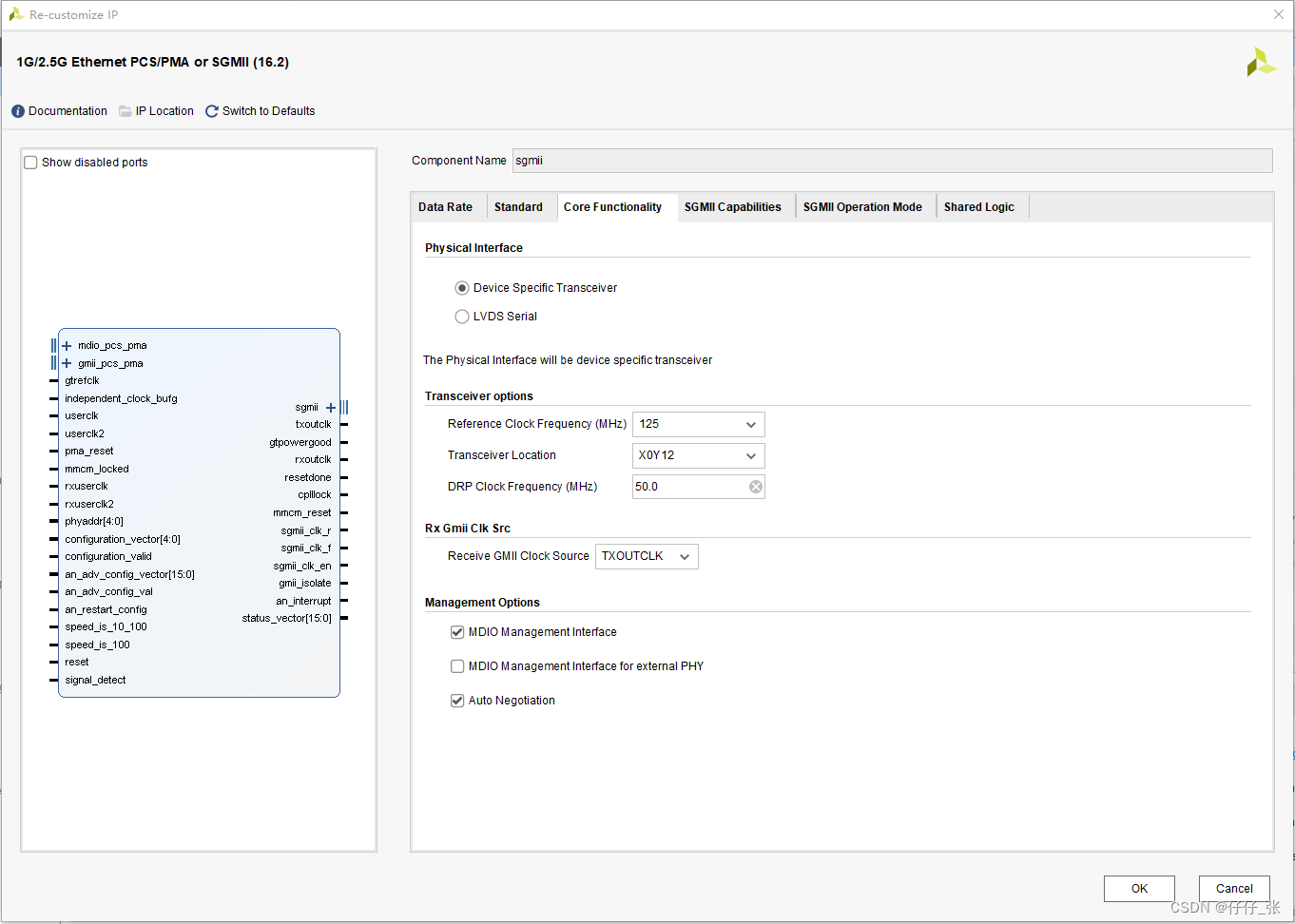

(3)外部PHY芯片的SGMII接口,连接到专用bank225上(即专用收发器上) 。所以接口选择Device Speciflc Transceiver。

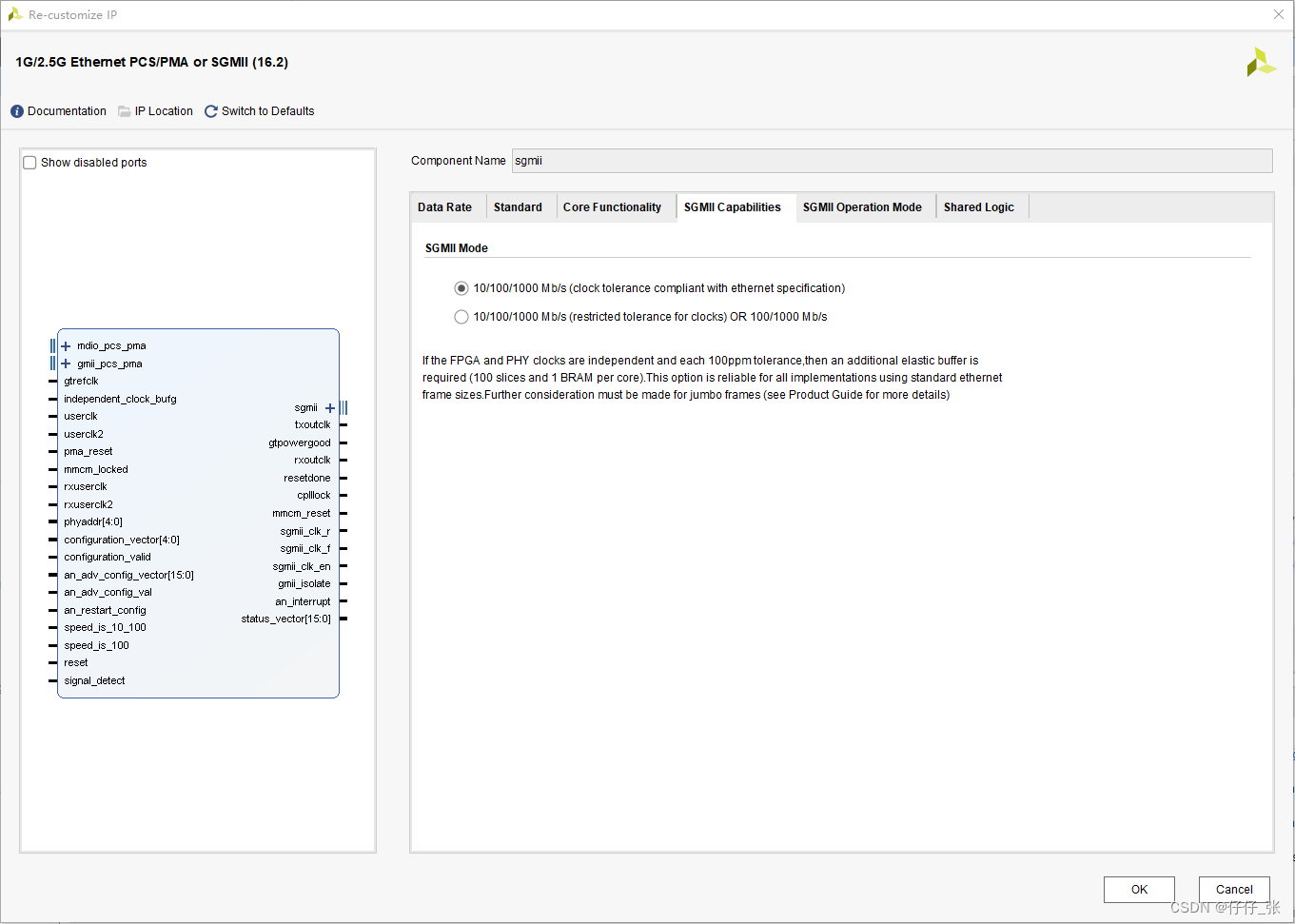

(4)

(5)该配置很关键,必须选择SGMII PHY Mode。

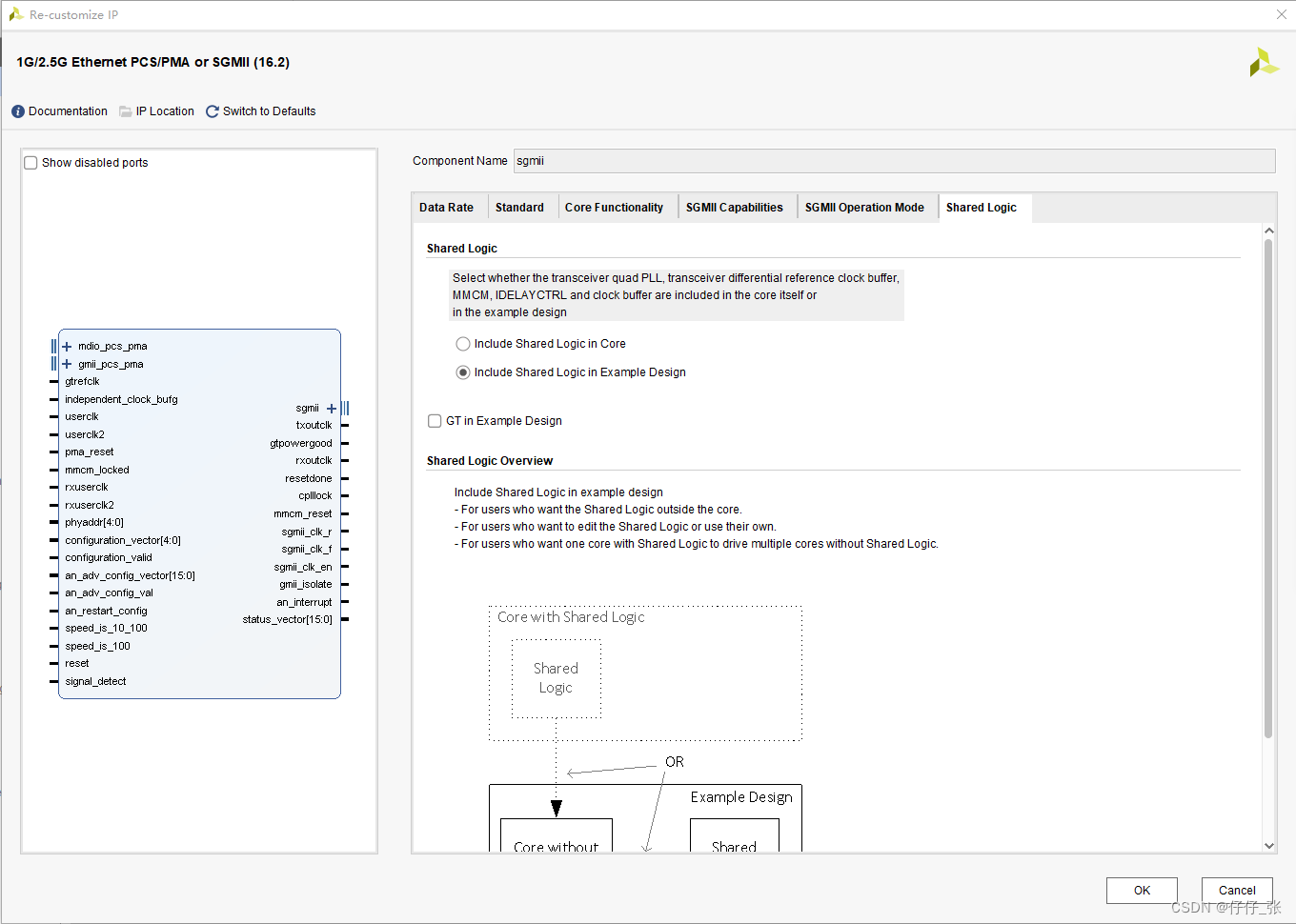

(6)

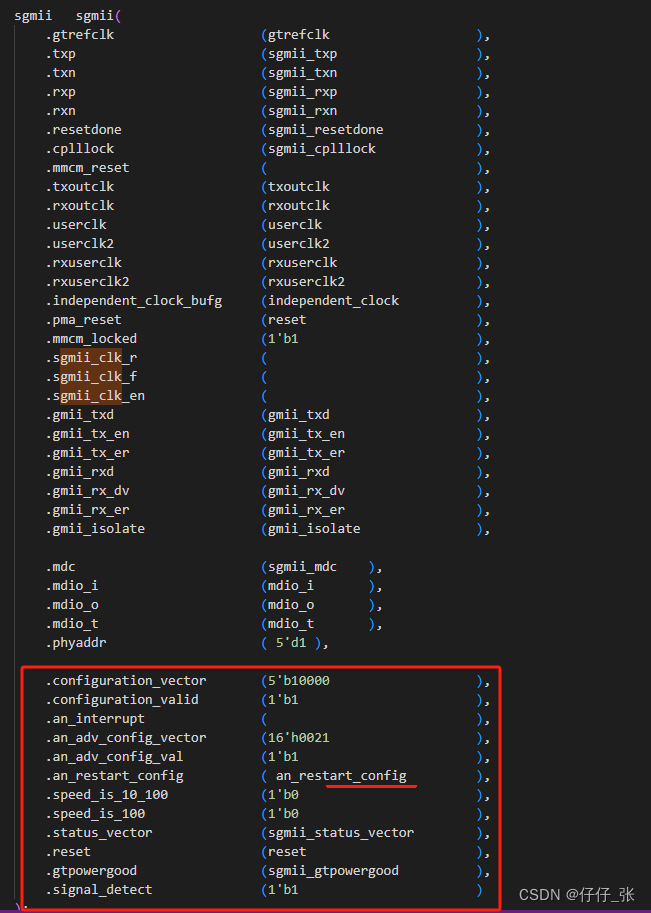

二、该IP接口配置

必须按照上图中配置,否则会导致sgmii接收不到数据。其中信号an_restart_config表示再次配置这些接口信息,上升沿有效。

三、gmii_rxd,gmii_rx_dv,gmii_rx_er;gmii_txd,gmii_tx_dv,gmii_tx_er均同步与时钟信号userclk2_0。

本文详细介绍了如何在FPGA项目中利用dp83867e芯片的SGMII模式以节省pin资源,并重点讲解了IP核的GUI界面配置步骤,包括选择SGMII标准、连接专用bank225以及关键配置选项,如SGMIIPHYMode和时钟同步设置。

本文详细介绍了如何在FPGA项目中利用dp83867e芯片的SGMII模式以节省pin资源,并重点讲解了IP核的GUI界面配置步骤,包括选择SGMII标准、连接专用bank225以及关键配置选项,如SGMIIPHYMode和时钟同步设置。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?