Pesudo Static Random Access Memory 伪静态随机内存

这样看,它是一个内存,和我们熟悉的DRAM,SRAM是一回事。但是,它是伪静态的。说明它不需要像DRAM那样,需要自刷新。

DRAM是完全用电容构造的,因此存在漏电流,要持续保存数据的话,需要不断地自刷新,一般要求32ms或者64ms刷新一次。

PSRAM使用了晶体管和电容来构造,因此可以不需要自刷新,没有DSRAM这个矫情的毛病!它使用一个晶体管和一个电容来存储一个bit的数据。而SRAM需要六个晶体管来存储一个bit的数据。因此,PSRAM有成本低,或者相同成本比SRAM有更大容量的优势。

PSRAM具有SRAM接口协议,外部只要给地址,发读写命令,就可以实现存取,无需DRAM那样要memory controller来控制refresh。

下面这些都可以当作内存使用:

| SRAM | 读取速度快,容量小,可读写,无需自刷新,掉电后数据丢失 |

| PSRAM | 读取速度稍慢,容量稍大,可读写,无需自刷新,掉电后数据丢失 |

| DRAM | 读取速度慢,容量大,可读写,需自刷新,掉电后数据丢失 |

| FLASH(XIP模式) | 读取速度最慢,容量最大,仅可读,无需自刷新,掉电后数据不丢失 |

这里说下,Flash闪存的1个存储单元存储多位数据,这是DRAM和SRAM都做不到的。根据浮栅层中电子的多少,每个存储单元可以表达1比特(SLC)、2比特(MLC)、3比特(TLC)或4比特(QLC)数据。

很多PSRAM芯片是SPI接口的(串口),支持QSPI四倍速或者更高,以提升访问速度。也有并口的的。

使用SPI接口的PSRAM芯片,需要SOC有PSRAM控制器。

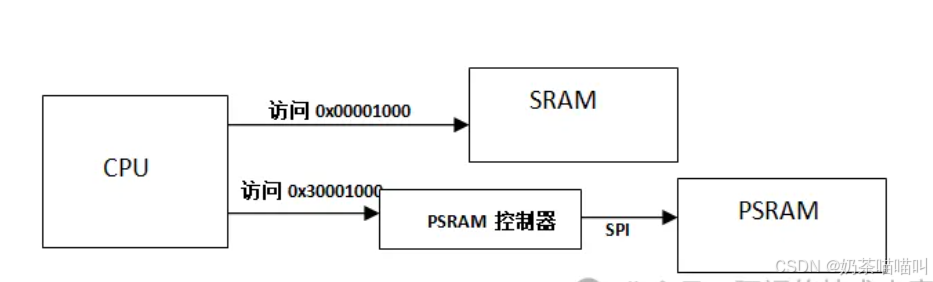

当CPU访问一个地址的时候,会通过自己的地址映射表,判断是访问哪块设备的。如果这个地址是PSRAM区域的,那么CPU是直接访问PSRAM控制器,然后控制器再通过SPI与PSRAM芯片交互,拿到数据。最后控制器再给出数据到CPU。在CPU眼里,就和直接访问SRAM是一样的。

PSRAM控制器把SPI的交互细节隐藏起来了。

使用PSRAM控制器,一般要先初始化,会有如下一些参数,要提前设置好:

unsigned int base; ///< SPI 接口基地址unsigned int cs_base; ///< SPI 接口基地址unsigned int rcmd; ///< 读操作命令unsigned int rcmd_len; ///< 读操作命令长度(bit)unsigned int rcmd_line; ///< 读操作命令总线宽度unsigned int raddr_len; ///< 读操作地址长度(bit)unsigned int raddr_line; ///< 读操作地址总线宽度unsigned int rwait_cycles; ///< 读操作等待时钟数unsigned int rspi_mode; ///< 读 SPI 操作模式unsigned int wcmd; ///< 写操作命令unsigned int wcmd_len; ///< 写操作命令长度(bit)unsigned int wcmd_line; ///< 写操作命令总线宽度unsigned int waddr_len; ///< 写操作地址长度(bit)unsigned int waddr_line; ///< 写操作总线宽度unsigned int wwait_cycles; ///< 写操作等待时钟数unsigned int wspi_mode; ///< 写 SPI 操作模式unsigned int qpi_en; ///< QPI 作模式使能unsigned short clk_div; ///< 时钟分频

// 读操作,0x30000000地址是PSRAM区域volatile uint8_t *data_8 = (uint8_t *)0x30000000;uint8_t n = data_8[0];

// 写操作,0x30000000地址是PSRAM区域volatile uint8_t *data_8 = (uint8_t *)0x30000000;data_8[0] = 0xa5;

2934

2934

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?