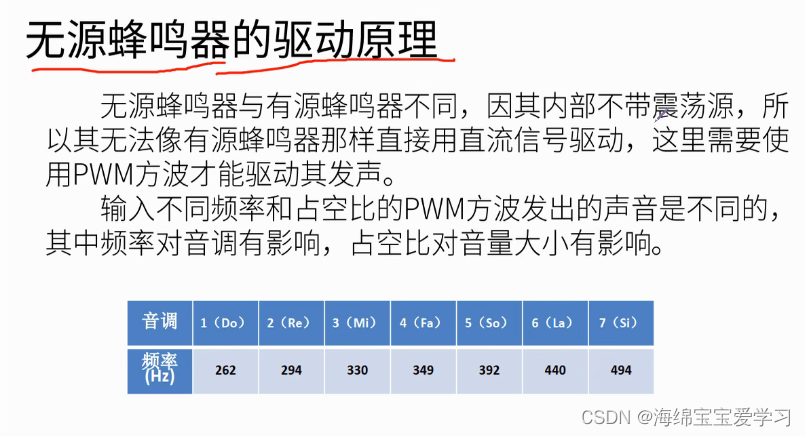

1 理论学习

2 实战演练

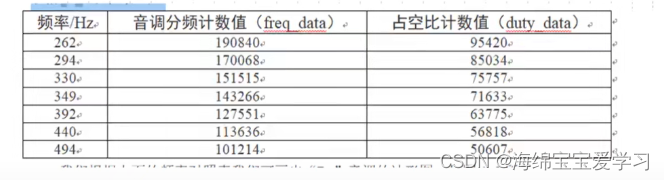

任务:驱动do ra mi fa … 的发声,每个音调0.5s,占空比50%

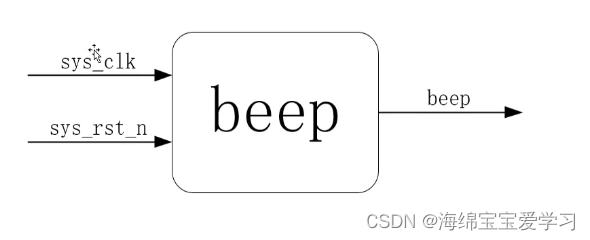

2.1 设计规划

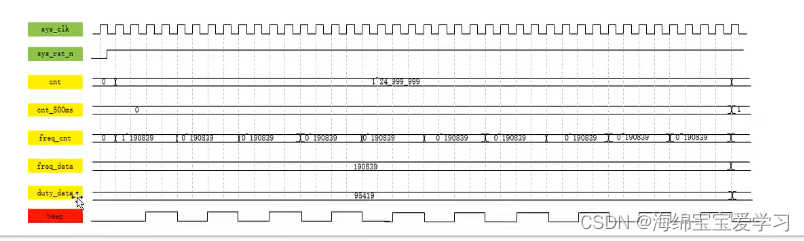

2.2 波形绘制

在duo一个周期内的波形变化,计数值小于占空比计数值的时候为低电平,大于占空比的时候为高电平。

2.3 程序编写与编译

module beep

#(

parameter CNT_MAX = 25'd24_999_999;

parameter DO = 18'd190839,

parameter RE = 18'd170067,

parameter MI = 18'd151514,

parameter FA = 18'd43265,

parameter SO = 18'd127550,

parameter LA = 18'd113635,

parameter XI = 18'd101213

)

(

input wire sys_clk,

inpot wire sys_rst_n,

output reg beep

);

reg [24:0] cnt;

// 最大值为6

reg [2:0] cnt_500ms;

reg [17:0] freq_cnt;

reg [17:0] freq_data;

wire [17:0] duty_data;

always@(posedge sys_clk or negedge sys_rst_n)

if(!sys_rst_n)

cnt <= 25'd0;

else if(cnt == CNT_MAX)

cnt <= 25'd0;

else

cnt <= cnt + 1'b1;

always@(posedge sys_clk or negedge sys_rst_n)

if(!sys_rst_n)

cnt_500ms <= 3'd0;

else if((cnt_500ms == 3'd6) && (cnt == CNT_MAX))

cnt_500ms <= 3'd0;

else if(cnt == CNT_MAX)

cnt_500ms <= cnt_500ms + 1'b1;

else

cnt_500ms <= cnt_500ms;

always@(posedge sys_clk or negedge sys_rst_n)

if(!sys_rst_n)

freq_cnt <= 18'd0;

else if(freq_cnt == freq_data || cnt == CNT_MAX)

freq_cnt <= 18'd0;

else

freq_cnt <= freq_cnt + 1'b1;

always@(posedge sys_clk or negedge sys_rst_n)

if(!sys_rst_n)

freq_data <= DO;

else case(cnt_500ms)

3'd0:freq_data <= DO;

3'd1:freq_data <= RE;

3'd0:freq_data <= MI;

3'd1:freq_data <= FA;

3'd0:freq_data <= SO;

3'd1:freq_data <= LA;

3'd0:freq_data <= XI;

default:3'd1:freq_data <= DO;

endcase

// 数据左移一位 表示乘以2 右移一位表示 除以2

assign duty_data = freq_data >> 1;

always@(posedge sys_clk or negedge sys_rst_n)

if(!sys_rst_n)

beep <= 1'b0;

else if(freq_cnt >= duty_data)

beep <= 1'b1;

else

beep <= 1'b0;

endmodule

tb beep 文件

`timescale 1ns/1ns

module tb_beep();

reg sys_clk;

reg sys_rst_n;

initial begin

sys_clk = 1'b1;

sys_rst_n <= 1'b0;

#20

sys_rst_n <= 1'b1;

end

always #10 sys_clk = ~sys_clk;

// 实例化

beep beep_inst

#( // 这个数据可以改小一点

parameter CNT_MAX = 25'd24_999_999;

parameter DO = 18'd190839,

parameter RE = 18'd170067,

parameter MI = 18'd151514,

parameter FA = 18'd43265,

parameter SO = 18'd127550,

parameter LA = 18'd113635,

parameter XI = 18'd101213

)

(

.sys_clk(sys_clk),

.sys_rst_n(sys_rst_n),

.beep(beep)

);

endmodule

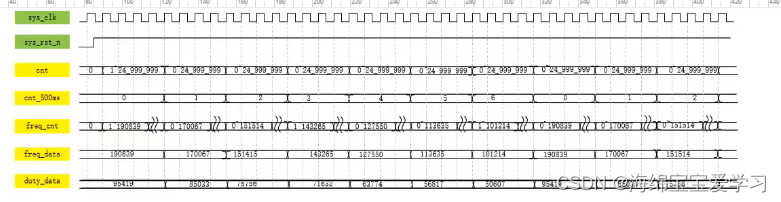

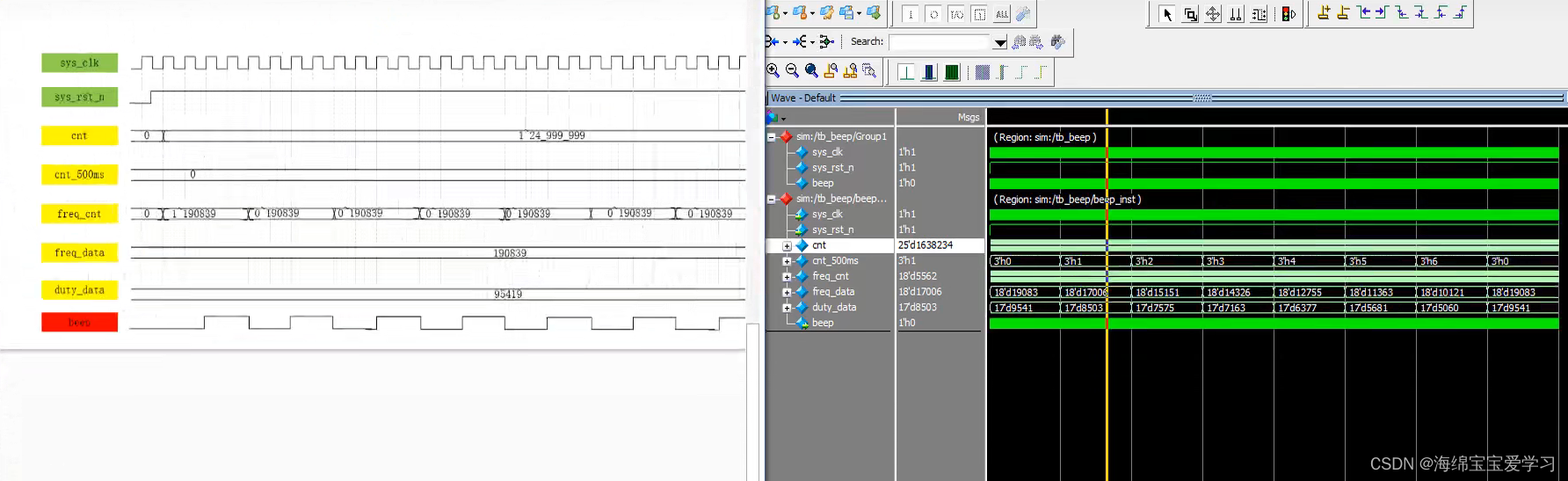

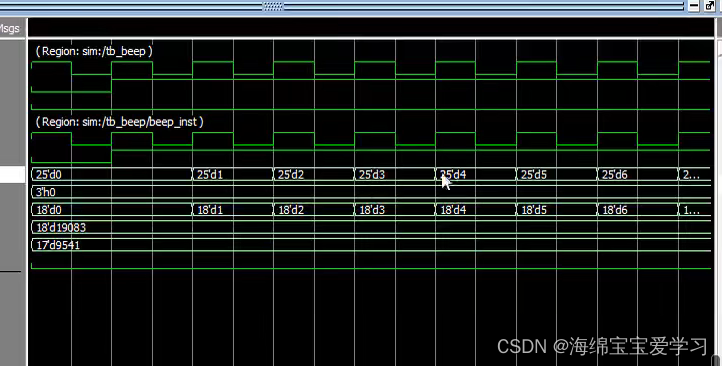

2.4 仿真和波形对比

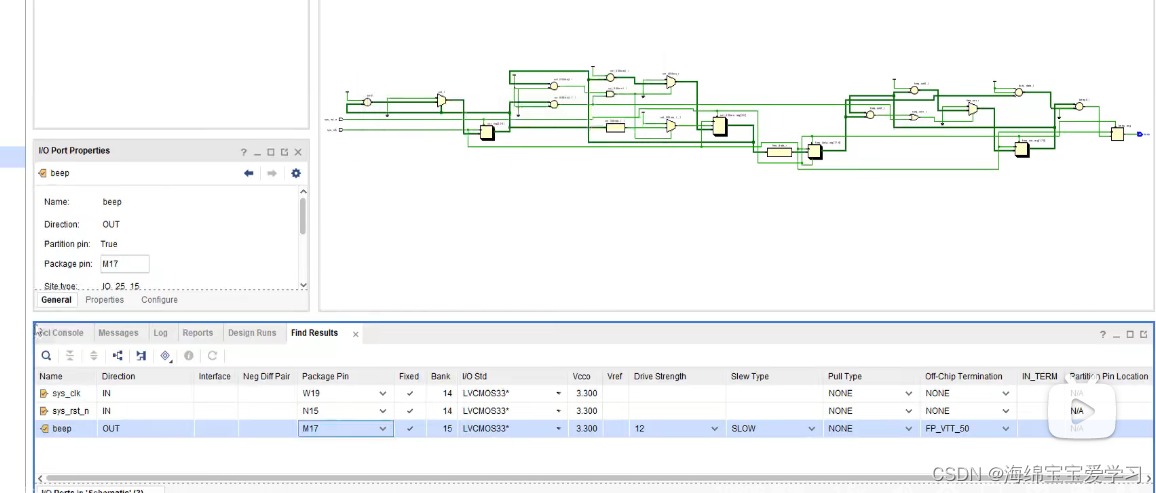

2.5 绑定管教和上板验证

4347

4347

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?