前端采集的振动信号在FPGA中,经过内部FIFO缓存之后发送给DSP做数据处理。DSP和FPGA之间通过EMIF接曰方式连接通FIFO实现DSP和FPGA之间的数据传输。

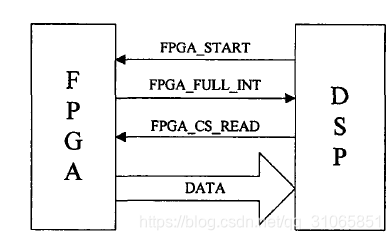

如图所示的FPGA和DSP的接口示意围,图中的DSP控制FPGA采集信号,FPGA中的FIFO数据装满的时候出发DSP开始读取数据,数据读取期间,引脚FPGA_CS_RD处于高电平,读取完毕后跳变为低电平,FPGA读取到对应引脚电平变化时,可W输出数据或者锁存数据。部分代码如下:

Int fpga_sig[ROTATE_DATA];

DDIR_RSET(DDIR,0X00);

CHIP_RSET(DDIR,0X00);

EMIF_config(&emiffig);

Void INTconfig()

{IRQ_setVecs((Unit32)&VECSTART);

Old_intm=IRQ_globalDisable();

eventId0=IRQ_EVT_INT0;

IRQ_clear(eventId0);

IRQ_enable(eventId0);

IRQ_plug(eventId0(),&int0);

IRQ_globalEnable();}

Interrupt viod int0(){IRQ_clear(eventId0);

while(FPGA_READ==0x01)

{…;}}

由程序可知,程序建立一个全局变量的数组用于存放前端的数据,然后对系统中接收数据W及控制FPGA的引脚初始化。接收数据的引脚设置输入方向,上电后控制FPGA开始采样的引脚需要在开始后发生电平变化。此外,还需要配置FPGA对于DSP的中断响应,主要是系统的中断向量的地址、中断标志位的复位W及打开系统的中断设置等。按照系统的要求,进入中断后首先复位中断标志位,当传输标志位处于高电平时,开始数据的传输,数据传输结束之后反馈给FPGA完成本次传输,进入下一个工作状态。

DSP与FPGA通信软件设计

最新推荐文章于 2023-12-29 09:54:55 发布

522

522

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?