文章目录

本文属于使用经验总结,未尽之处不必纠结

AXI-uartlite IP核简介

AXI-uartlite 是Xilinx提供的驱动串口的IP核,用AXI-Lite总线接口和用户进行交互,速度根据不同的芯片调整,总的来说使用比较简单,收发数据也比自己写的串口驱动程序要稳定。本文只介绍基本应用,不涉及中断等操作。

IP核用户接口

debug_uart your_instance_name (

.s_axi_aclk(s_axi_aclk), // input wire s_axi_aclk

.s_axi_aresetn(s_axi_aresetn), // input wire s_axi_aresetn

.interrupt(interrupt), // output wire interrupt

//写地址端口

.s_axi_awaddr(s_axi_awaddr), // input wire [3 : 0] s_axi_awaddr

.s_axi_awvalid(s_axi_awvalid), // input wire s_axi_awvalid

.s_axi_awready(s_axi_awready), // output wire s_axi_awready

//写数据端口

.s_axi_wdata(s_axi_wdata), // input wire [31 : 0] s_axi_wdata

.s_axi_wstrb(s_axi_wstrb), // input wire [3 : 0] s_axi_wstrb

.s_axi_wvalid(s_axi_wvalid), // input wire s_axi_wvalid

.s_axi_wready(s_axi_wready), // output wire s_axi_wready

//写应答端口

.s_axi_bresp(s_axi_bresp), // output wire [1 : 0] s_axi_bresp

.s_axi_bvalid(s_axi_bvalid), // output wire s_axi_bvalid

.s_axi_bready(s_axi_bready), // input wire s_axi_bready

//读地址端口

.s_axi_araddr(s_axi_araddr), // input wire [3 : 0] s_axi_araddr

.s_axi_arvalid(s_axi_arvalid), // input wire s_axi_arvalid

.s_axi_arready(s_axi_arready), // output wire s_axi_arready

//读数据端口

.s_axi_rdata(s_axi_rdata), // output wire [31 : 0] s_axi_rdata

.s_axi_rresp(s_axi_rresp), // output wire [1 : 0] s_axi_rresp

.s_axi_rvalid(s_axi_rvalid), // output wire s_axi_rvalid

.s_axi_rready(s_axi_rready), // input wire s_axi_rready

.rx(rx), // input wire rx

.tx(tx) // output wire tx

);

端口描述

| 端口 | 描述 |

|---|---|

| AWADDR | 写地址 |

| AWVALID | 写地址有效标志 |

| AWREADY | 写地址通道握手信号 |

| WDATA | 写数据 |

| WSTRB | 写数据选通信号,指明数据总线哪个字节有效,在AXI-uartlite中此信号不起作用 |

| WVALID | 写数据有效标志位 |

| WREADY | 写数据通道握手信号 |

| BRESP | 写应答,指明发送是否被成功接收 |

| BVALID | 写应答信号有效标志位 |

| BREADY | 写应答通道握手信号 |

| ARADDR | 读地址 |

| ARVALID | 读地址有效标志位 |

| ARREADY | 读地址通道握手信号 |

| RDATA | 读数据 |

| RRESP | 读应答,指明读操作的状态,是否成功 |

| RVALID | 读数据有效标志位 |

| RREADY | 读数据通道握手信号 |

AXI-Lite接口基本使用

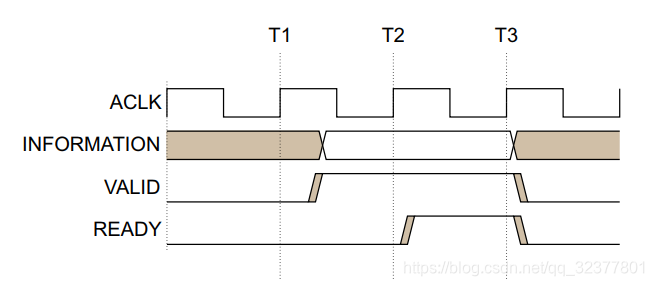

AXI-Lite 总线使用valid+ready信号进行相互握手。

发送地址或数据

发送端提供数据或地址的同时提供同步的valid信号,等待接收端拉高ready信号,valid和ready同时为高时接收端采样数据或地址,即在上图中的T2时刻处开始采样。

AXI-uartlite写地址和写数据要同时进行

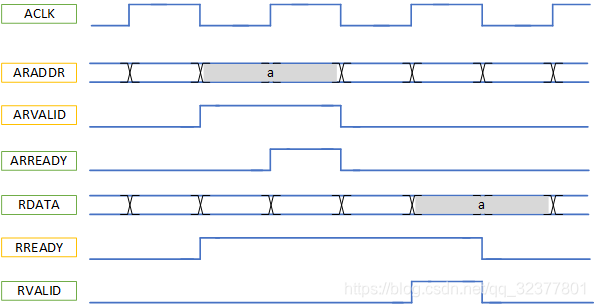

读数据

先发送读地址,同时拉高rready信号,表明可以接收数据,当valid信号拉高时采样数据。

AXI-uartlite IP核寄存器介绍

| 地址偏移 | 寄存器名称 | 描述 |

|---|---|---|

| 0h | Rx FIFO | 接收数据FIFO |

| 04h | Tx FIFO | 发送数据FIFO |

| 08h | 状态寄存器 | IP核状态寄存器 |

| 0ch | 控制寄存器 | IP核控制寄存器 |

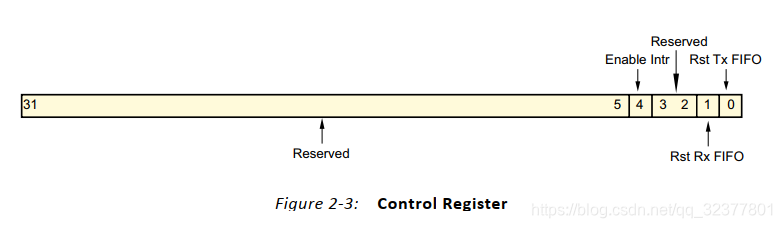

Rx FIFO和Tx FIFO都是低8bit有效,控制寄存器如下图所示:

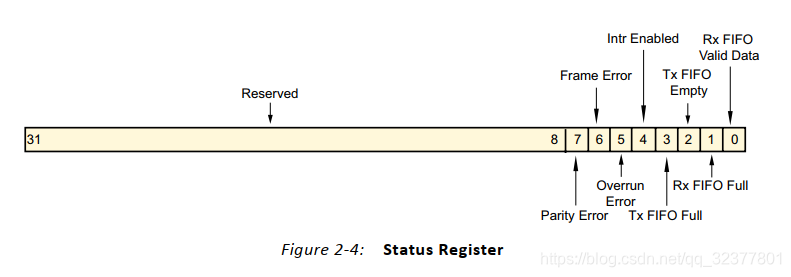

状态寄存器如下图所示:

简单的AXI-uartlite控制模块

`timescale 1ns / 1ps

//

// +------------------------------------------------------+

// | Address | Register Name | Description |

// |---------|---------------|----------------------------|

// | 0h | Rx FIFO | Receive data FIFO |

// | 04h | Tx FIFO | Transmit data FIFO |

// | 08H | STAT_REG | UART Lite status register |

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

367

367

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?