2024/1/22

更新描述(居然被催更)

2025/4/18

1、更新对3.2的时间描述

2、增加范例

一、背景

本人目前从事BMS工作,当前正在进行短路测试。目前已经废了几十个管了(*^_^*);

请注意,当短路时达到了MOS的钳位电压的时候,短路成功是有次数的,每次短路都会对MOS有一定的损坏,所以可能前面两/三次可以,但是在第四次的时候会炸管。反之则不一定,作者并未出现过炸管;

二、信息总结

PCB设计初期要考虑电流流向是否平均流入流出各路MOS;板子的大电流回路的寄生电感;短路时,最大能量是否超过了MOS的最大Eas(雪崩能量);要根据客户的电池进行适配,切勿使用与实际电池的容量和倍率相差过大的PACK进行测试,不然就是浪费力气;等诸多原因,包含MOS的Crss参数等;

1)是否平均流入流出,影响持续时候的热平衡,以及短路时,各单体MOS过电流不会相差太大,不然会导致某个MOS的DS击穿情况;

可以通过更改不同位置MOS的驱动电阻来调节导通时间;

2)寄生电感直接关系MOS关断的瞬时电压大小;

1、尽可能的缩短过电流路径

2、能用1OZ的就别用2OZ,铜厚也影响PCB电感量

3) Eas雪崩

如果总MOS的Eas值够大,短路也是可以过;当然,也要考虑关断速度所影响的关断能量问题;

4) MOS的Rg电阻

通常会使用47R/100R来驱动各路MOS,但不绝对,要考虑发热量的问题;调大可能会造成过热,进而导致MOS耐电流能力下降;

5) 过流和短路波形有区别

我做测试时发现过流保护和短路保护的波形会有很大的区别,过流基本会达到MOS的钳位电压,但是短路很大可能不会到MOS的钳位电压。所以过流只能来测GS的下降时间,我做了这么多次短路,发现一般情况只需要将GS的下降总时间放到30us的点,基本都能过。并且DS电压并不会到MOS的钳位电压。

6)匹配客户的电池包参数

最好是直接拿到客户的电池包进行测试,不然像我手头是动力型方体大容量电池,客户是18650普通3C多串多并,那样可能客户的电池包能很好的过短路,但是自己手头的电池包根本过不了的情况。所以一定一定要知道客户的电池包参数,不要盲目的做短路测试,白费力气!!!

7)MOS封装不同所带来同的抗冲击能力

TOLL > TO-263 > TO252,这个是基本关系,除非MOS很NB,价格也非常NB。

8)MOS选型

一个比较典型的例子,一般情况使用的话电池包的电压不超过MOS的总耐压85%;

有一种情况:

16S三元,按最大电压4.25 * 16 = 68V

85V管子的85%是72.25V

那么也是可以用的,但是短路我认为基本过不了。因为考虑到成本问题,不管是MOS数量还是内阻,都是尽可能的往低成本进行适配。那么如果想过短路只能加MOS数量,或者MOS数量不变的情况下,换更高耐压的MOS。

三、小试牛刀

3.1 改进关断路径

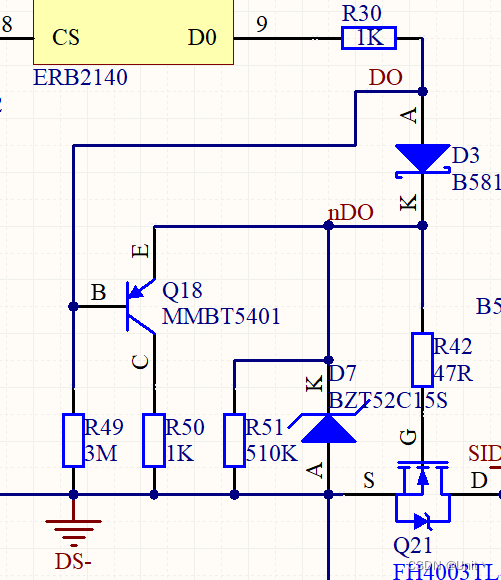

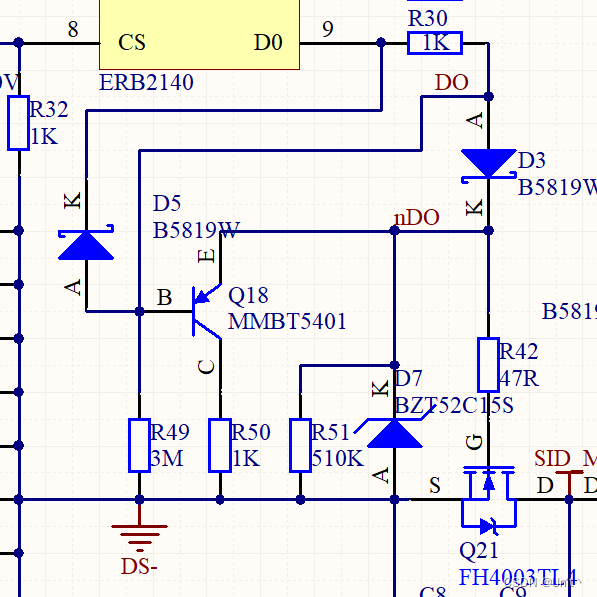

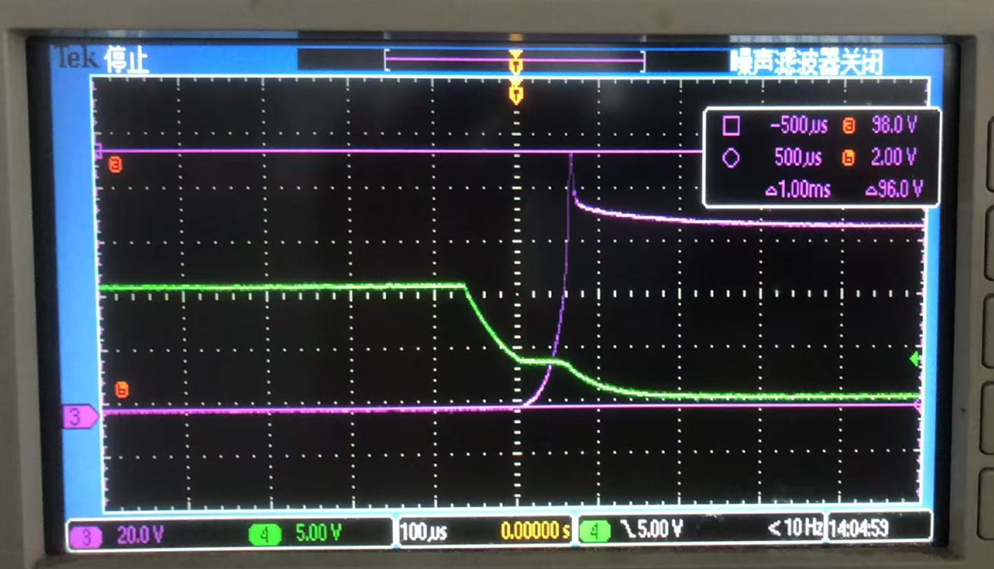

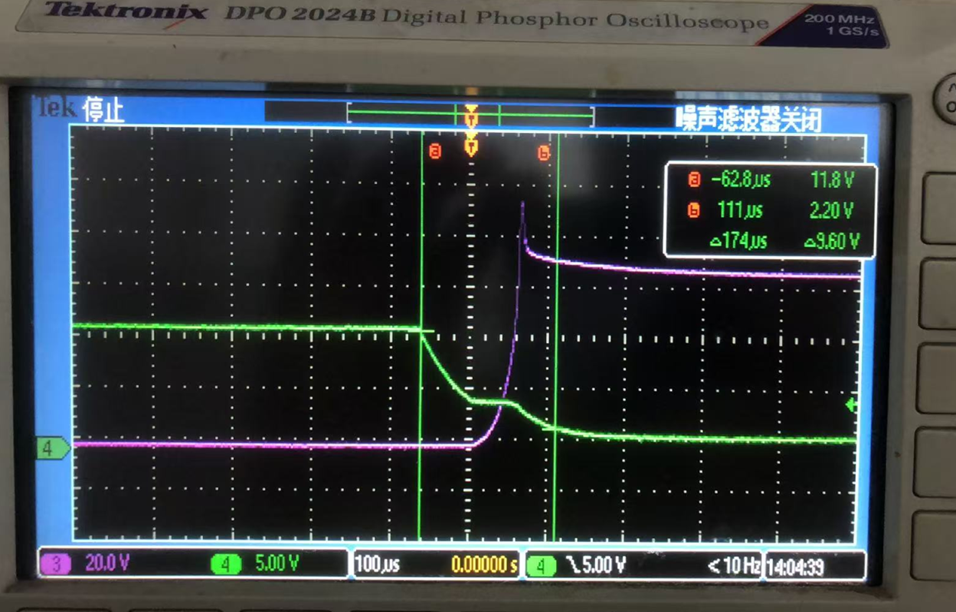

一般情况下,IC的DO脚是推挽架构(不包括早期一些厂商的IC可能拉灌电流能力弱的情况),在低串数低功率的情况下是没什么问题的。但是我前期使用别人的下拉电路的时候,发现过流关断的时候都会发生MOS的GS脚震荡。如图

按照理论分析来说,当发生放电事件后,DO会置0,进而关闭MOS导通。其路径为;

IC的DO为0,MMBT5401导通,将E点电位拉到与C点电位一致(不知道我有没说反),即nDO为0,MOS的DS = 0,达到MOS关闭的结果;

但是!但是!

实际情况是,当IC的DO为0,其MMBT5401的B点电位经过电阻R30的1K走IC内部到GND,这样会造成三极管在放大区,从而造成nDO波形震荡,即MOS的GS震荡。

改进重点

此电路要在这个基础上反并一个肖特基二极管

这样就可以消除震荡的情况,得到一个较为平滑的下降沿(较平滑是因为MOS的问题,多少会有点毛刺);震荡应该是灌电流回路的R30所造成的情况。(各位大佬可以在评论区说说我说的有没问题,我理论比较差)

3.2、调节下降沿时间

电路确定后,那么就是调节关断时间的问题了;前面我也说了,一般情况下将GS的下降总时间拉到100us处基本就可以过短路,但不完全对,需要看你产品的功率;目前我是尝试过7S50A/13S20A等参数,基本都是在30us都可以过。如果VDS过还是高,一般考虑先将时间再拉长,但要考虑是否会击穿GS的情况。另一种就是加钱再堆MOS数量。

可以通过调节R50的阻值来调节下降总时间,如果你发现R50的阻值可能用的是不常用电阻值,你也可以更改GS的电阻,再进行R50的调节;

3.3、增加TVS来替MOS抗短路

一般85V的管,会用64V的TVS(64V一般雪崩击穿电压在100V左右)进行并联。由于TVS的功率会比MOS大很多,所能承受的雪崩能量也很大,但是要注意PCB走线,需要一定的宽度,不然会TVS没崩,铜箔先崩,同时会导致放电管瞬间击穿;

要注意TVS的走线宽度!!!

要注意TVS的走线宽度!!!

要注意TVS的走线宽度!!!

但是!纵使TVS的功率很大,同样也是会崩的;一旦TVS崩了,就一定是短路状态,导致整个BMS失效,甚至着火。除非TVS内部整个炸没了。

抗冲击顺序是关断前部分由MOS抗,后段最大的冲击能量由TVS抗。TVS的雪崩电压尽可能靠近MOS的雪崩电压,这样TVS冲击时间比较短,比较保险。

四、目前已知各家体二极管钳位电压点

每批次MOS的钳位电压都不太一样,请悉知!

华润微的CRSS052N08的DS钳位电压约为114V

德普微的DP052N09GN的DS钳位电压约为120V

金誉的PTY08N052的DS钳位电压约为104V

五、范例

电池:钠电池/13S/30Ah

MOS:贝岭-BLP024N10-T TOLL封装

因为要串包,所以13S用了100V的MOS

1588

1588

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?