1.基本概念

- 虚拟存储器由主存+辅存组成,二者在硬件+系统软件的管理下协调工作。

- 虚拟存储器对应用程序员是透明的。

- 虚拟存储器具有主存的速度、辅存的容量。

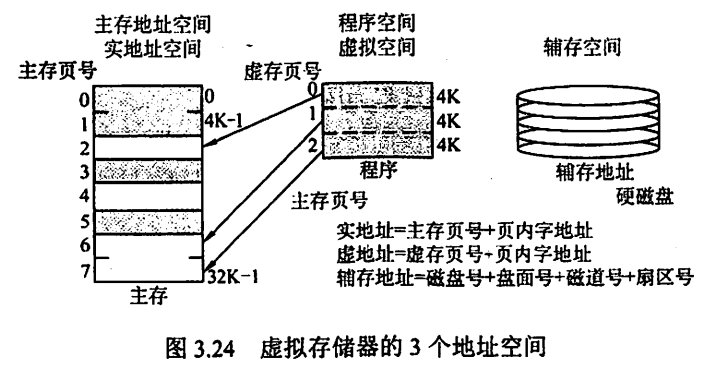

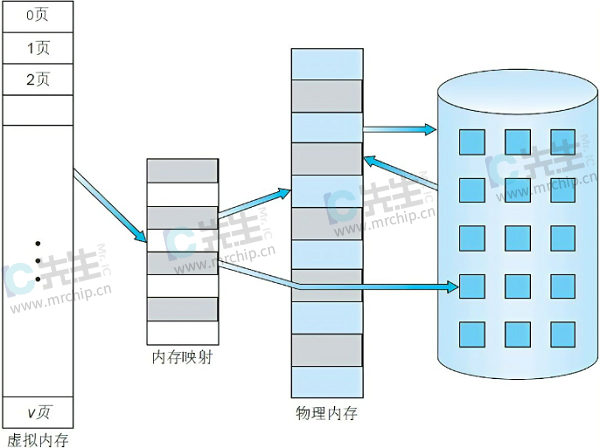

- 虚拟存储器将主存和辅存的地址空间进行统一编址,从而形成一个庞大的地址空间。用户可以在此基础上自由编程,而无需关心物理地址、主存容量等其他问题。

- 虚拟存储器同样采用与Cache类似的技术,将被经常访问到的辅存内容的副本临时存放到主存中。

- 采用全相联映射的地址映射方式,以降低主存缺页访问辅存带来的巨大开销。

- 采用回写法来处理数据一致性的问题。

- 地址映射工作由操作系统完成,当然也要辅以一些硬件的支持,如TLB、地址映射系统等。

2.名词解释

虚地址/逻辑地址

- 用户编程所允许涉及的地址,其对应的地址空间为虚拟空间或程序空间。

- 虚地址 = 虚拟页号 + 页内字地址。

实地址/物理地址

- 实际的主存单元地址,其对应的地址空间为主存地址空间或实地址空间。

- 实地址 = 主存页号 + 页内字地址。

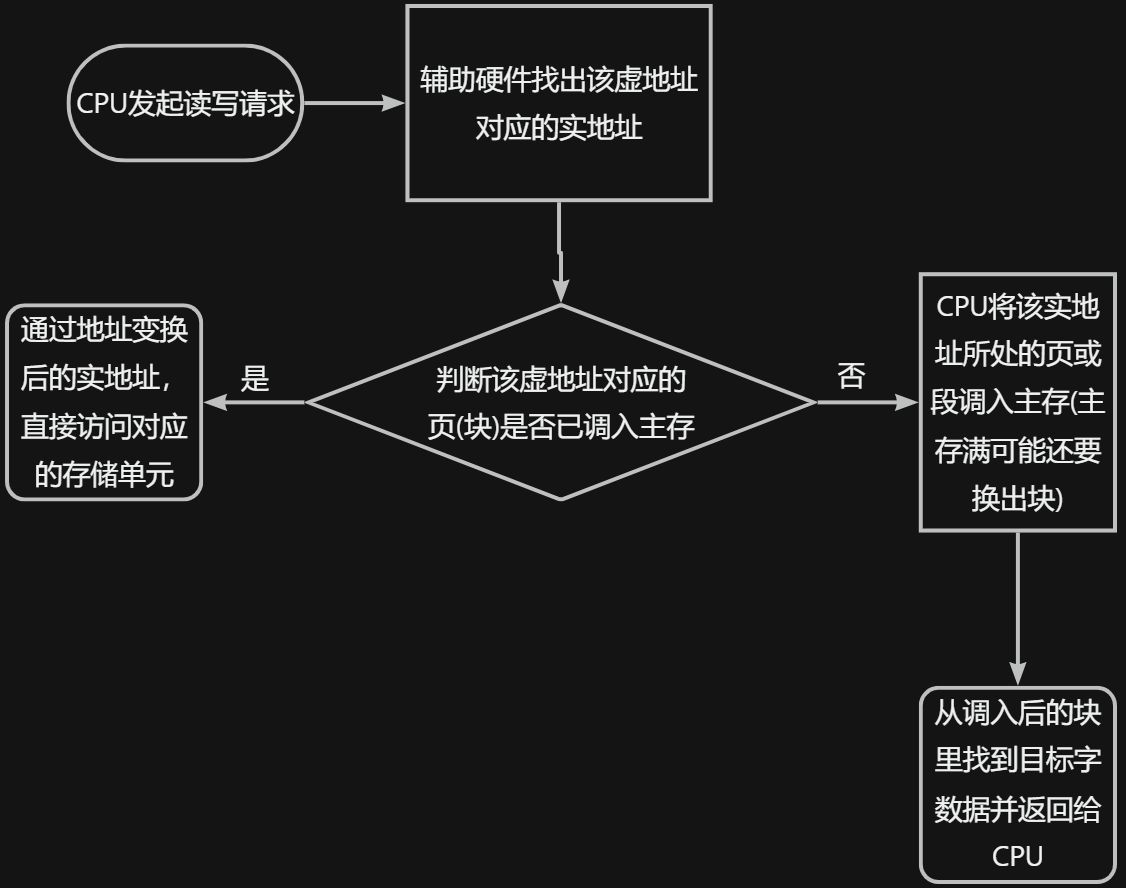

3.基本访问流程

4.分类

4.1 页式虚拟存储器

4.1.1 概述

- 页式虚拟存储器以页为操作单位,即虚拟空间与主存空间均被划分成了多个同样大小的页。

- 主存的页称为实页、页框;虚存的页称为虚页。

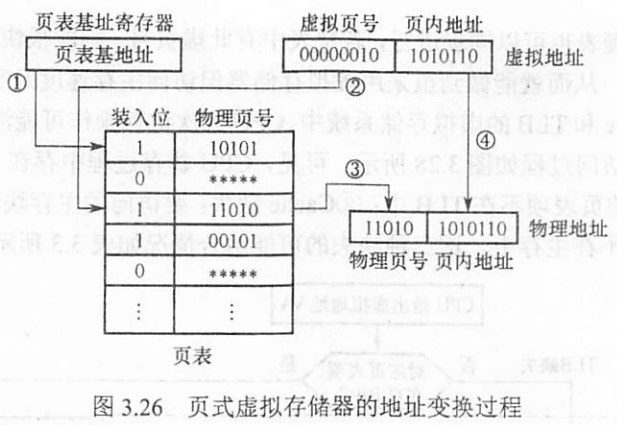

- 虚拟地址 = 虚页号 + 页内地址。

4.1.2 说明

4.1.2.1 页表/慢表

4.1.2.1.1 说明

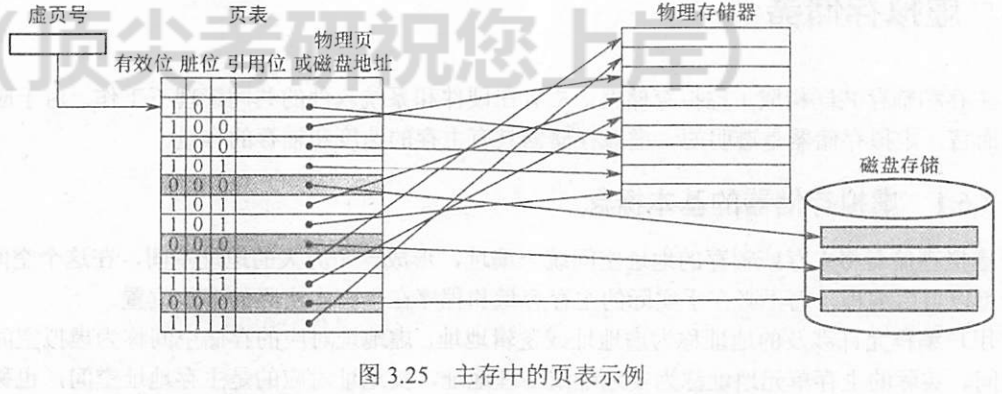

- 页表是一张存放在主存中的虚页号与实页号的对照表,一般长久驻留在主存(内存)中。

- 用于完成虚地址到实地址的转换工作。

有效位/装入位:若为1,则表示该虚拟页已由辅存调入主存;若为0,则表示该项没有被调入主存(可视为空项)。

脏位/修改位:表示页面是否被修改过(回写法的回写策略凭证)。

引用位/使用位:表示被访问了多少次,与替换策略进行配置,以便在主存满的时候换出合适的页。

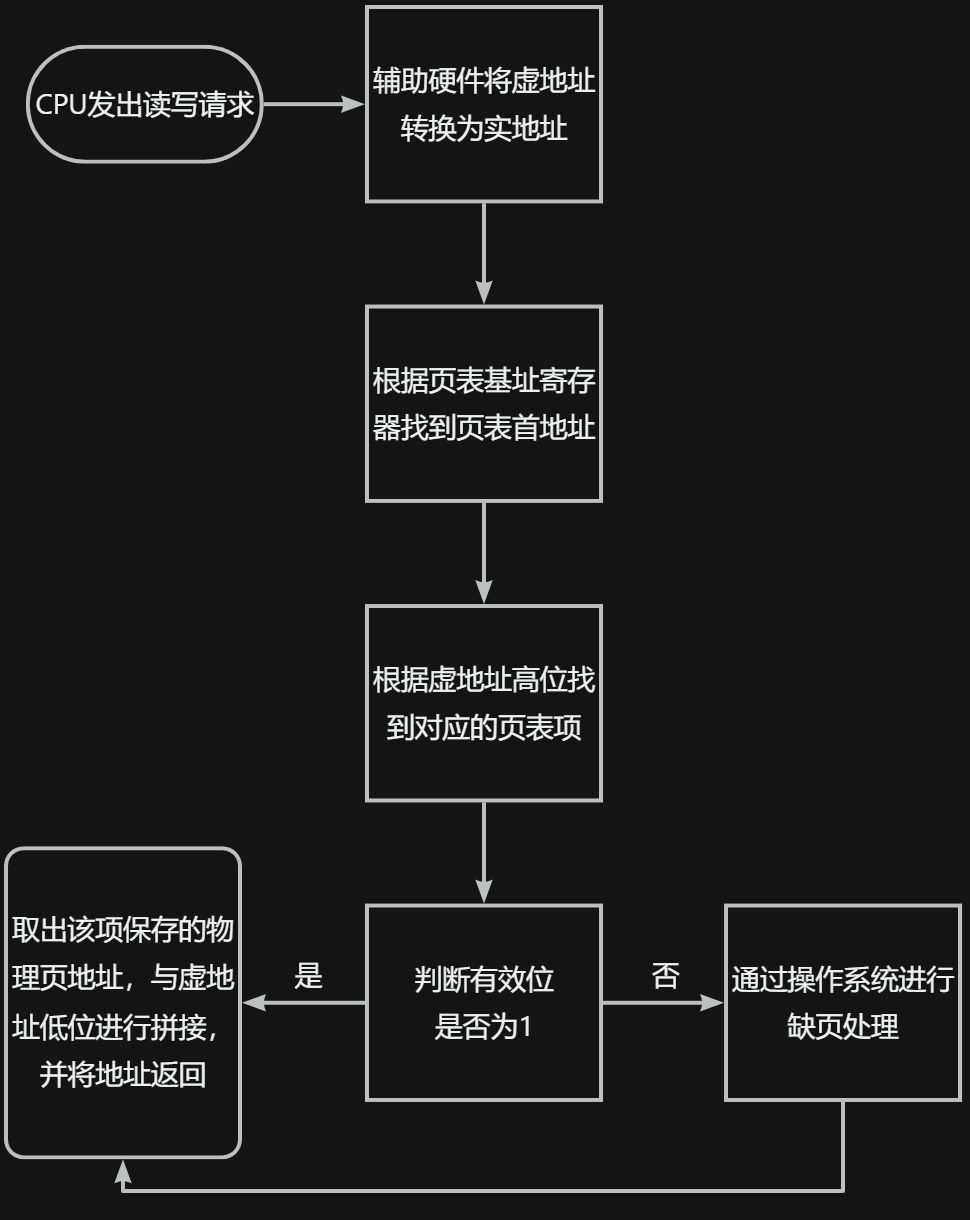

4.1.2.1.2 地址变换过程

Ps

页面若很小,则虚拟存储器中包含的页面就会过多,使得页表的体积过大,导致页表占据的存储空间过大,操作速度反而变慢。

页面若很大,则主存中存放的页面较少,导致页面调度频率较高,换页次数增加,操作速度因此降低。

4.1.2.1.3 优缺点

优点:页长度固定,页表结构简单,调入方便。

缺点:

- 程序不一样是页大小的整数倍,因此调入的最后一页可能会有冗余而浪费。

- 页不是逻辑上独立的实体,因而处理、保护、共享均不及段式虚拟存储器。

4.1.2.2 快表(TLB)

4.1.2.2.1 背景

由前面可知,在采用虚拟存储机制后,访存时会先去主存访问一次页表,然后再去访问主存才能拿到数据(如果命中,不命中的情况同样不言而喻),因此,访问的次数相较于未采用虚拟存储机制增加了。

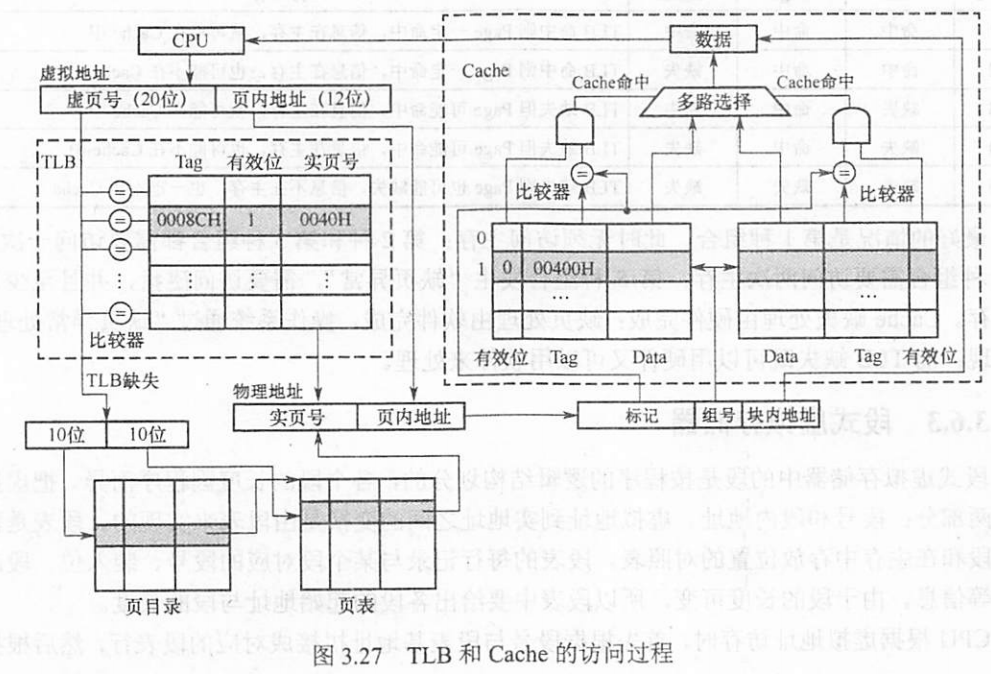

依据程序局部性原理,在一段时间内总是经常访问某些页时,如果将这些页放到Cache组成的快表中时,那访存效率会得到明显提高。

4.1.2.2.2 特点

- 快表通常采用全相联或组相联的映射方式。

- 地址转换时,首先查找快表,若命中,则无需访问主存中的页表(慢表)。

- TLB项 = TLB标记字段 + 页表表项内容。

- 快表采用高速相联存储器,其速度来源于硬件本身,而不是查找算法带来的速度上的优势。

在全相联方式的下,TLB标记就该表项对应的虚页号;在组相联的方式下,TLB则是虚页号的高位部分(低位部分用于选择TLB组的组索引)。

4.1.2.3 具有TLB和Cache的多级存储系统

在一个具有Cache和TLB的虚拟系统中,CPU的一次访存操作可能涉及TLB、页表、Cache、主存和磁盘的访问。

这期间,可能会出现下面TLB、Page、Cache组合的若干种缺失情况:

| 序号 | TLB | Page | Cache | 说明 | 访存情况 |

|---|---|---|---|---|---|

| 1 | hit | hit | hit | TLB命中则Page一定命中, | |

| 信息在主存中, | |||||

| 也在Cache中 | 无需访存主存 | ||||

| 2 | hit | hit | miss | TLB命中则Page一定命中, | |

| 信息在主存中, | |||||

| 不在Cache中 | |||||

| 访问一次主存 | |||||

| 3 | miss | hit | hit | TLB缺失但Page可能命中, | |

| 信息在主存中, | |||||

| 也在Cache中 | 访问一次主存 | ||||

| 4 | miss | hit | miss | TLB缺失但Page可能命中, | |

| 信息在主存中, | |||||

| 不在Cache中 | 访问两次主存 | ||||

| 5 | miss | miss | miss | TLB缺失则Page可能缺失, | |

| 信息不在主存中, | |||||

| 也一定不在Cache中 | 访问一次主存+访问辅存+缺页处理 |

Cache缺失由硬件完成。

缺页处理由软件完成(操作系统通过缺页异常处理程序实现)。

TLB缺失即可用硬件也可用软件来处理。

4.2 段式虚拟存储器

4.2.1 概述

- 段是按程序的逻辑结构划分的,各个段的长度长短不一。

- 虚拟地址 = 段号 + 段内地址。

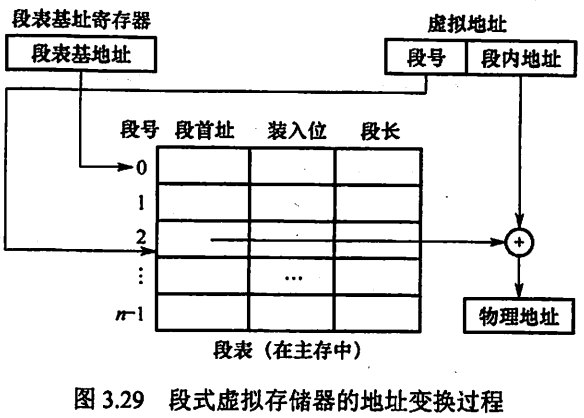

- 段表是程序中的逻辑段和在主存中的存放位置的对照表,虚地址到实地址的变换就是通过段表来实现的。

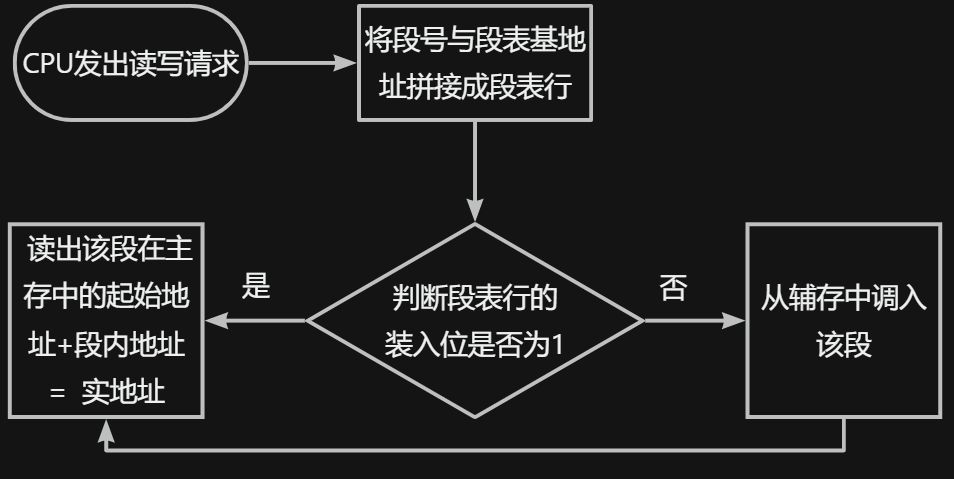

4.2.2 地址变换过程

4.2.3 优缺点

优点

- 段的分界与程序分界对应,具有逻辑独立性。

- 易于编译、管理、修改、保护,便于多道程序的共享。

缺点

段长度可变,从而使得分配空间不方便,因而容易在段间留下碎片。

4.3 段页式虚拟存储器

4.3.1 概述

- 把程序按逻辑结构分段,每段划分为固定大小的页。主存空间划分为大小固定的页。

- 程序对主存页的调入调出仍以页为单位。

- 每个程序对应一个段表,每个段对应一个页表。

- 段的长度是页的长度的整数倍,段的起点必须是某一页的整数倍。

- 虚地址 = 段号 + 段内页号 + 页内地址。

4.3.2 优缺点

优点

兼具页式和段式存储器的优点,可以按段实现共享和保护。

缺点

在地址变换过程中,需要查两次表,系统开销较大。

5.虚拟存储器与Cache的比较

5.1 共同点

| 项目 | 虚拟存储器 | Cache |

|---|---|---|

| 最终目标 | 提高系统性能,都有容量、速度、价格的梯度 | |

| 数据块 | 都把块作为基本传送单位(虚拟存储器的块更大些) | |

| 包含内容 | 都有地址映射、替换算法、更新策略等内容 | |

| 思想 | 均依据程序的局部性原理,将活跃的数据放在相对高速的部件中 |

5.2 区别

| 项目 | 虚拟存储器 | Cache |

|---|---|---|

| 解决的问题 | 解决主存容量小的问题 | 解决系统速度不匹配的问题 |

| 实现方式 | 由操作系统和硬件共同实现 | 由硬件实现 |

| 透明性 | 对系统程序员不透明,对应用程序员透明 | 对所有程序员透明 |

| 不命中后果 | 主存的速度约为辅存的速度的100倍以上,不命中时的系统性能影响更大 | CPU的速度约为Cache的10倍,不命中时对系统性能影响更小 |

| 不命中时只能先由辅存调入主存,再与CPU进行通信 | 不命中时,主存能直接和CPU进行通信 |

本文详细阐述了虚拟存储器的基本概念,包括其工作原理、虚实地址转换、页式和段式虚拟存储器的区别与优缺点,以及与Cache的比较。重点介绍了页式虚拟存储器的页表结构、TLB优化和多级存储系统中的访问流程。

本文详细阐述了虚拟存储器的基本概念,包括其工作原理、虚实地址转换、页式和段式虚拟存储器的区别与优缺点,以及与Cache的比较。重点介绍了页式虚拟存储器的页表结构、TLB优化和多级存储系统中的访问流程。

2669

2669

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?