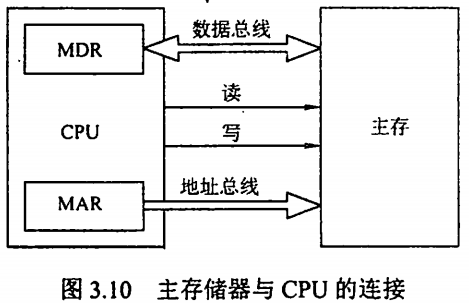

1.连接原理

- 主存储器通过数据总线、地址总线、控制总线与CPU连接。

- 数据总线的位数 × 工作频率 ∝ 数据传输率。

- 地址总线的位数决定了可寻址的最大内存空间。

- 控制总线(读/写)指明了本次总线周期的类型和输入/输出操作完成的时刻。

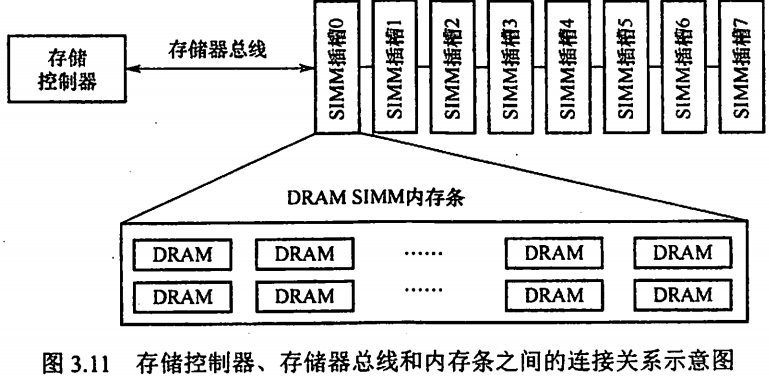

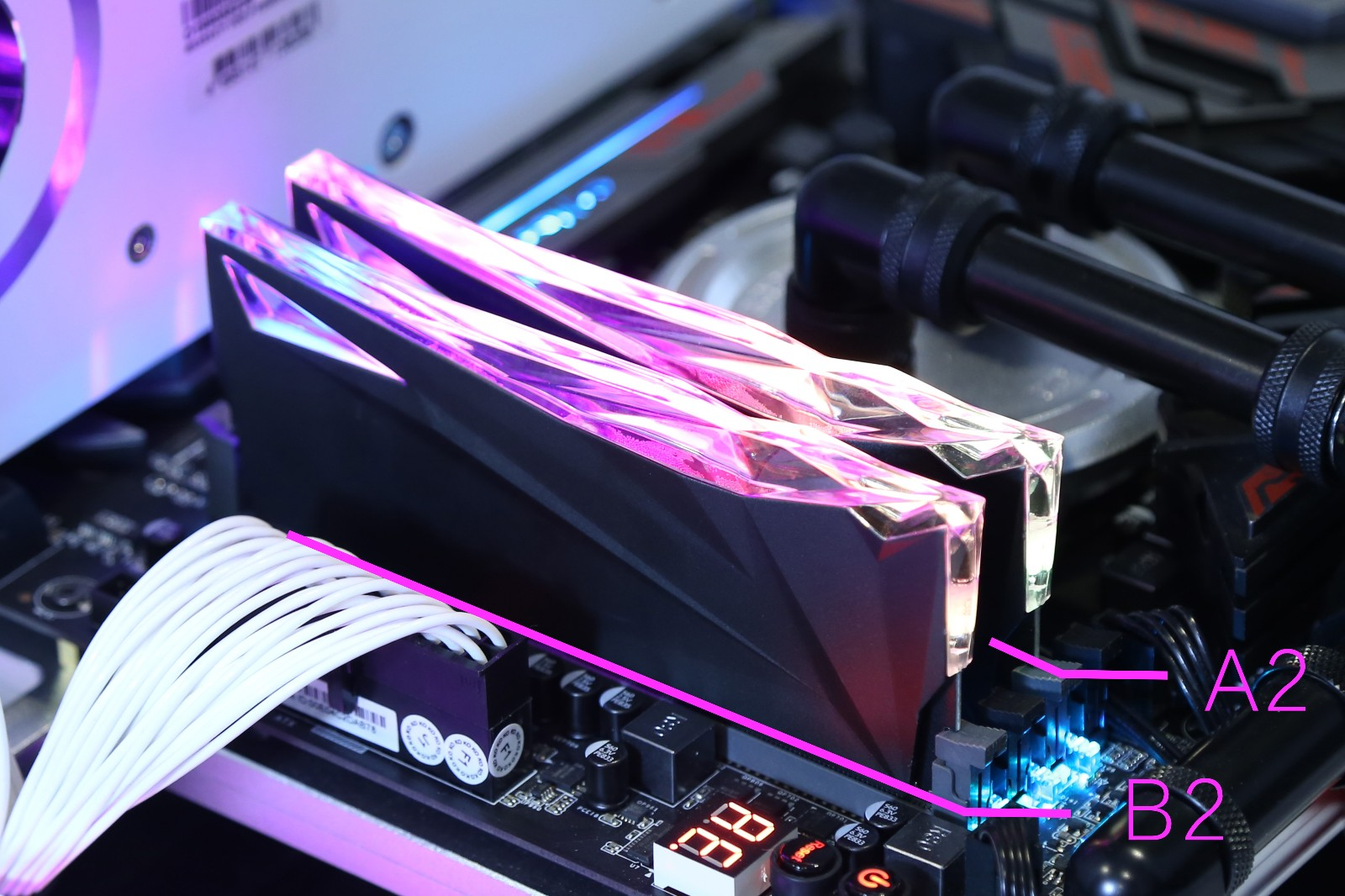

多个芯片集成到一个内存条上,多个内存条+主板上的ROM芯片 = 主存空间,然后通过总线与CPU相连。

内存条中的信息 --> 内存条的引脚 --> 内存条插槽(存储器总线)内的引线 --> 主板 --> 主板上的导线 --> CPU芯片。

2.主存容量的扩展

由于单个存储芯片容量有限,因此需要在字和位两方面进行扩充才能满足实际存储器的要求。

2.1 位扩展法

2.1.1 说明

CPU的数据总线位数与存储芯片的数据位数不一定相等,此时必须对其进行扩位(位拓展)。

用多个存储器件对字长进行扩充以增加存储字长,使其位数与CPU的数据线尾数相等。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

3778

3778

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?