NXP恩智浦电源管理芯片 PIMC VR5510 (配套S32G)芯片手册(I2C通信)-翻译版

文章目录

- NXP恩智浦电源管理芯片 PIMC VR5510 (配套S32G)芯片手册(I2C通信)-翻译版

1. 基本概述

VR5510是一款汽车多输出电源管理IC,专注于网关、车载网络、域控制器、远程信息处理和车辆到X(V2X)通信。该设备包括多个高效开关模式和线性稳压器。它提供了输入和输出的外部频率同步,以优化系统的电磁兼容性(EMC)性能。

VR5510包括增强的安全功能,具有故障安全输出。该设备覆盖了汽车安全完整性等级(ASIL)B和ASIL D安全完整性等级。它符合ISO 26262标准,并符合AEC-Q100 rev H(Grade1,MSL3)。VR5510可以充分利用面向安全的系统分区,也可以配置为非安全质量管理(QM)版本部分。

VR5510有几个版本,支持各种安全应用,并提供许多关于输出轨道数量、输出电压设置、操作频率和电源顺序的选择。

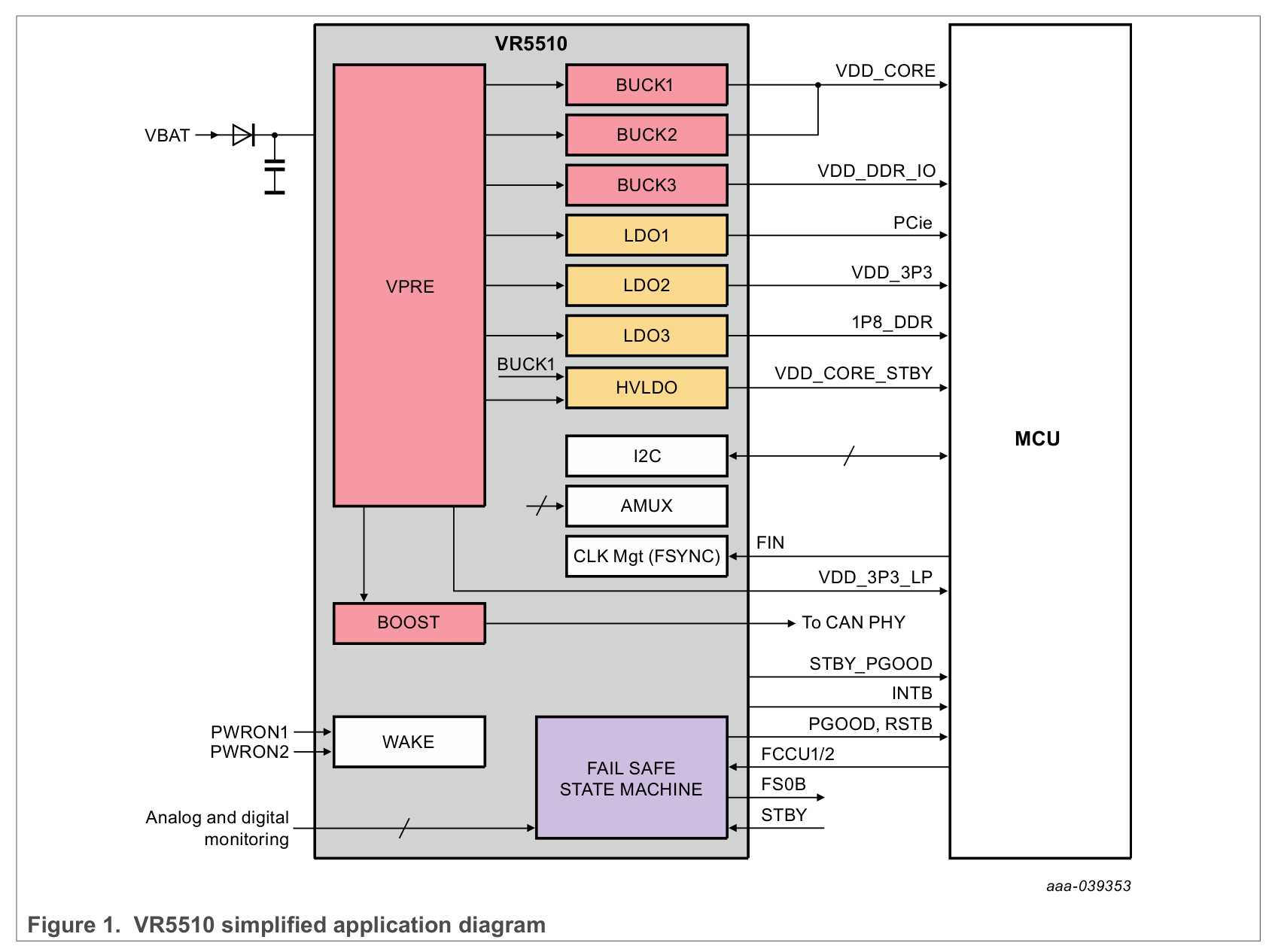

2. 简化应用视图

3. 特点

- 60 VDC最大输入电压

- VPRE同步Buck控制器,外部MOSFET;可配置的输出电压,开关频率,电流能力高达10 A

- 低压集成同步BUCK1和BUCK2转换器,专用于MCU核心电源,具有SVS/DVS功能;可配置的输出电压和电流能力高达3.6 A峰值;双相操作,扩展电流能力高达7.2 A峰值

- 低压集成同步BUCK3转换器;可配置的输出电压和电流能力高达3.6 A峰值

- BOOST转换器,集成低端开关;可配置的输出电压和输入电流能力高达2.25 A峰值

- 3x线性电压调节器(LDOx),用于MCU IO,双数据速率(DDR)和模数转换器(ADC)电源;可配置的输出电压和电流能力高达400 mA

- 高压线性稳压器(HVLDO),低压差(LDO)模式下的电流能力高达10 mA,开关模式下100 mA

- EMC优化技术,包括开关模式电源(SMPS)频率同步,扩频,摆频控制,手动频率调谐•低功耗待机模式,静态电流非常低(VPRE和HVLDO打开时为35 μA)

- 2x输入引脚用于唤醒检测和电池电压感应

- 通过I2C接口进行设备控制,具有循环冗余校验(CRC)(高达3.4 MHz)

- 通过专用同步引脚实现双设备操作

- 可扩展的组合,从QM到ASIL B到ASIL D,具有独立的监控电路,用于MCU监控的专用接口,简单和挑战者看门狗功能,电源良好,复位和中断,内置自检(BIST),故障安全输出

- 通过一次性可编程(OTP)编程进行配置;原型启用支持在工程模式下项目开发期间的自定义设置

4. 应用

-

Gateway 网关

-

In-vehicle Networks 车载网络

-

Domain controllers 域控制器

-

Telematics 汽车通信技术

-

V2X communications v2x通信

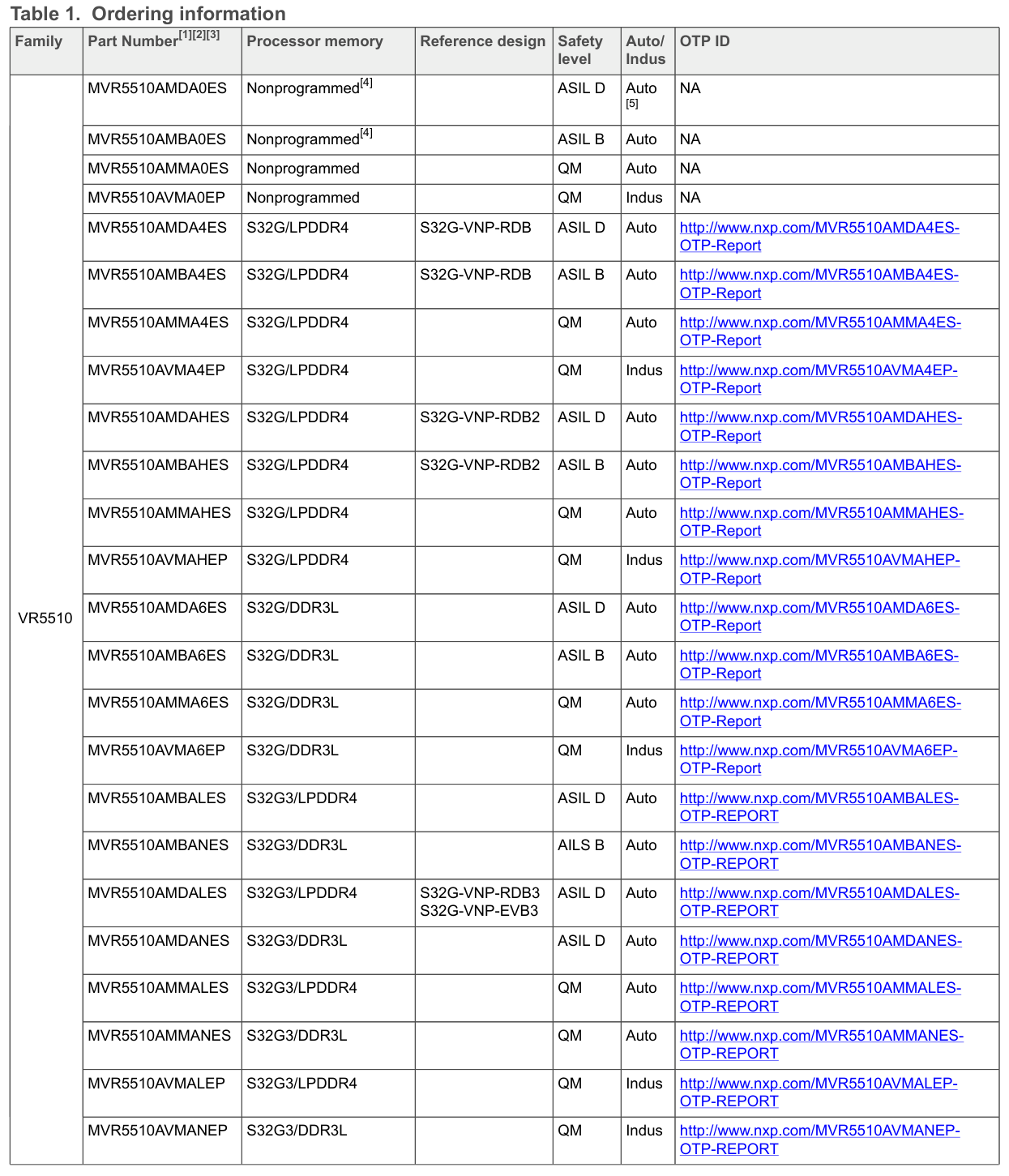

5. 订购信息

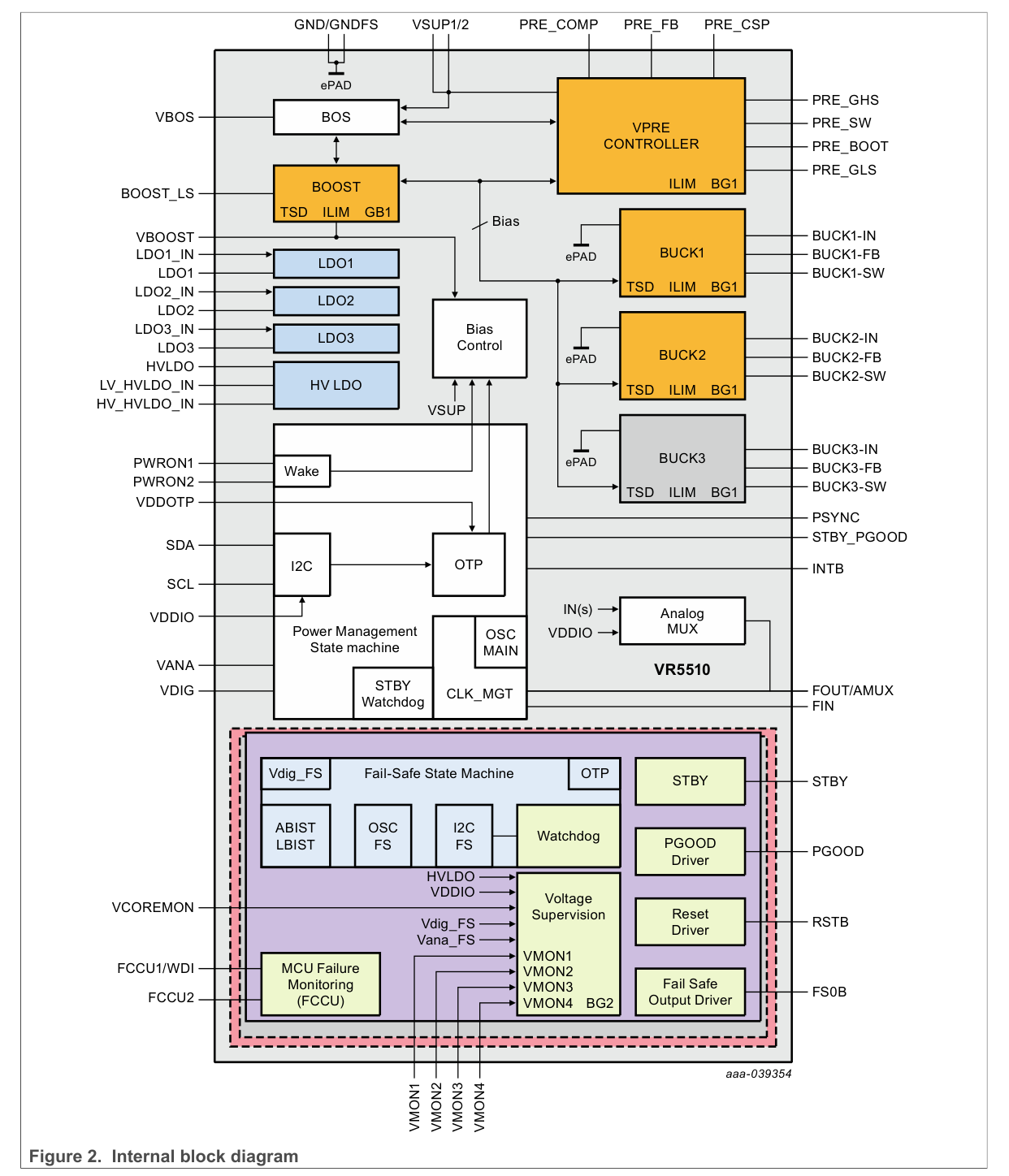

6. 芯片内部区块视图

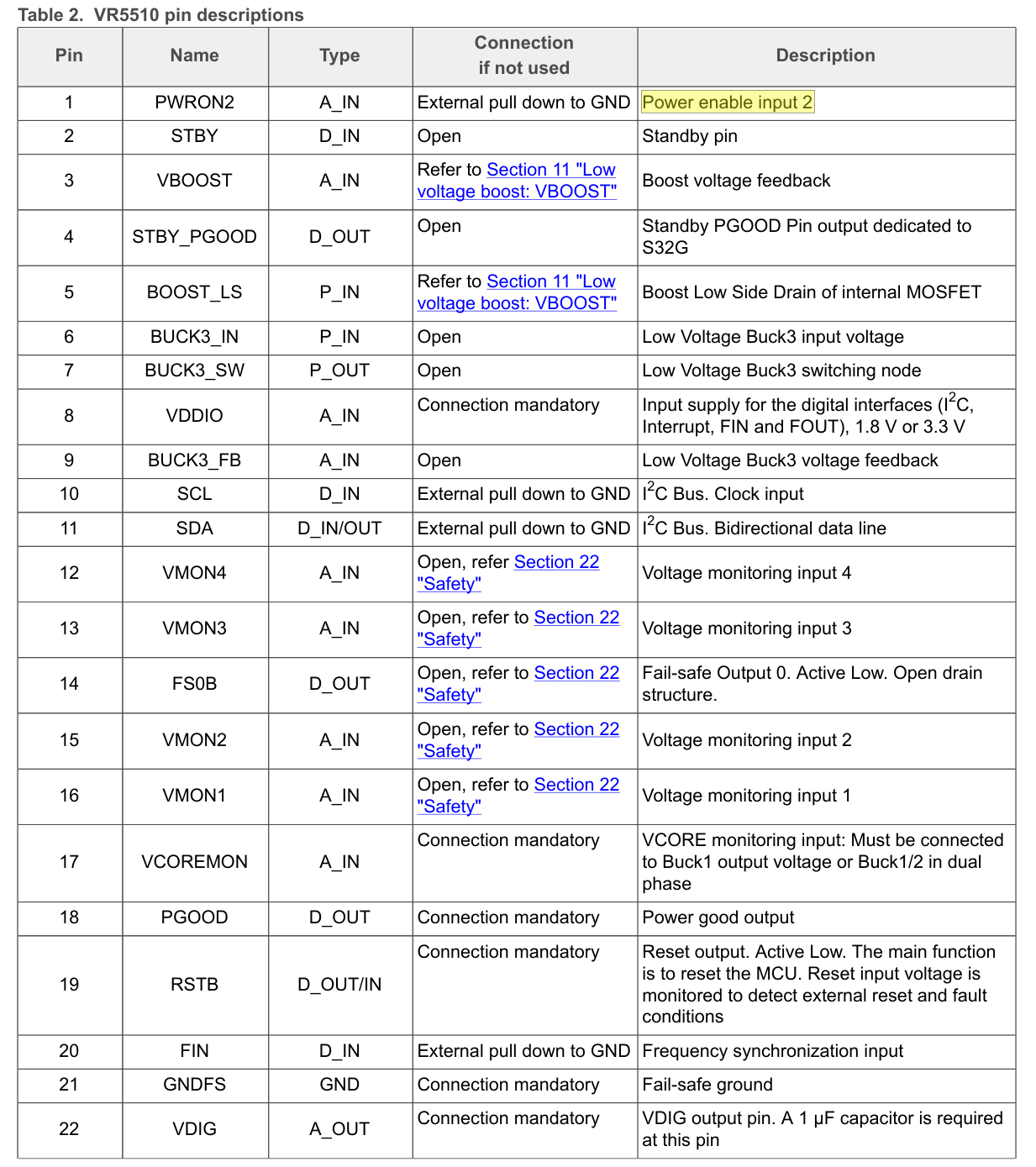

7. Pin脚信息

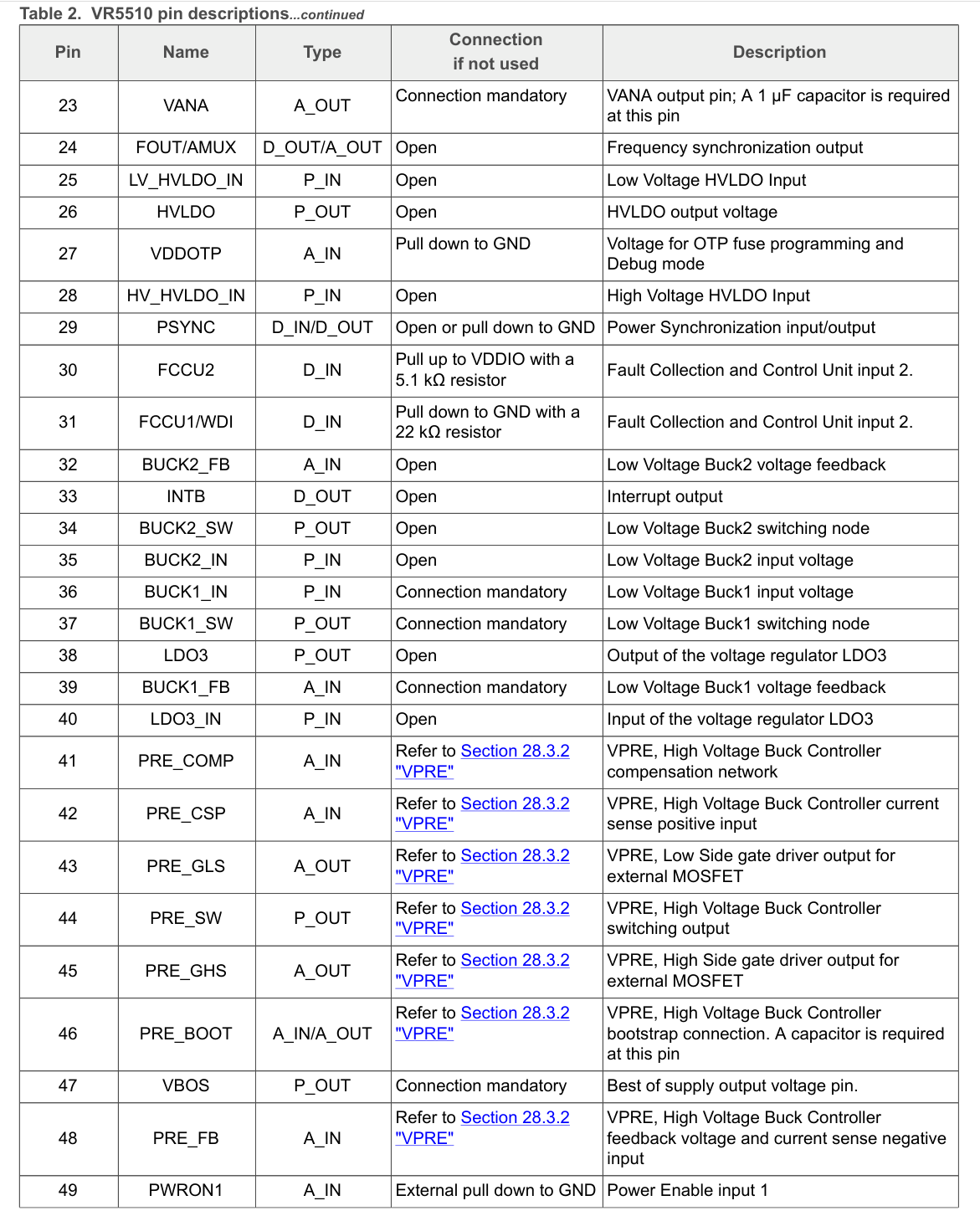

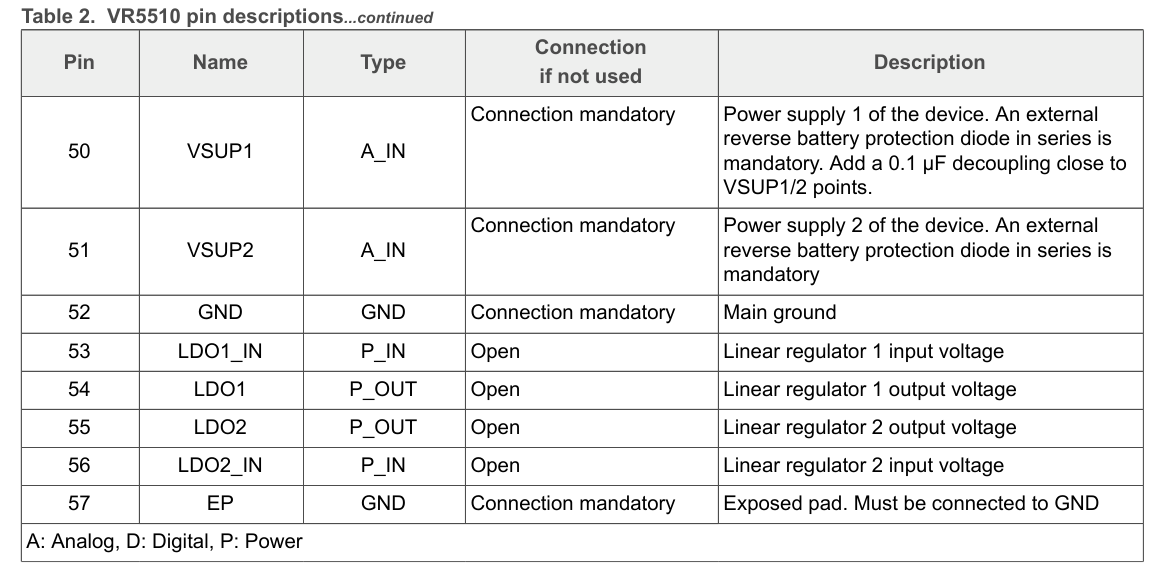

7.1 Pin 描述

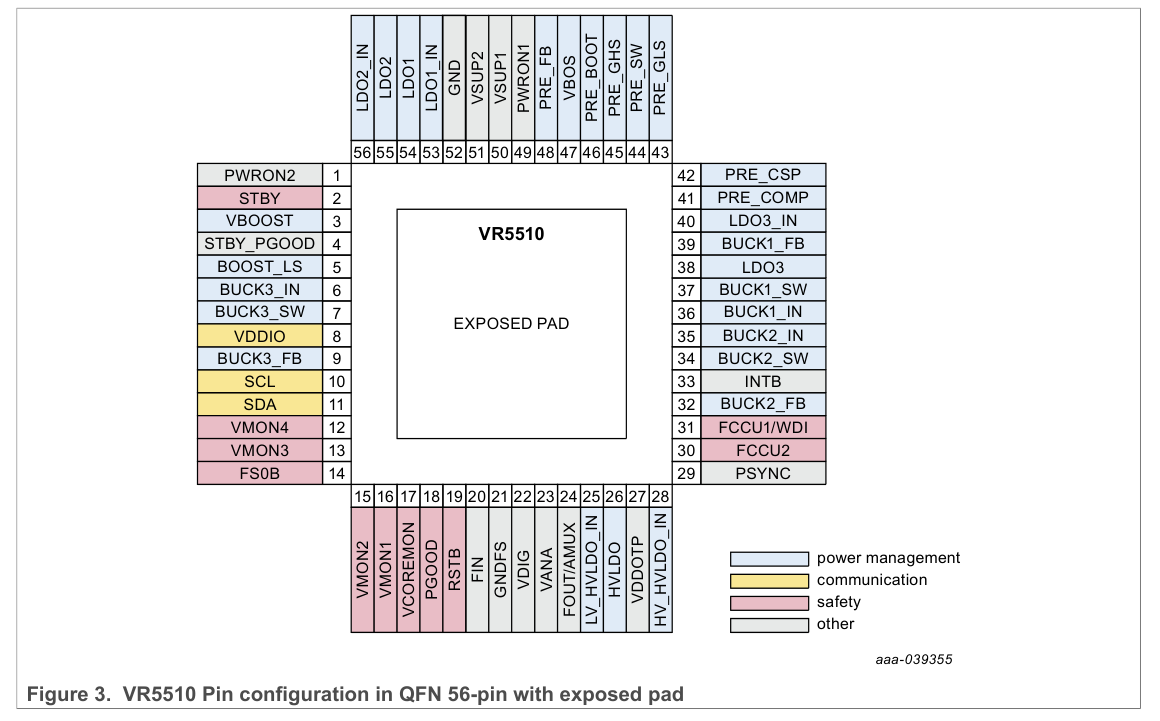

7.2 Pinning

8. 产品特性概述

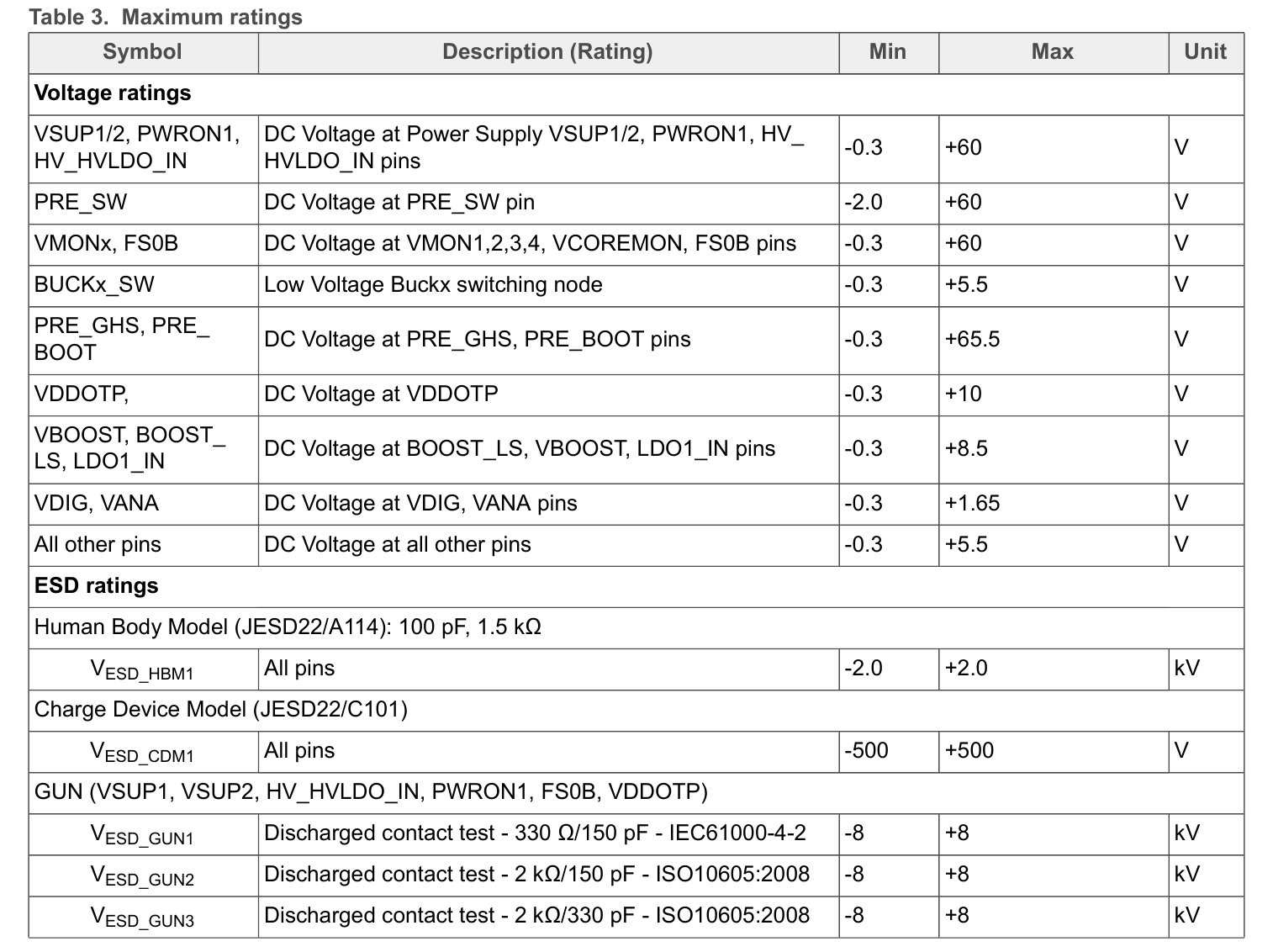

8.1 最大额定值

除非另有说明,所有电压均为对地电压。超过这些额定值可能会导致设备故障或永久性损坏。

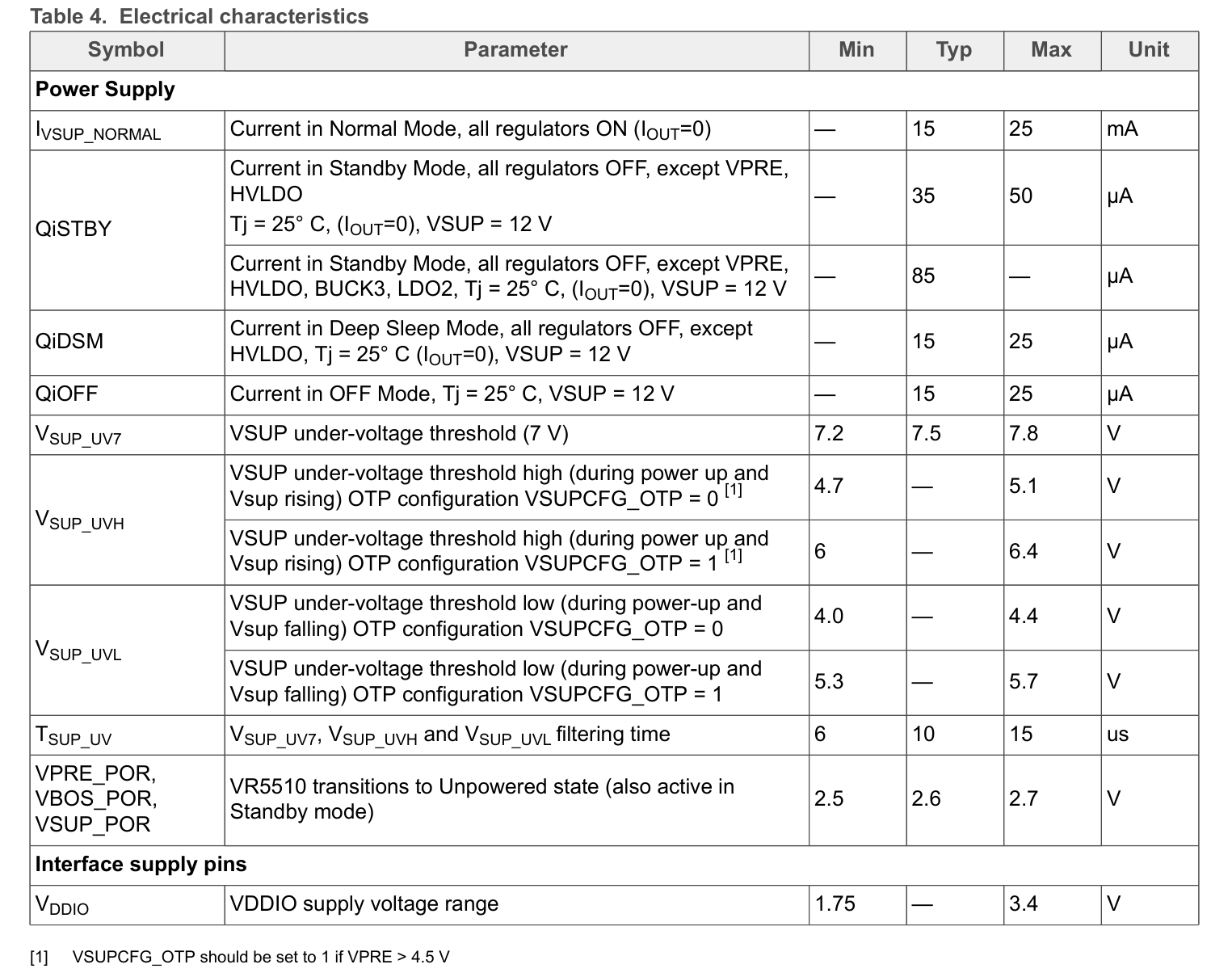

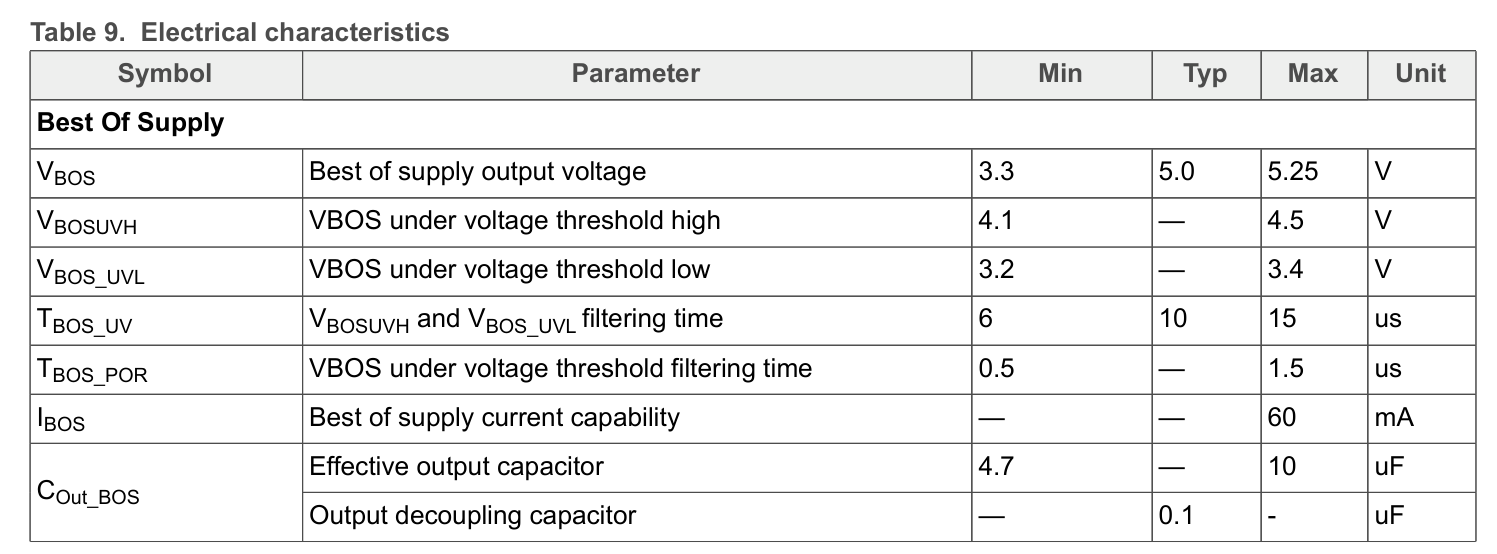

8.2 电气特性

TA = -40 °C至125 °C,除非另有规定。VSUP = VSUP_UVH至36 V,除非另有规定。所有电压均以地为基准。

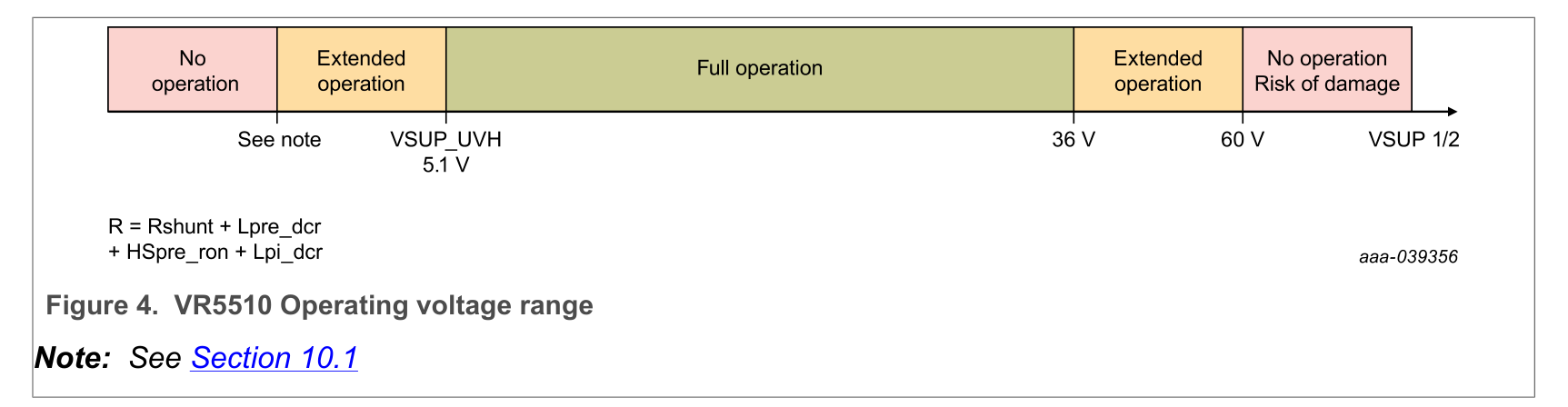

8.3 操作范围

在VSUP_UVH阈值以下,扩展操作范围取决于VPRE输出电压配置和外部组件。

- 当VPRE配置为5V时,VPRE可能不会保持在其调节范围内。

- VSUP的最低电压取决于外部元件(LPI_DCR)和应用条件(IPRE,F_VPRESW)。

当VPRE在455 kHz时切换时,VR5510的最大连续工作电压为36 V。该部件经过验证,在室温下以48 V的限定持续时间15分钟来满足24 V应用的启动要求。它可以承受58 V的负载转储而无需外部保护。

当VPRE在2.2 MHz时切换时,VR5510的最大连续工作电压为18 V。该部件经过验证,在室温下以26 V的限定持续时间2分钟来满足12 V应用的启动要求和35 V负载转储。

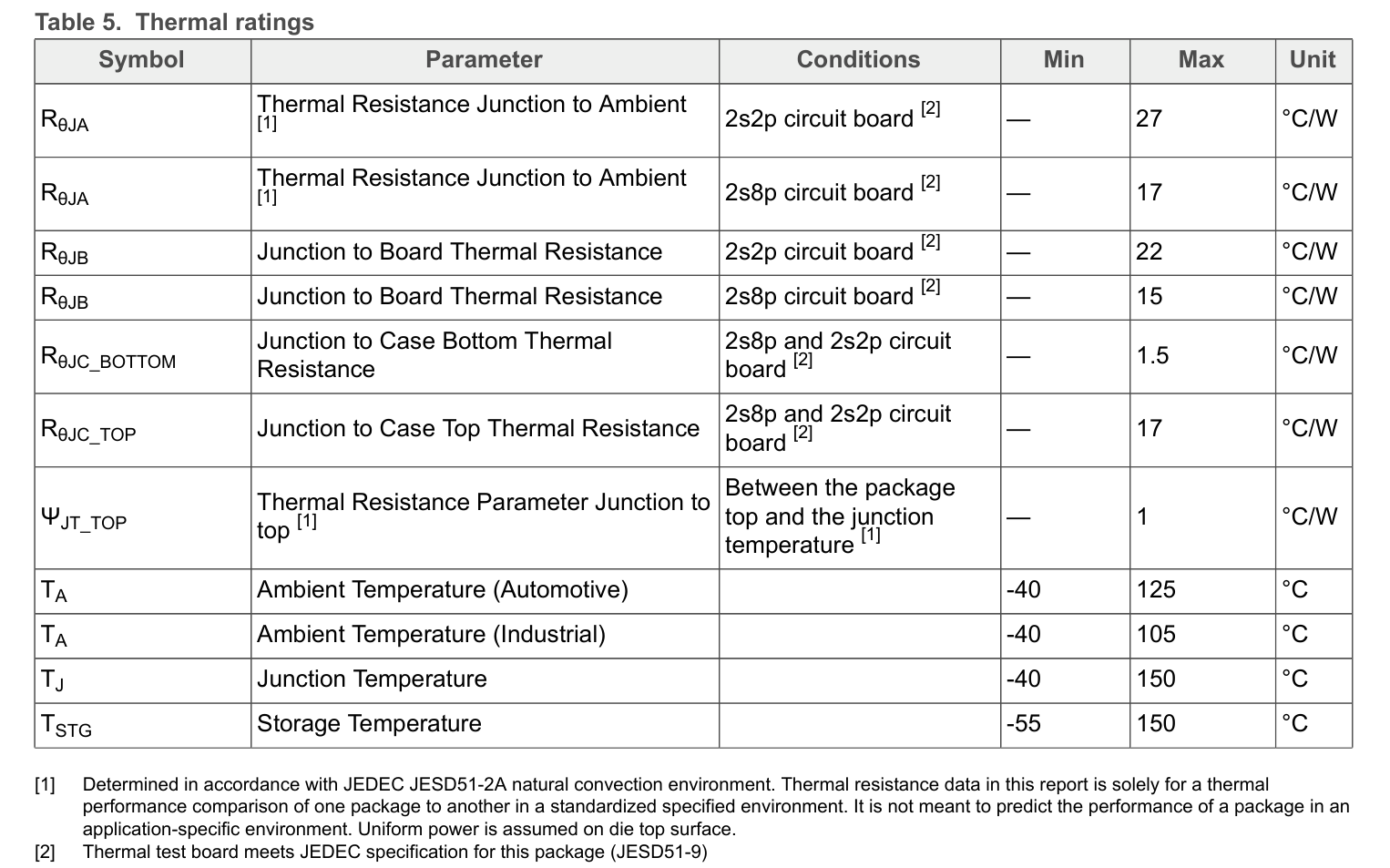

8.4 热力范围

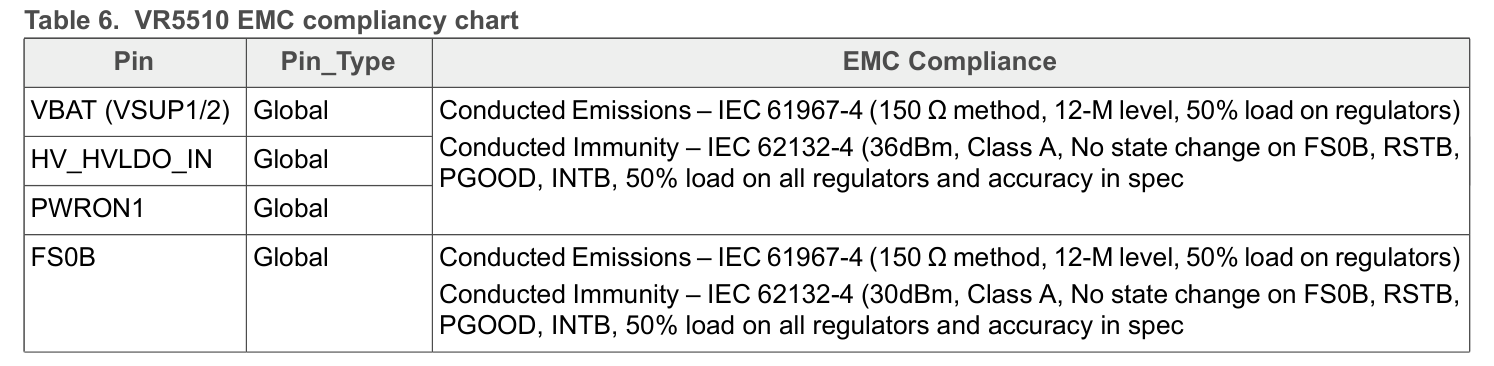

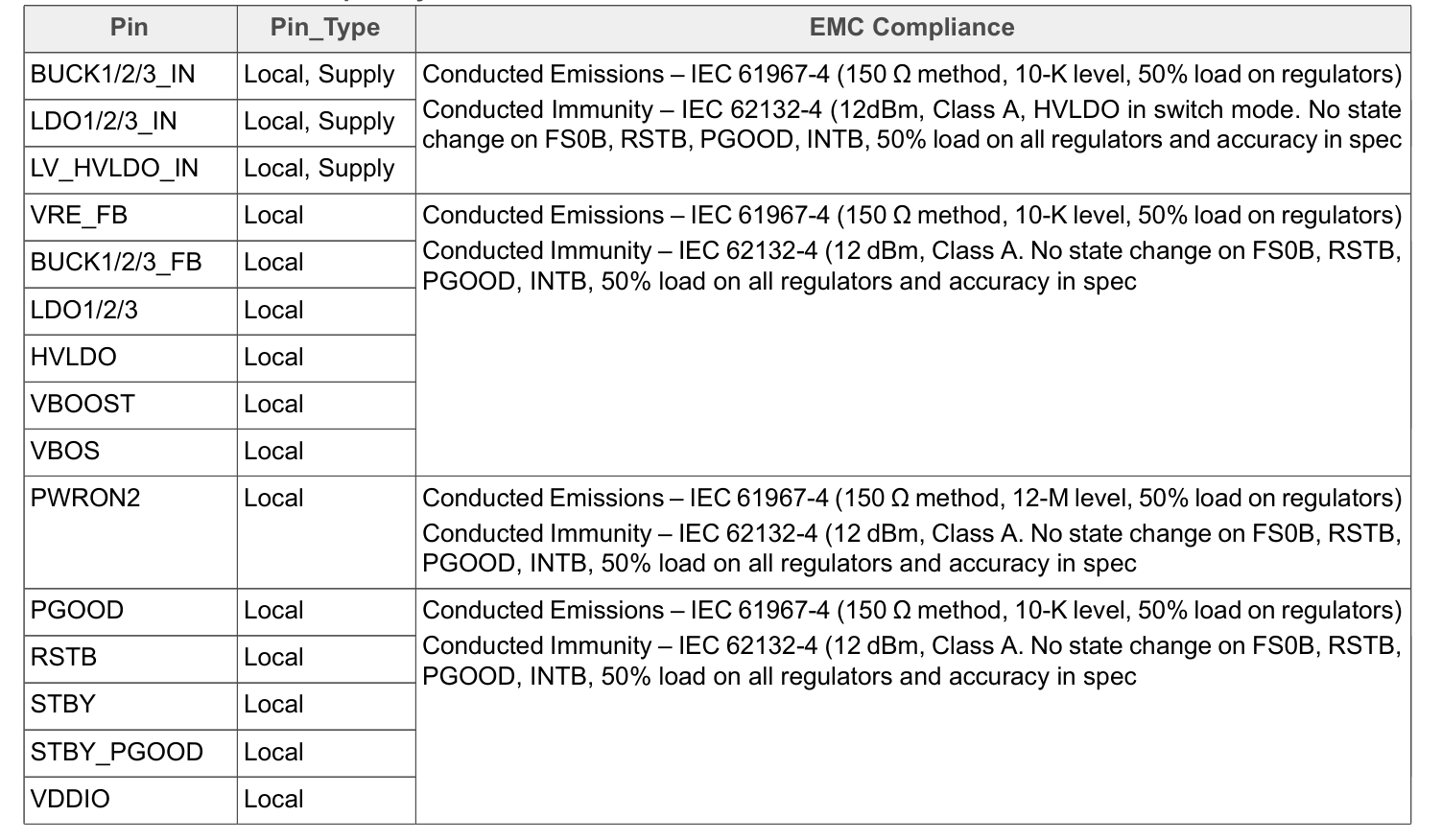

8.5 EMC合规性

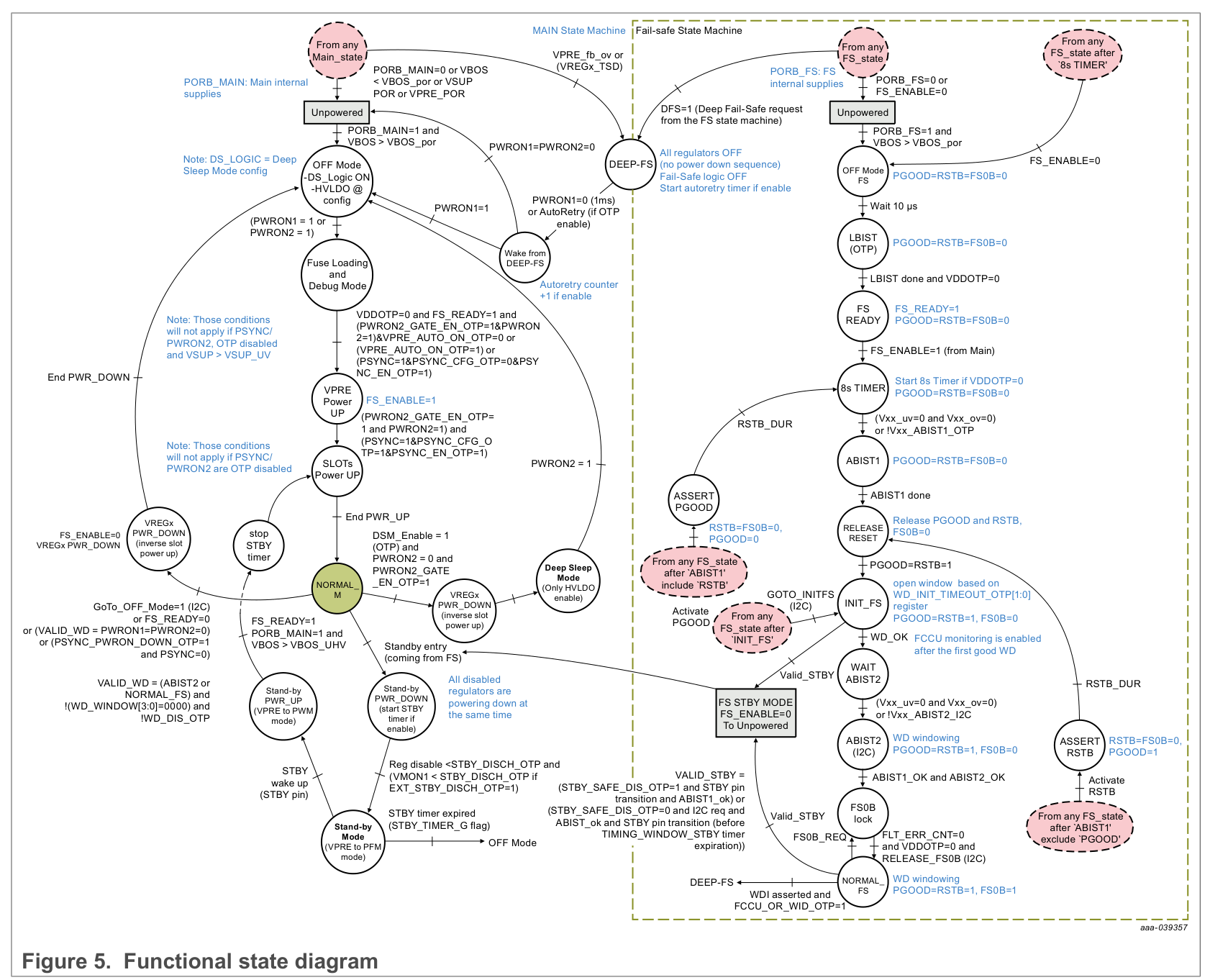

8.6 功能状态图

8.7 功能设备操作

VR5510设备具有两个独立的逻辑块。主状态机管理电源管理、待机模式、深度睡眠模式和开机源。故障安全状态机负责进入待机模式并监控电源管理和MCU。

8.8 主要状态机

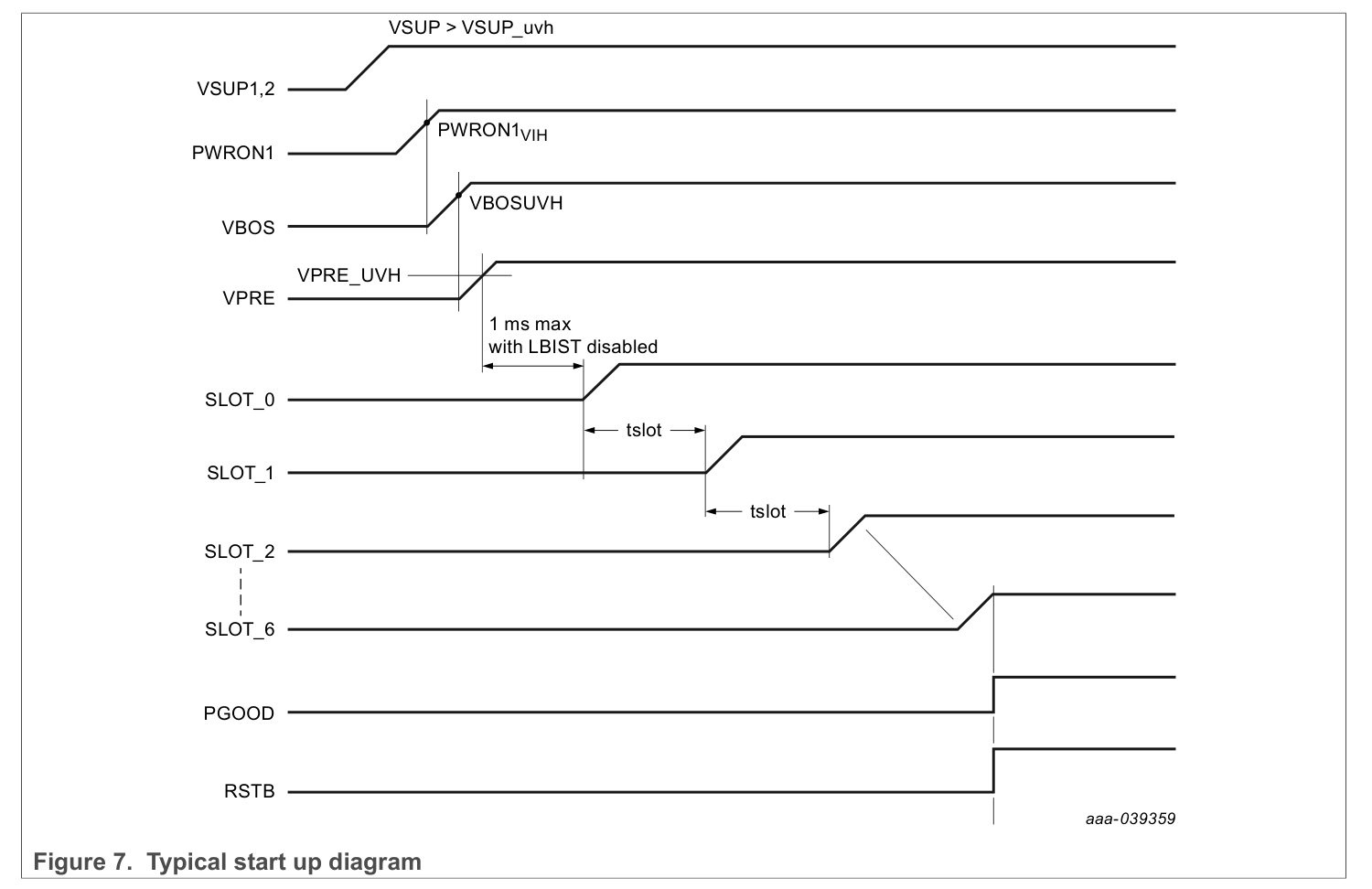

VR5510在VSUP > VSUP_UVH和PWRON1 > PWRON1VIH或PWRON2 > PWRON2VIH时启动。首先VBOS上电,然后是VPRE。 OTP编程确定了其余调节器的上电顺序。当上电顺序完成时,主状态机处于Normal_M模式,即所有调节器都处于运行模式。根据OTP配置,可以将HVLDO编程为第一个启动的调节器。

该设备可以通过切换STBY引脚或发出I2C命令并切换STBY引脚(有关详细信息,请参见第8.16节“待机模式进入”)将其置于待机模式。在验证所有禁用的调节器已经放电至小于100 mV后,该设备会进入待机模式。该设备可以通过切换PWRON2引脚(有关详细信息,请参见第8.17节“操作模式”)将其置于深度睡眠模式。该设备通过电源关闭序列达到深度睡眠状态,只保持HVLDO处于活动状态。

如果MCU从未应用或QM不存在,则可以通过MCU的I2C命令将该设备置为OFF模式,在禁用该设备时,当PWRON1和PWRON2均等于0时,它会进入OFF模式。在反向顺序停止所有调节器之前,按照下降顺序进行了电源关闭序列以使其进入OFF模式。

当VPRE提供外部PMIC时,VPRE关闭可以延迟250 us或32 ms由VPRE_OFF_DLY_OTP位(CFG_SM_ 2_OTP寄存器)等待外部装置的电源关闭序列完成而不被强制执行。

如果VSUP损失(VSUP < VSUP_POR),VPRE损失(VPRE < VPRE_POR)或VBOS损失(VBOS < VBOS_POR),则该设备停止运行、禁用HVLDO并直接进入未供电状态而不启动电源关闭序列。当VSUP > VSUP_UVH且PWRON1> PWRON1VIH或者PWRON2> PWRON2VIH时再次启动此设备。

8.9 深度故障安全状态 Deep Fail-safe State

深度故障安全状态是主状态机的一部分。如果在启用的调节器上发生VPRE_FB_OV或TSD检测,或者如果故障安全状态机发出深度故障安全请求(DFS = 1),设备将停止操作并直接进入DEEP-FS模式,而不会启动关机序列。当PWRON1引脚设置为零时,设备退出深度故障安全模式。如果OTP配置(CFG_SM_2_OTP寄存器中的AUTORETRY_EN_OTP位)激活了自动重试超时功能(CFG_CLOCK_3_OTP寄存器中的AUTORETRY_TIMEOUT_OTP位),则设备在4秒或100毫秒后退出深度故障安全模式。OTP配置可以限制自动重试次数为15次,也可以将自动重试次数设置为无限(CFG_SM_2_OTP寄存器中的AUTORETRY_INFINITE_OTP位)。当VSUP > VSUP_UVH且 PWRON1 > PWRON1VIH时,设备重新启动。

8.10 失效状态机 Fail-safe state machine

故障安全状态机在VBOS > VBOS_POR时开始执行LBIST(LBIST是OTP可编程的,可以通过禁用来加快启动过程)。当LBIST完成后,开始监视RSTB引脚的8秒定时器。当所有分配给ABIST1的调节器都通过了欠压和过压检查时,ABIST1会自动启动。当ABIST1完成后,释放RSTB和PGOOD引脚,并根据WD_INIT_TIMEOUT_OTP[1:0]位字段(CFG_2_OTP寄存器)中的可编程窗口打开设备初始化。

ABIST1失败不会阻止释放RSTB和PGOOD引脚。第一个良好的看门狗刷新关闭INIT_FS,并且设备等待I2C命令来执行ABIST2。当ABIST2成功完成后,必须使用适当数量的良好看门狗刷新来清除故障计数器以释放FS0B引脚。当FS0B引脚被释放时,设备准备进入应用运行模式,并激活所有选择的监控功能。在应用运行模式下,VR5510根据其配置,在检测到故障时断言安全引脚(PGOOD、RSTB和FS0B),详细信息请参考VR5510安全手册。

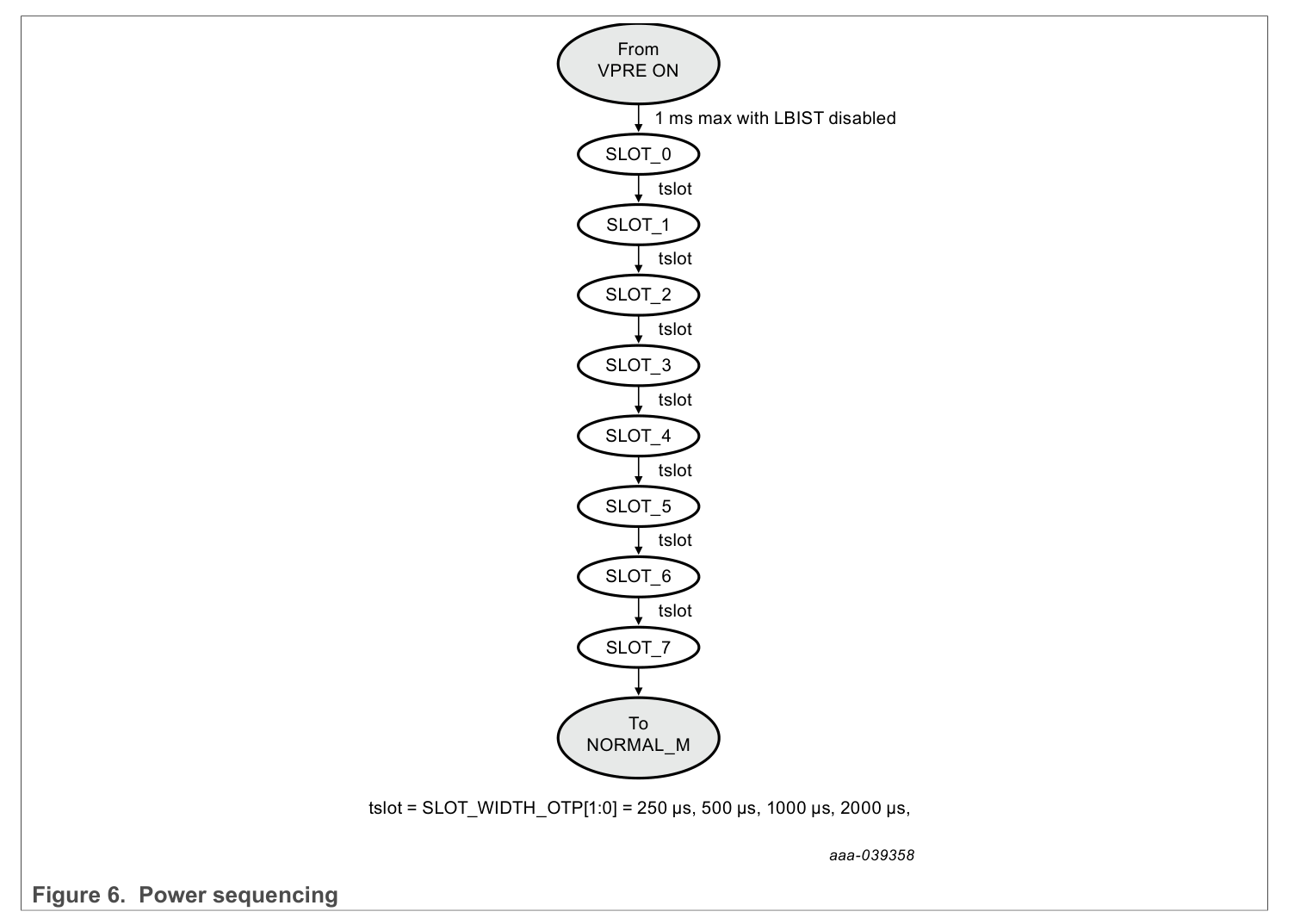

8.11 电源顺序 Power Sequencing

VPRE是第一个在SLOT_0之前自动启动的调节器。其他调节器根据OTP电源顺序配置开始启动。有七个插槽可用于编程BUCK1、BUCK2、BUCK3、BOOST、LDO1、LDO2、LDO3和HVLDO调节器的启动顺序。此外,可以使用HVLDO_SLOT_EN_OTP位(CFG_SEQ_4_OTP寄存器)来编程HVLDO在插槽中启动(或不启动)。对于需要HVLDO跟踪BUCK1的应用程序,BUCK1和HVLDO相隔一个插槽,并且先启动HVLDO,然后是BUCK1。

上电序列从SLOT_0开始,到SLOT_7结束;关机序列按相反顺序执行。如果没有使用所有七个插槽,则状态机会跳过未使用的插槽。分配给SLOT_7的调节器在上电序列期间不会被启动。它们可以稍后通过向M_REG_CTRL1/2寄存器发送I2C写命令以Normal_M模式下进行启动(或不启动)。

每个调节器都通过OTP配置分配给一个插槽,使用以下OTP位进行配置:

- BUCK1调节器使用BUCK1S_OTP [2:0]分配到一个插槽;

- BUCK2调节器使用BUCK2S_OTP [2:0]分配到一个插槽;

- BUCK3调节器使用BUCK3S_OTP [2:0]分配到一个插槽;

- LDO1调节器使用LDO1S_OTP [2:0]分配到一个插槽;

- LDO2调节器使用LDO2S_OTP [2:0]分配到一个插槽;

- LDO3调节器使用LDO3S_OTP [2:0]分配到一个插槽。

使用HVLDOS_OTP [2:0]将HVLDO调节器分配给一个插槽,使用BOOSTS_OTP [2:0]将BOOST调节器分配给一个插槽。每个插槽的宽度可以通过OTP使用SLOT_WIDTH_OTP [1:0]位字段进行配置。

- SLOT_WIDTH_OTP [1:0] = 00(默认)对应于250微秒的插槽宽度。

- SLOT_WIDTH_OTP [1:0] = 01对应于500微秒的插槽宽度。

- SLOT_WIDTH_OTP [1:0] = 10对应于1000微秒的插槽宽度。

- SLOT_WIDTH_OTP [1:0] = 11对应于2000微秒的插槽宽度。

真正的上电序列不仅取决于插槽OTP设置,还取决于每个调节器的不同软启动时间。如果启用了LBIST,则VBOSUVH到SLOT_0的时序可以高于1毫秒。LBIST典型持续时间为3毫秒。

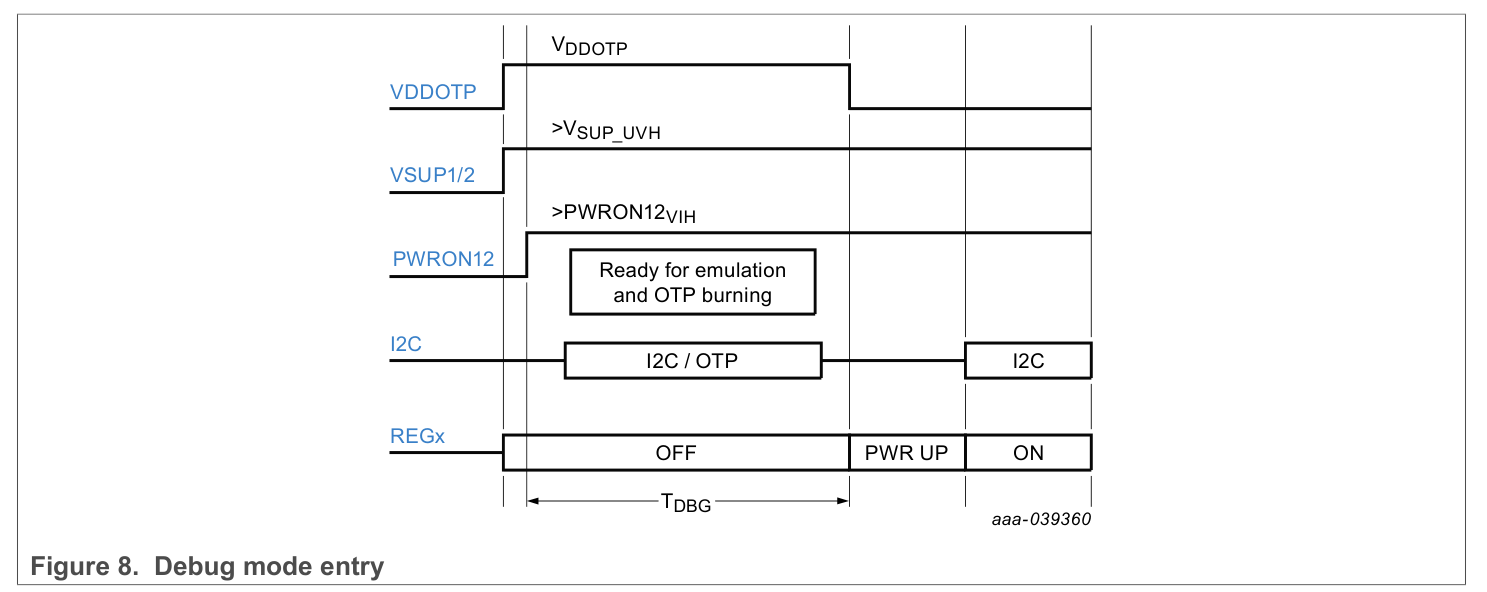

8.12 使用VDDOTP引脚进入调试模式

VR5510提供了一种在调试模式下评估设备的方法。调试模式允许用户通过I2C接口访问OTP寄存器集,修改寄存器并测试设备功能。在调试模式下,所有的稳压器都保持关闭状态。

VR5510进入调试模式的顺序如下:

- 将VDDOTP引脚接到VDDOTP电压上。

- 将VSUP1/2电压大于VSUP_UVH,并且PWRON1大于PWRON1VIH或者PWRON2大于PWRON2VIH。

- 设备现在进入调试模式,准备进行调试或OTP编程。

- 施加0 V的VDDOTP来打开具有修改配置的设备。

如果将VDBG电压保持在VDDOTP引脚上,可以通过I2C通信使用NXP GUI界面和NXP插座EVB来模拟或编程新的OTP配置。当OTP过程完成时,当VDDOTP引脚被断开低电平时,设备将以新的OTP配置启动。 OTP仿真/编程仅在工程开发期间可行。生产中的OTP编程由NXP完成。

在调试模式下,看门狗窗口完全打开,故障安全状态机(DFS = 1)的深度故障安全请求被屏蔽,监视RSTB引脚的8秒定时器被禁用,并且无法释放故障安全输出引脚FS0B。设备处于调试模式时无法进入待机模式。

在调试模式下,主数字访问的I2C地址固定为0x20,故障安全数字访问的I2C地址为0x21。

在调试模式下,不需要刷新看门狗以便于调试硬件和软件例程(即I2C命令)。然而,看门狗功能保持开启(种子、LFSR、WD刷新计数器、WD错误计数器)。WD错误被检测并计数,并通过RSTB引脚进行响应。

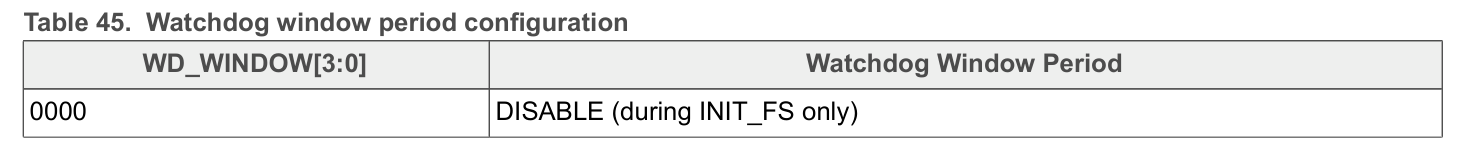

要释放FS0B而不考虑看门狗窗口,请在离开调试模式之前,在FS_WD_WINDOW寄存器中将WD_WINDOW [3:0] = 0000禁用看门狗窗口。要退出调试模式,请在FS_STATES寄存器中写入DBG_EXIT位=1。

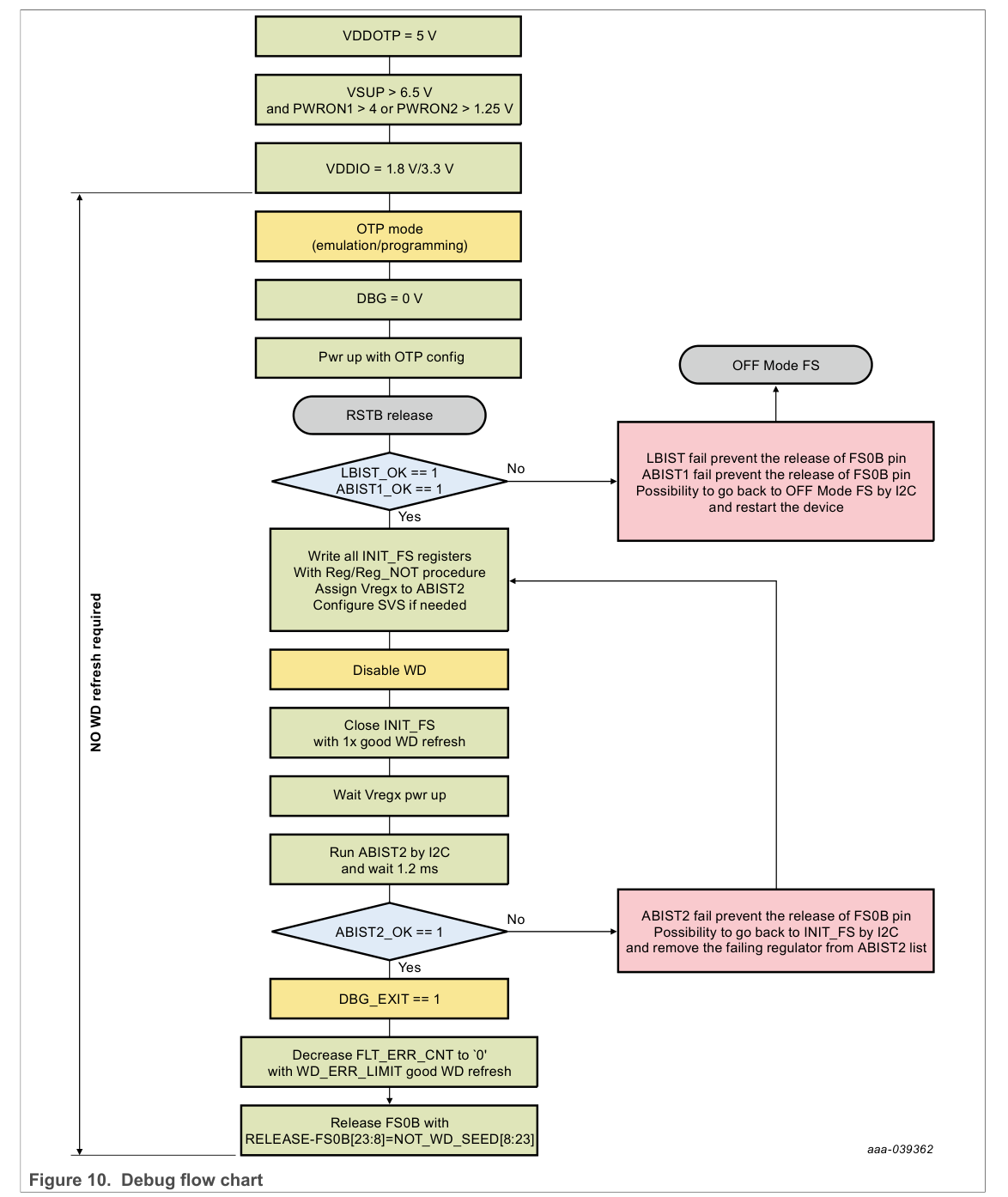

TA = -40°C至125°C,除非另有规定。VSUP = VSUP_UVH至36 V,除非另有规定。所有电压均参考地面。

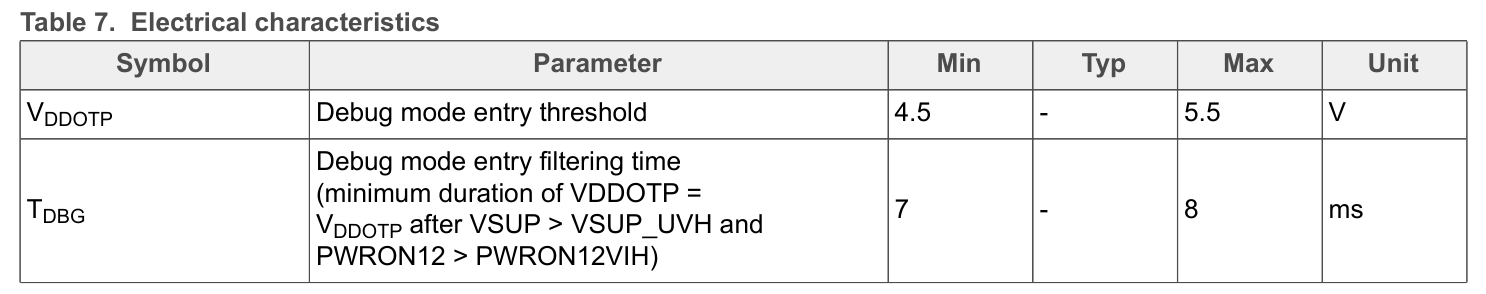

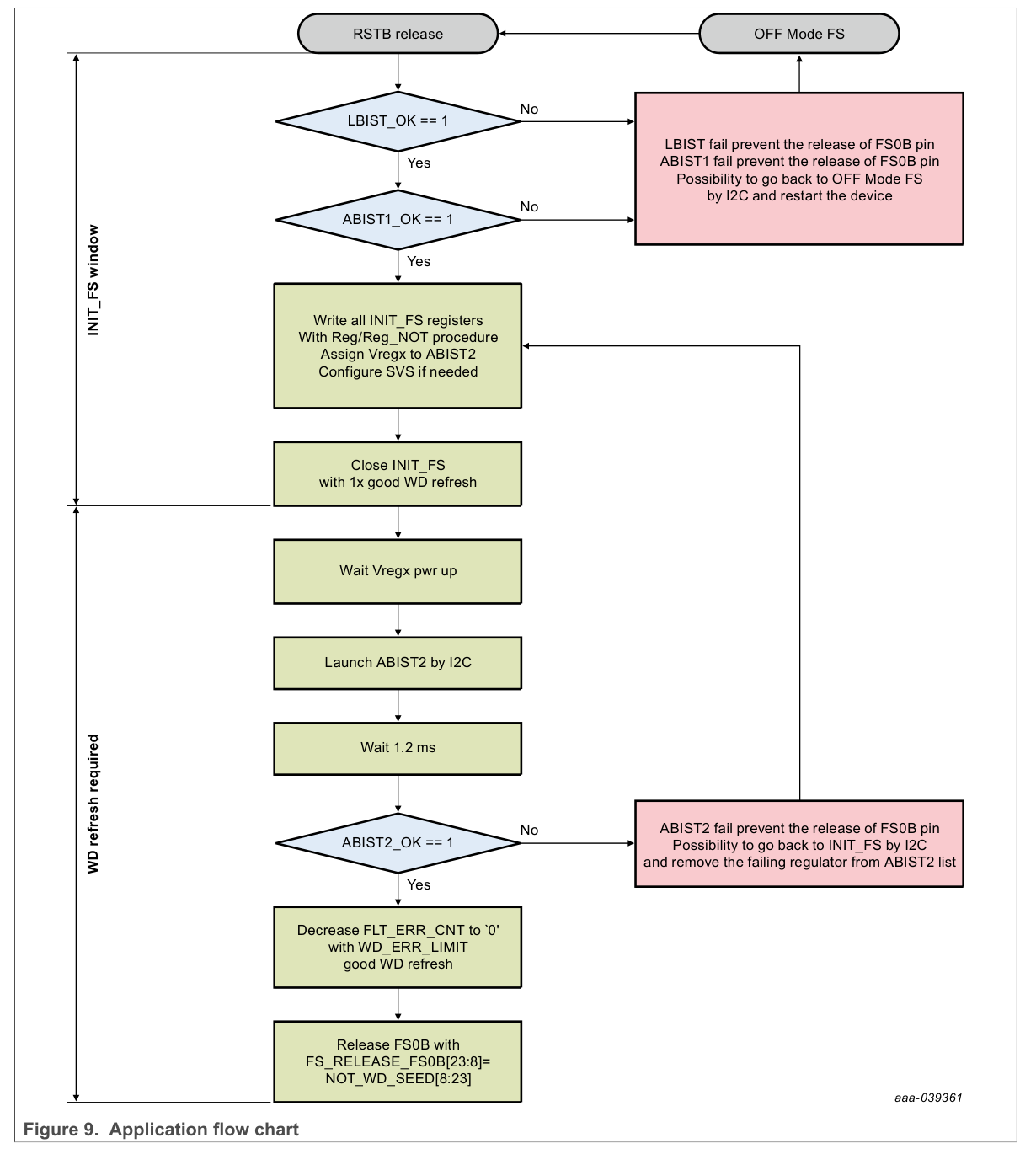

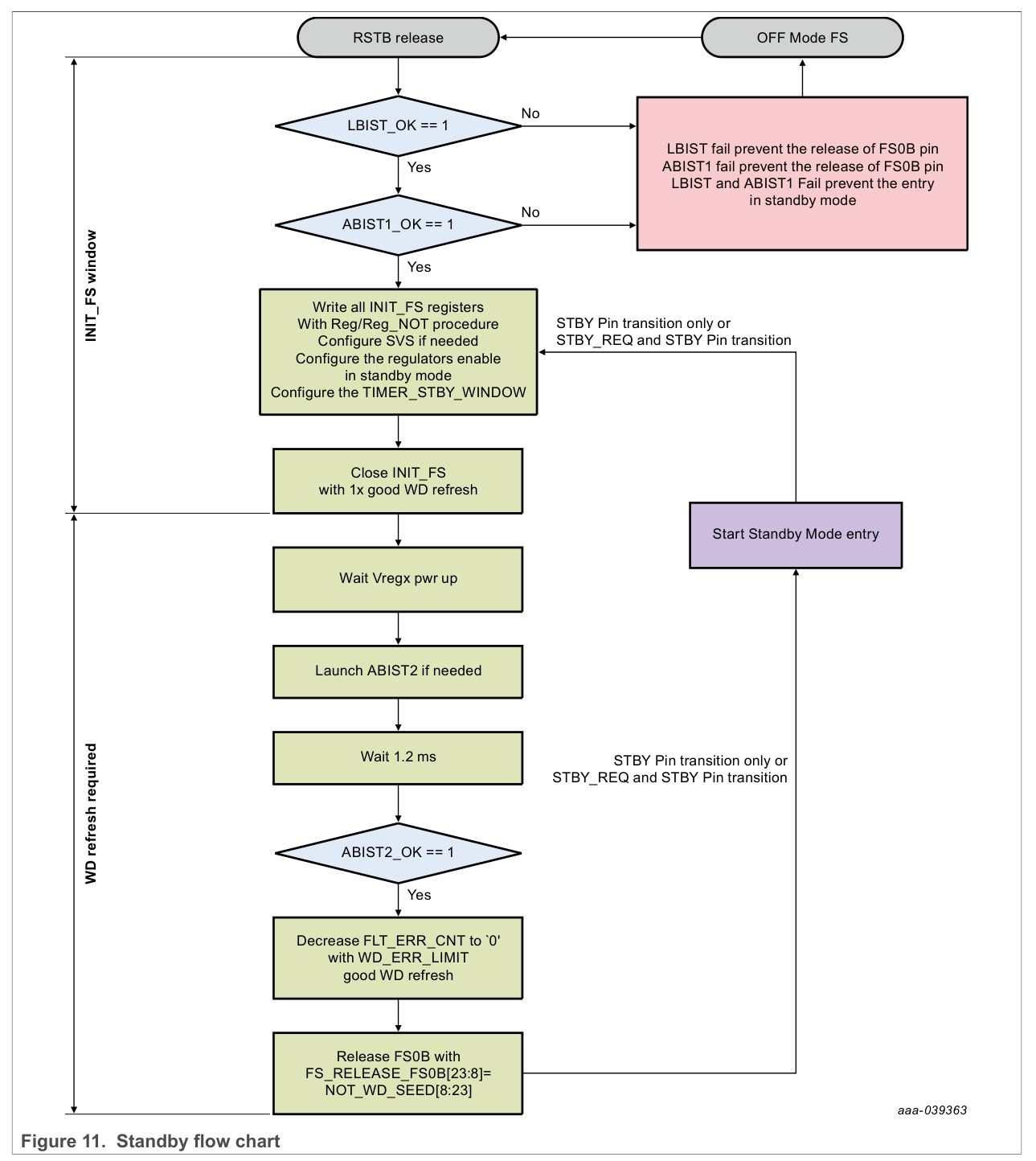

8.13 流程图

以下流程图描述了设备的启动方式,进入待机模式的方法以及在释放RSTB引脚时应该做什么。

8.14 应用流程图

在应用模式下,VDDOTP引脚连接到GND,并且一旦INIT_FS关闭,就需要进行看门狗刷新。

8.15 Debug流程图

在调试模式下,VDDOTP引脚的管理方式如第8.12节“使用VDDOTP引脚进入调试模式”所述。看门狗窗口完全打开,不需要进行看门狗刷新。

8.16 进入待机模式 Standby mode Entry

8.17 模式运行

根据应用的不同,VR5510可以有几种工作模式:关闭模式、深度睡眠模式、待机模式和正常模式。

-

关闭模式:

关闭模式是设备的初始状态,其中所有调节器都处于关闭状态。

-

深度睡眠模式:

深度睡眠模式会关闭除LDO(低压差线性稳压器)模块中的HVLDO之外的所有VR5510调节器。在深度睡眠模式下,PWRON2输入检测器处于活动状态,并可触发开启事件。

DSM_EN_OTP位(DSM_EN_OTP寄存器)用于启用或禁用深度睡眠(DSM)工作模式。

-

待机模式:

待机模式是一种低功耗模式,当设备需要进入最小供电电流模式时,同时保持最小预设输出电压。在正确编程条件下,通过切换STBY引脚并使用STBY_EN_OTP位(CFG_VPRE_2_OTP寄存器)和STBY_WINDOW_EN_OTP位(CFG_2_OTP寄存器),可以进入待机模式。

在低功耗待机模式下开启的主要调节器是VPRE和HVLDO。VPRE被强制以PFM模式运行,而HVLDO则以LDO模式运行。还可以选择操作其他调节器(除BOOST之外),但此时开关只能强制以PFM工作。

BUCKx_STBY_EN位用于启用或禁用待机模式中的Buck调节器。

LDOx_STBY位用于启用或禁用待机模式中的LDOs.

HVLDO_STBY位用于启动或停止Standby mode 中 LDOs 的功能.

更多有关Standby mode示例和详细信息,请参阅AN12880文档

-

正常模式:

在正常模式下,设备根据预先设置的参数开启调节器进行操作。设备将保持在正常模式直到处理器请求转换为待机模式或深度睡眠模式。当检测到内部故障或处理器指示外部故障时,设备将退出正常模式并进入关闭模式或深度安全失败模式。

9. 最好的供电

9.1 功能描述

VBOS调节器管理来自VSUP、VPRE或VBOOST的最佳供电,以有效地为设备的内部偏置提供5.0 V的输出。VBOS还为VPRE高侧和低侧门驱动器以及VBOOST低侧门驱动器提供电源。

如果VBOS欠压,可能导致设备无法完全正常工作。因此,当检测到VBOS欠压时会关闭设备。在VSUP < VSUP_UV7时,使用VSUP_UV7欠压阈值启用从VSUP到VBOS的路径。

这在VRPE变低且VPRE未启动时为VSUP提供了一个低降压路径,并且在设备上电时起作用。当VSUP > VSUP_UV7时,强制VBOS使用VPRE或VBOOST中的一个来优化效率。

9.2 电力特性

除非另有规定,否则TA的范围为-40°C至125°C。除非另有规定,VSUP的范围为VSUP_UVH至36V。所有电压均以地面为参考。

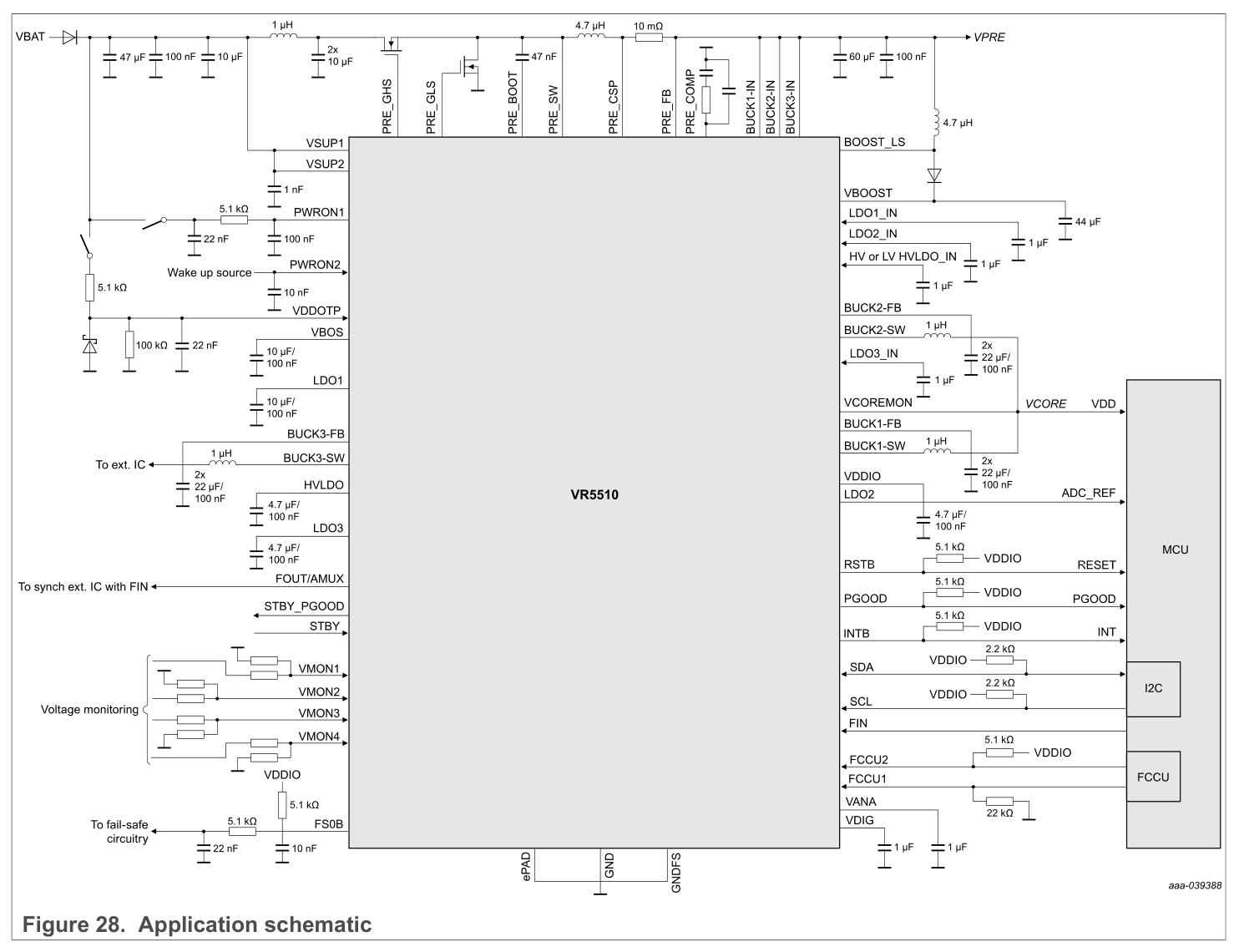

21. 应用原理图

请参考VR5510设备指南,了解原理图的更多细节。

22. 安全性

22.1 功能描述

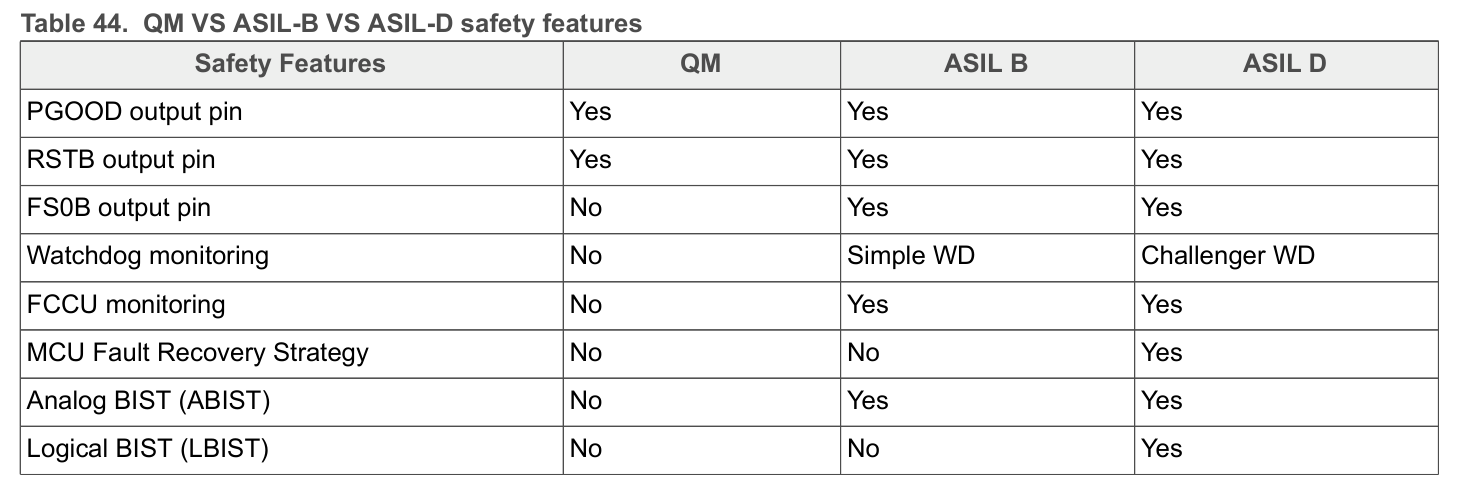

故障安全域是电气独立且物理隔离的。故障安全域由自己的参考电压和电流供应,具有自己的振荡器,采用重复模拟路径以最小化共同失效,同时具备LBIST/ABIST来覆盖潜在故障。根据设备型号不同,故障安全域提供QM、ASIL B或ASILD合规性。除非另有说明,否则故障安全定时来自于±10%精度的故障安全振荡器。

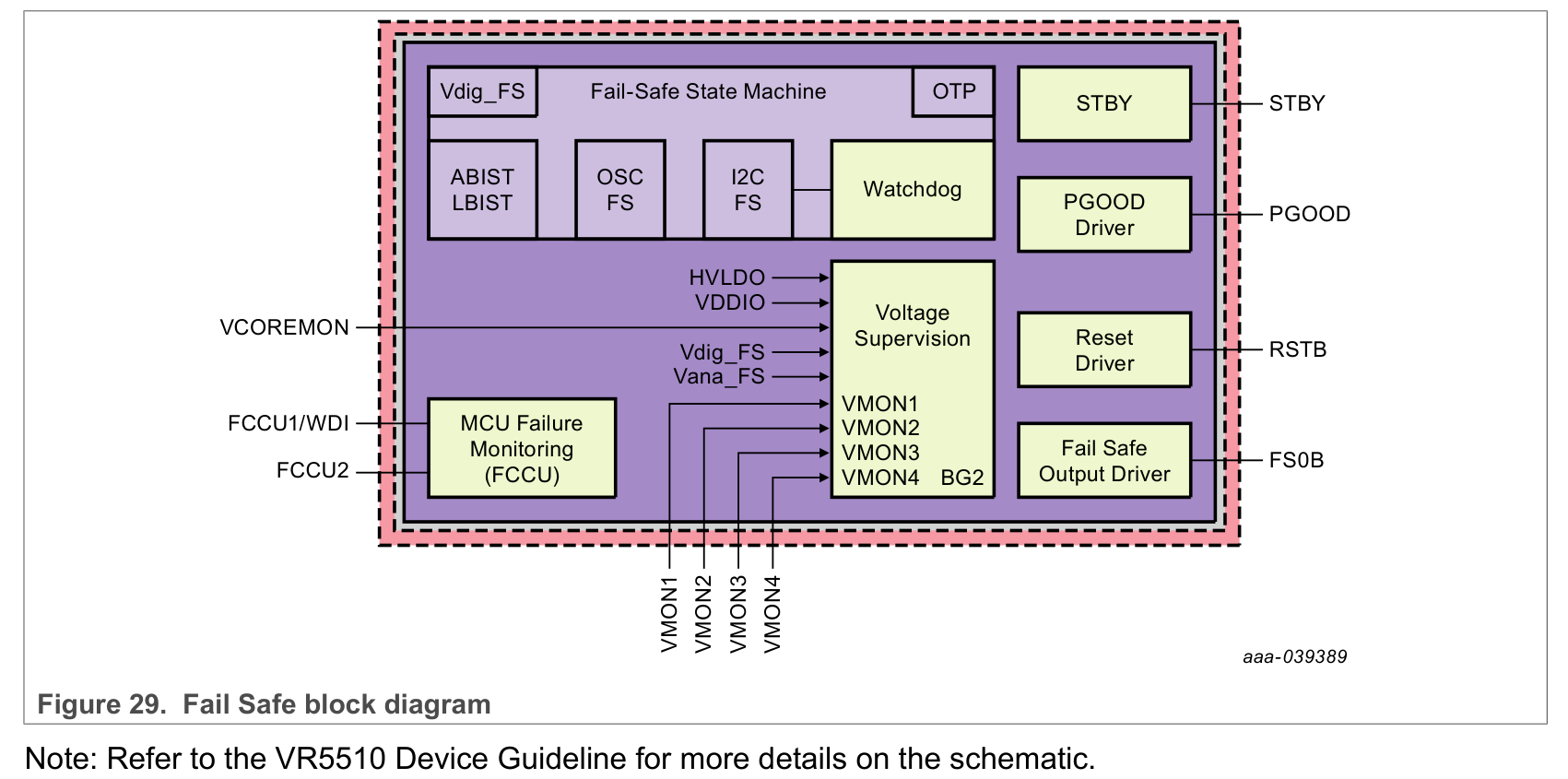

图29展示了故障安全域及其专用引脚。

22.2 QM与ASIL-B与ASIL-D的比较

22.3 失效安全初始化

在POR或从待机模式或深度睡眠模式唤醒后,当释放RSTB引脚时,故障安全状态机进入INIT_FS阶段进行初始化。为了确保在INIT_FS期间的写入过程(除了I2C传输期间的CRC计算),MCU必须执行以下序列以对所有INIT_FS寄存器进行操作。下面描述了该过程,其中Register_A后缀表示任何INIT_FS寄存器的后缀(例如FS_I_FSSM、FSI_I_SVS等)。

- 在FS_I_Register_A(DATA)中写入所需的数据。

- 在FS_I_NOT_Register_A(DATA_NOT)中写入FS_I_Register A的一补数。

例如,如果FS_I_Register_A = 0xABCD,则必须将0x5432(0xABCD的一补数)写入FS_I_NOT_Register_A。只有DATA_NOT内容中的实用位需要取反。保留位不被考虑,可以写入零。

VR5510执行实时比较过程(XOR),以确保DATARS_I_Register_A = DATA_NOT FS_I_NOT_Register_A。

如果比较结果正确,则将REG_CORRUPT位(FS_STATES寄存器)设置为零。如果比较结果错误,则将REG_CORRUPT位设置为一。在第一个良好的看门狗刷新关闭INIT_FS阶段之后,REG_CORRUPT监视是活动的。

在窗口超时之前,必须通过第一个良好的看门狗刷新来关闭INIT_FS阶段。

窗口持续时间可通过WD_INIT_TIMEOUT_OTP[1:0]位(CFG_2_OTP寄存器)进行编程。

在INIT_FS阶段关闭后,可以通过设置GOTO_INITFS位(FS_SAFE_IOS寄存器)从任何其他FS_state重新进入该阶段。

22.4 看门狗

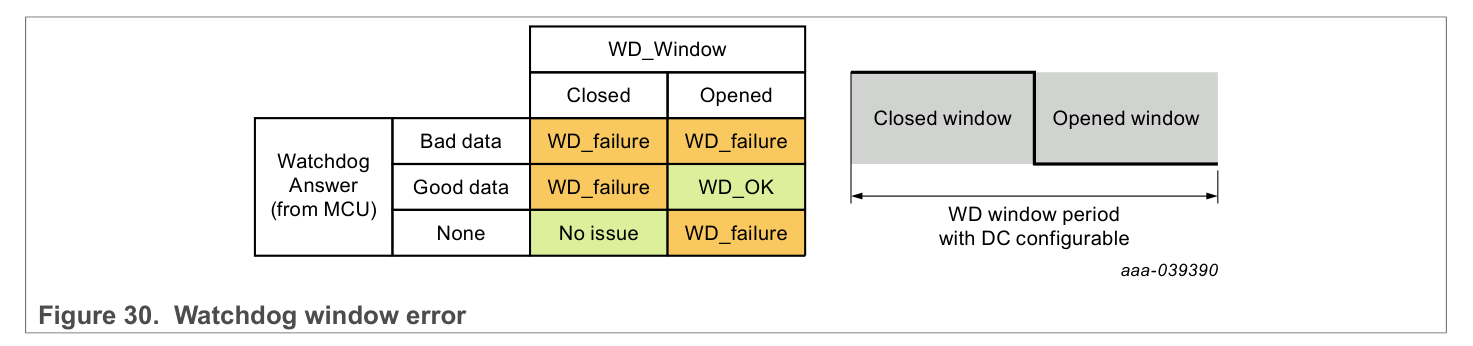

看门狗是用于Simple和Challenger看门狗的窗口化看门狗。窗口的第一部分称为关闭窗口,第二部分称为打开窗口。在打开窗口期间,良好的看门狗刷新是指良好的看门狗响应。坏的看门狗刷新是指在打开窗口期间出现坏的看门狗响应、没有进行任何看门狗刷新或者在关闭窗口期间有良好的看门狗响应。在进行了良好或坏的看门狐刷新后,新的时间段立即开始,以使MCU与突发式监控保持同步。图30说明了可能出现的监控错误情况:

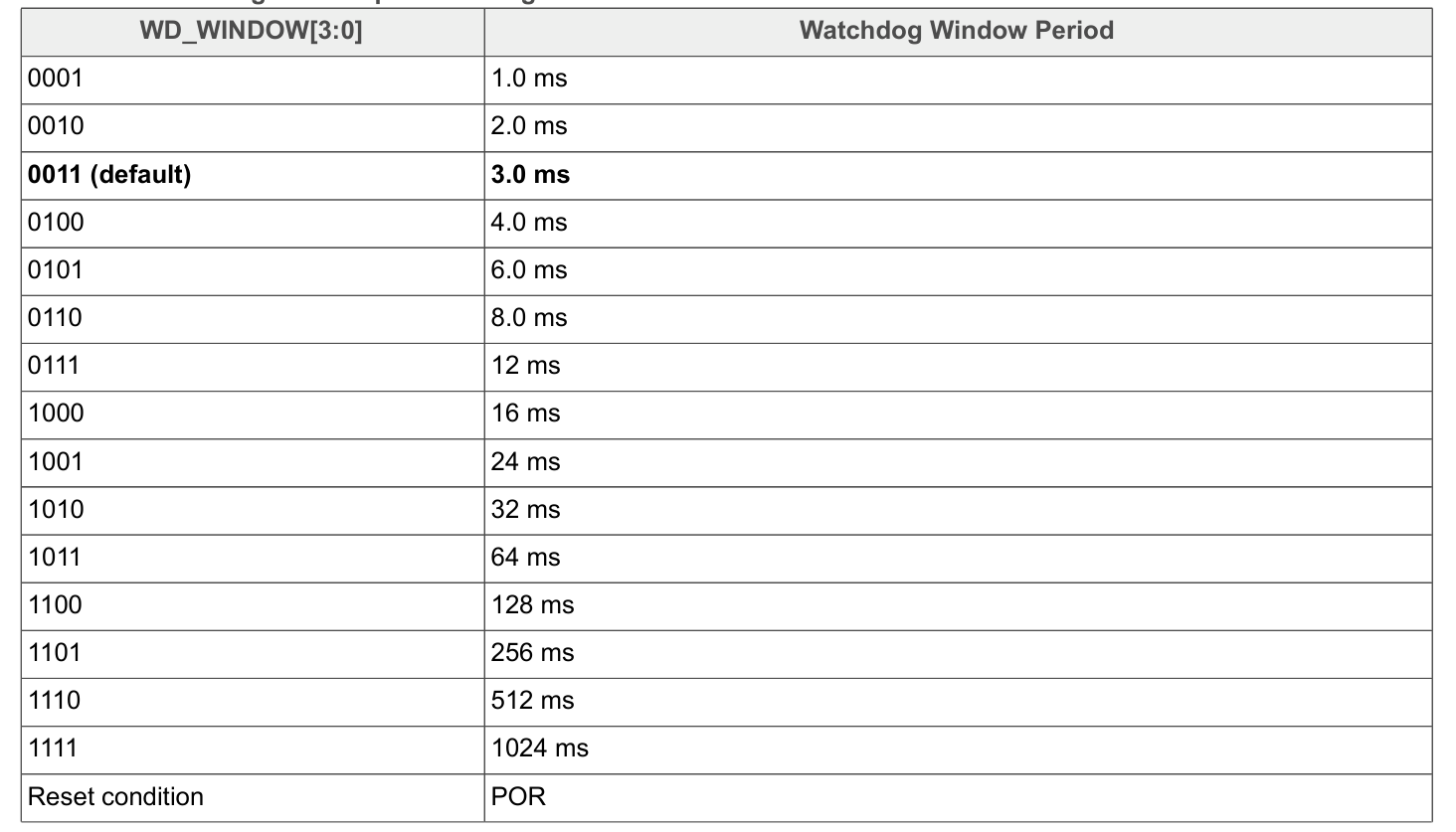

第一个良好的看门狗刷新关闭了INIT_FS阶段。看门狗窗口继续运行,MCU必须在看门狗窗口期的OPEN窗口中刷新看门狗。看门狗窗口的持续时间可通过WD_WINDOW [3:0]位(FS_WD_WINDOW寄存器)进行配置,范围从1毫秒到1024毫秒。新的看门狗窗口在下一次刷新后生效。只能在INIT_FS阶段禁用看门狗窗口。当INIT_FS关闭时,禁用看门狗将生效。

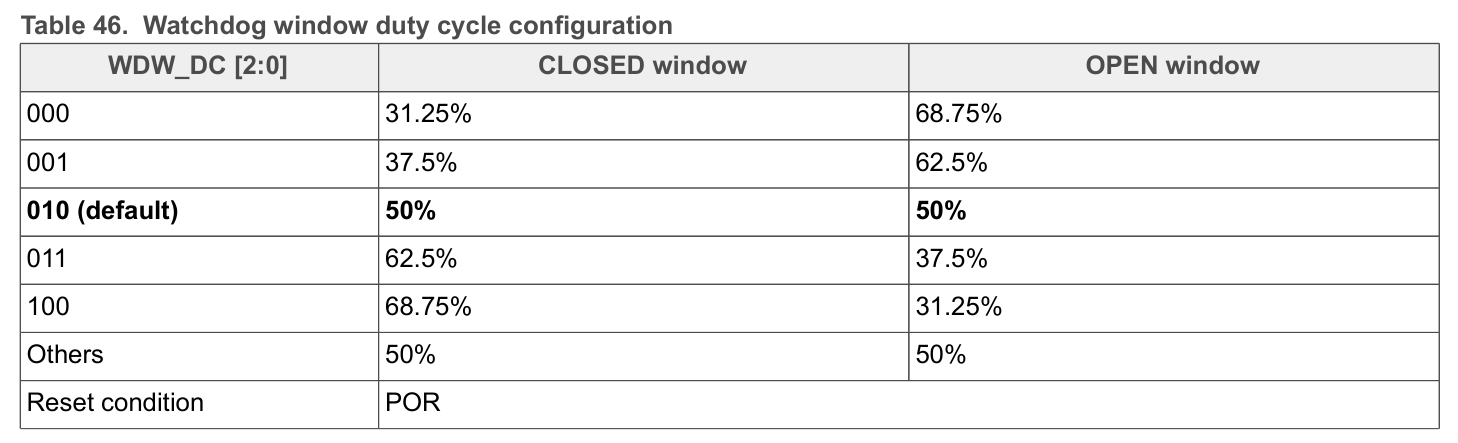

看门狗窗口的占空比可通过WDW_DC [2:0]位(FS_WD_WINDOW寄存器)进行配置,范围从31.25%到68.75%。新的占空比在下次看门狗刷新后生效。

22.4.1 Simple watchdog

简单看门狗使用了一个独特的种子。MCU可以将自己的种子发送到WD_SEED位域(FS_WD_SEED寄存器),或者可以使用默认值0x5AB2。在打开看门狗窗口期间,这个种子必须写入WD_ANSWER位域(FS_WD_ANSWER寄存器)。当结果正确时,看门狗窗口被重新启动。当结果不正确时,WD错误计数器会递增,并且看门狗窗口被重新启动。在简单看门狗配置中,不能向WD_SEED写入0xFFFF和0x0000值。如果尝试写入0x0000或0xFFFF,则报告通信错误。

22.4.2 Challenger watchdog

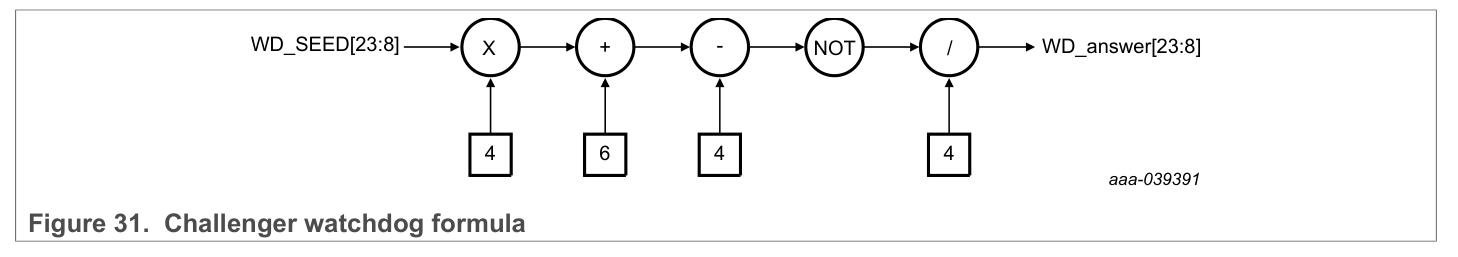

挑战者看门狗基于VR5510和MCU之间的问答交流。在INIT_FS阶段,VR5510实现了一个线性反馈移位寄存器(LFSR)来生成一个16位伪随机字。MCU可以发送不同的LFSR种子或使用默认的VR5510 LFSR值(0x5AB2)进行预定义计算。结果通过I2C传输,在打开看门狗窗口期间由VR5510进行验证。当结果正确时,看门狗窗口被重新启动并生成新的LFSR。当结果错误时,WD错误计数器增加,看门狗窗口被重新启动,并且LFSR值不变化。

在初始化阶段(INIT_FS),MCU发送LFSR的种子,或使用由VR5510生成的默认LFSR值(0x5AB2),该值可在WD_SEED寄存器中获得。使用这个LFSR,MCU根据下面的公式执行简单计算,并将结果发送到WD_ANSWER寄存器中。

22.4.3 看门狗错误计数

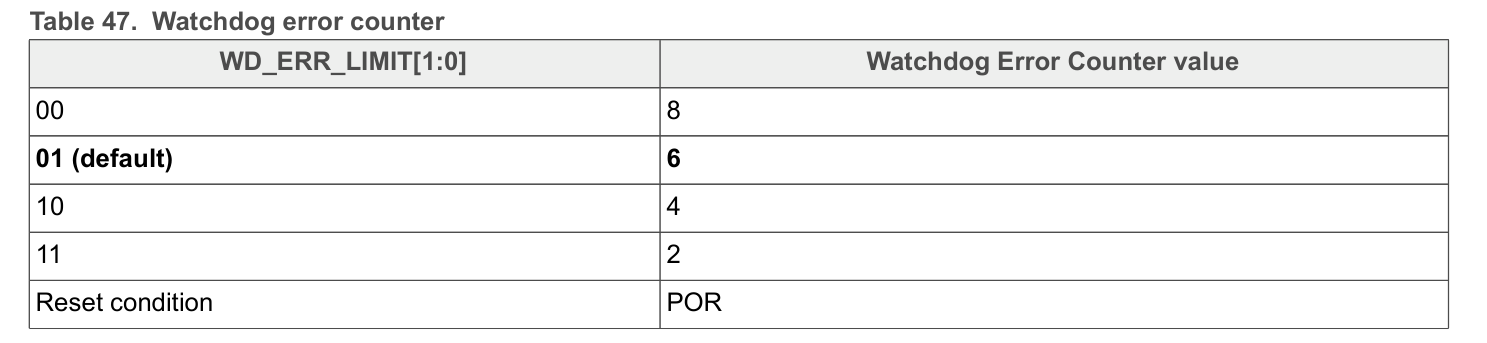

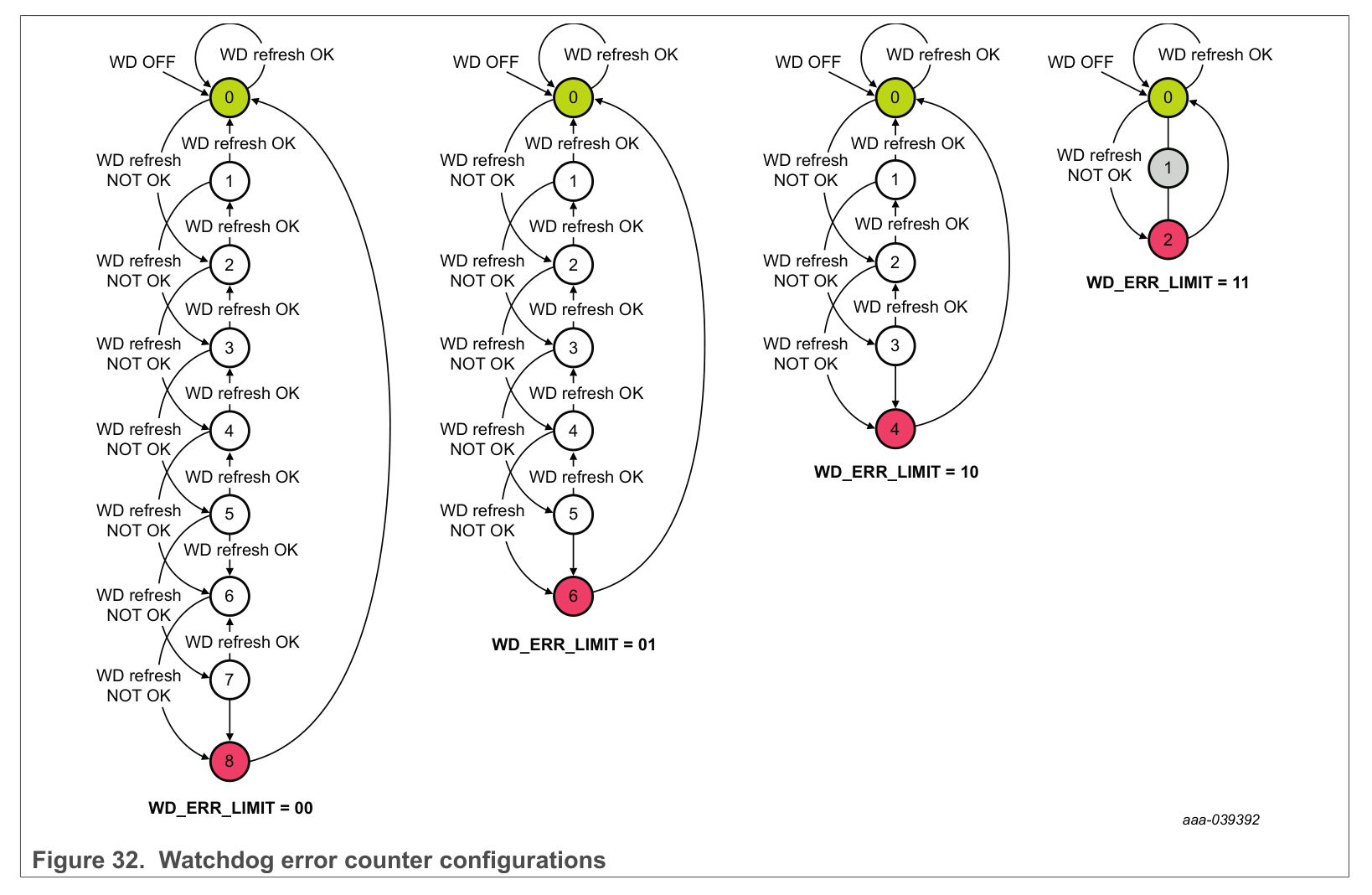

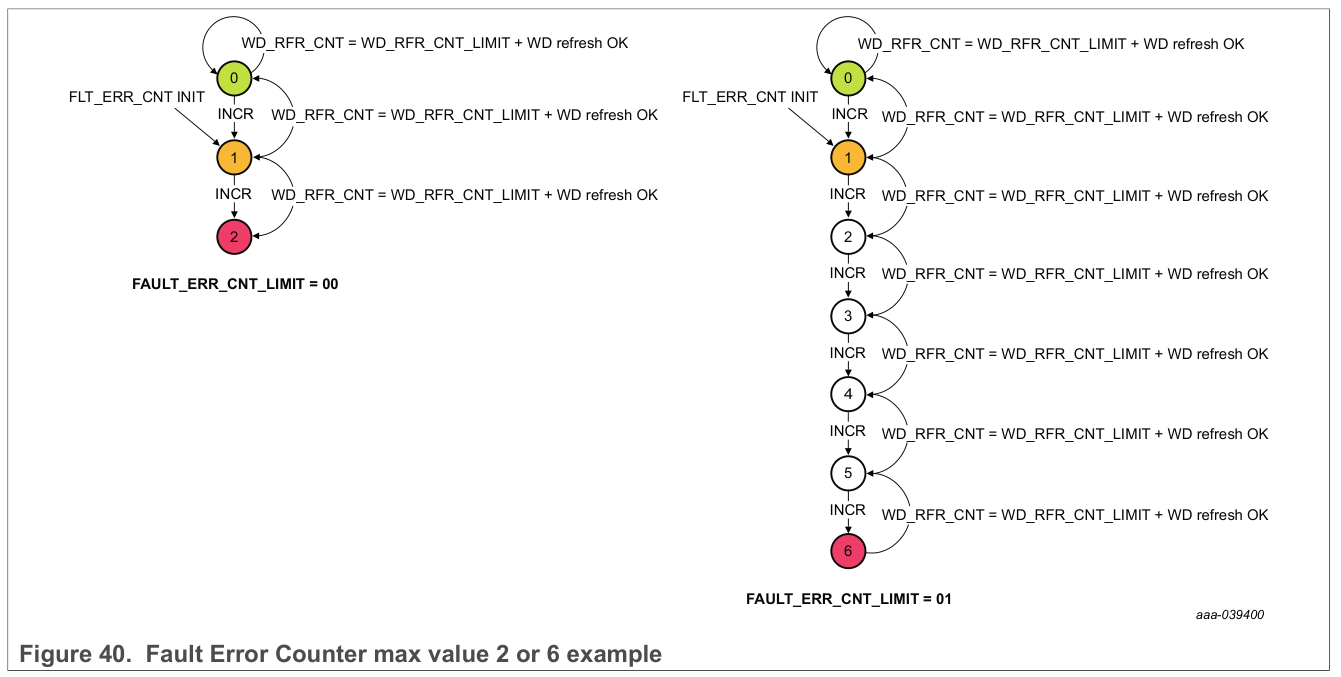

看门狗错误策略适用于Challenger看门狗和Simple看门狗。设备中实现了看门狗错误计数器,用于过滤不正确的看门狗刷新。每次发生看门狗故障时,设备将计数器增加两个单位。每次成功刷新看门狗时,计数器减少一个单位。这个原则确保循环的‘OK/NOK’行为在故障检测上收敛。

为了允许应用程序的灵活性,在INIT_FS阶段可以通过WD_ERR_LIMIT[1:0]位字段(FS_I_WD_CFG寄存器)配置看门狗错误计数器的最大值。

为了诊断目的,MCU可以从FS_I_WD_CFG寄存器的WD_ERR_CNT[3:0]位域中读取看门狗错误计数器值。

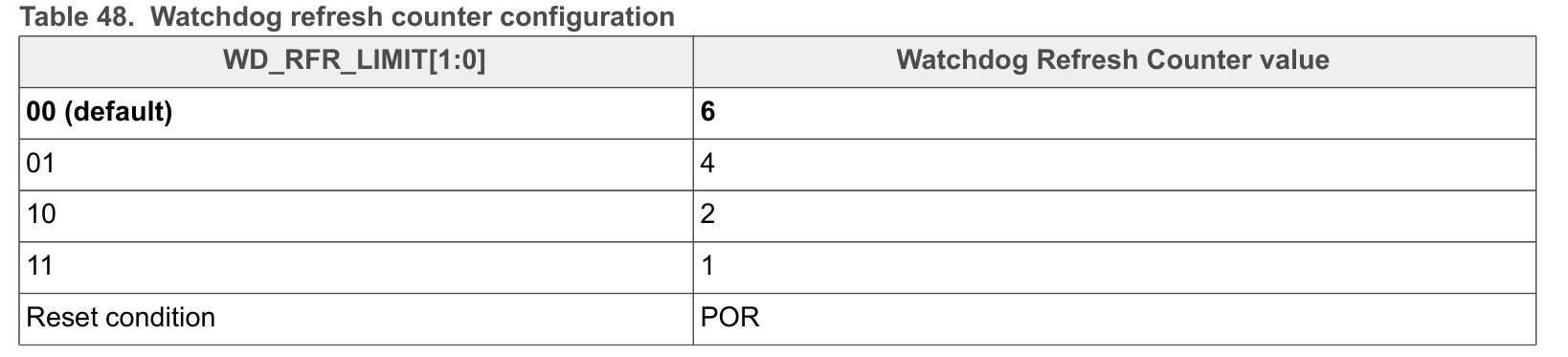

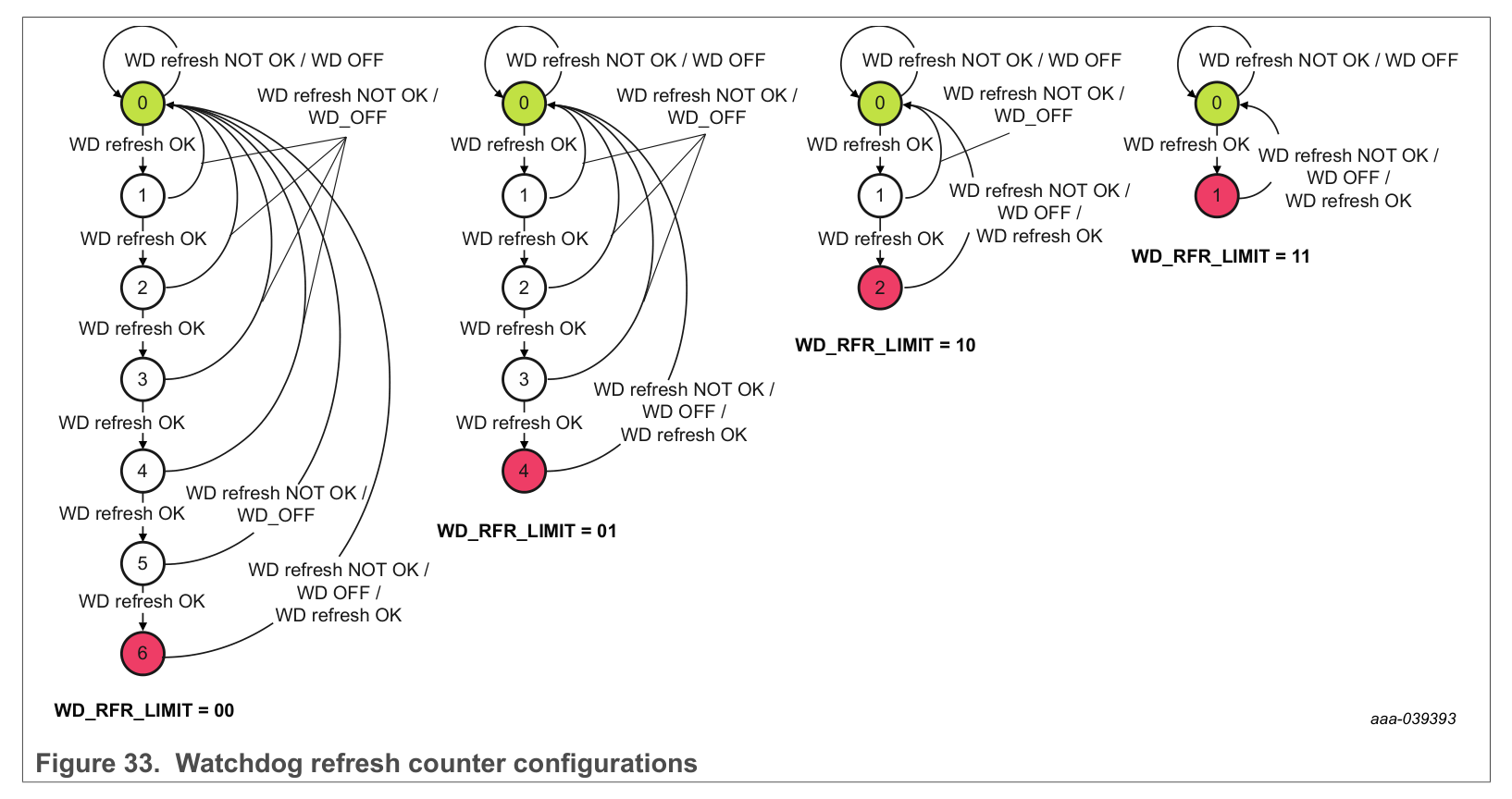

22.4.4 看门狗刷新计数

看门狗刷新策略适用于Challenger看门狗和Simple看门狗。看门狗刷新计数器用于递减故障错误计数器。每次成功刷新看门狗时,看门狗刷新计数器增加一。每当看门狗刷新计数器达到其最大值(默认为六),如果下一个WD刷新也是正常的,则故障错误计数器减少一。无论看门狗刷新计数器处于什么位置,每次发生错误的刷新时,都会将该计数器重置为零。

为了在应用中提供灵活性,在INIT_FS阶段可以使用WD_RFR_LIMIT[1:0]位字段(FS_I_WD_CFG寄存器)配置看门狗刷新计数器的最大值。

为了诊断目的,MCU可以通过FS_I_WD_CFG寄存器中的WD_RFR_CNT[2:0]位字段读取看门狗刷新计数器的值。

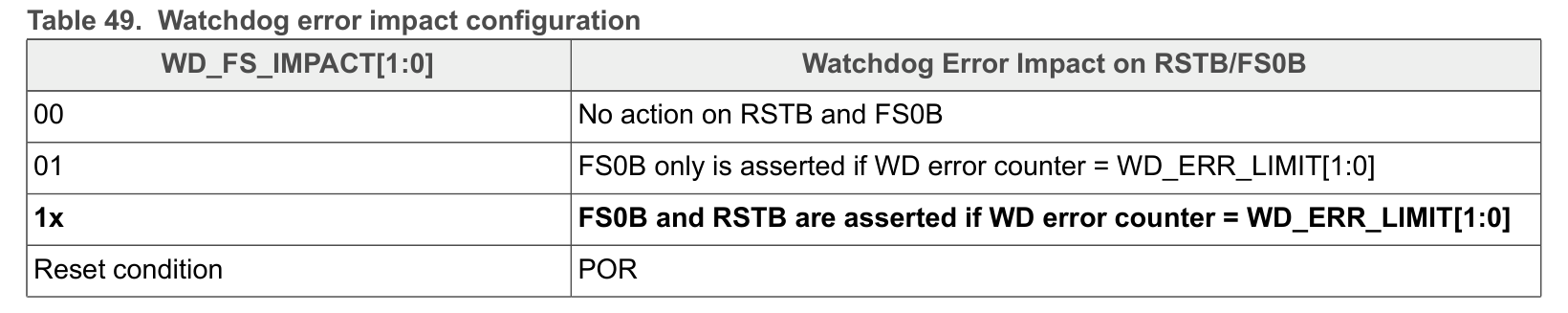

22.4.5 看门狗错误影响

当看门狗错误计数器达到最大值时,在INIT_FS阶段可以通过WD_FS_IMPACT[1:0]位字段(FS_I_WD_CFG寄存器)配置RSTB和/或FS0B上的故障安全反应。

22.4.6 MCU故障恢复策略

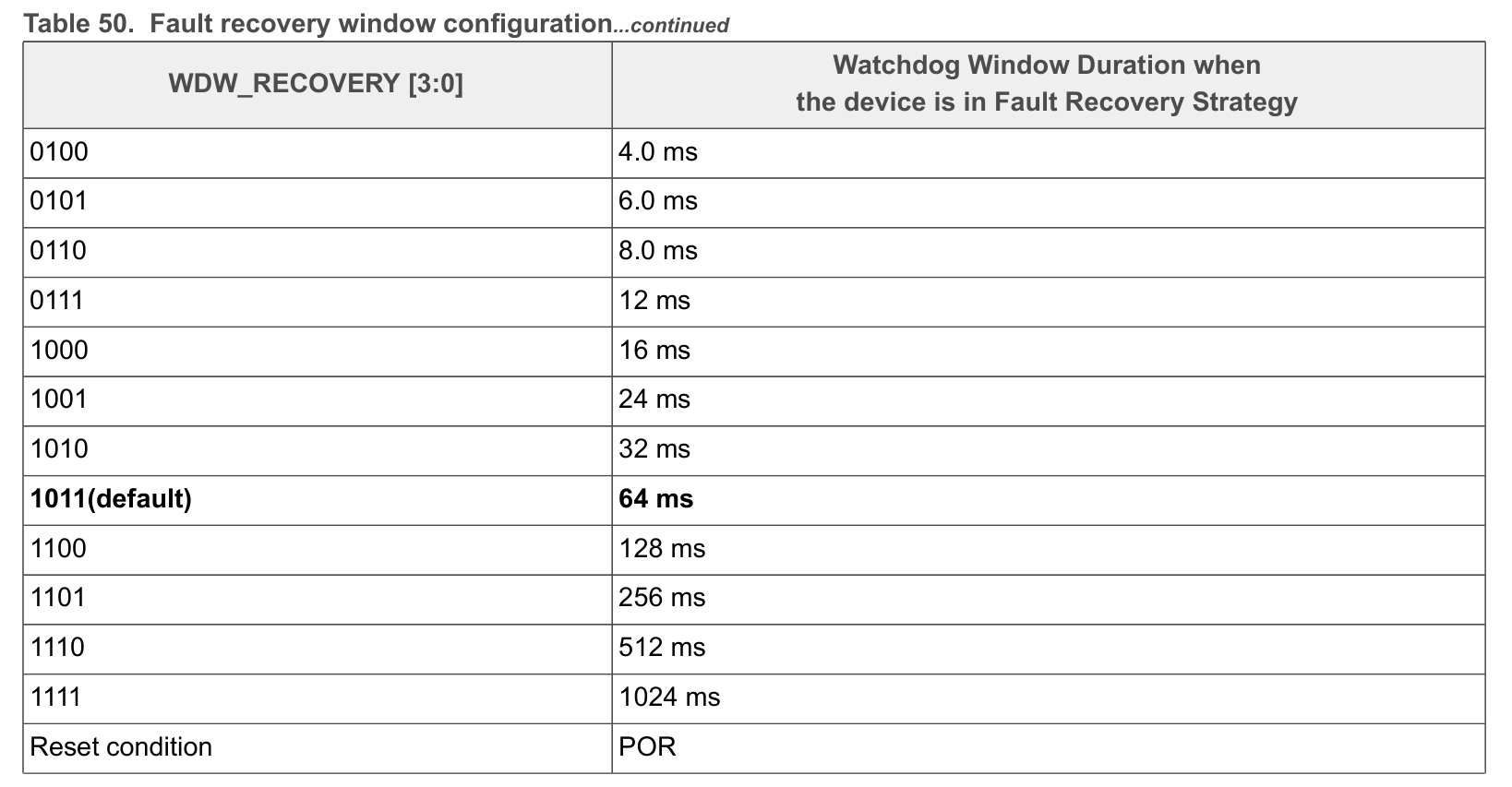

这个功能扩展了看门狗窗口,允许MCU执行故障恢复策略。目标是在故障事件后,防止MCU在尝试恢复应用程序时被重置。当MCU通过其FCCU引脚触发故障时,设备会断言FS0B引脚,并且看门狗窗口持续时间自动变为开放窗口(没有更多的占空比)。

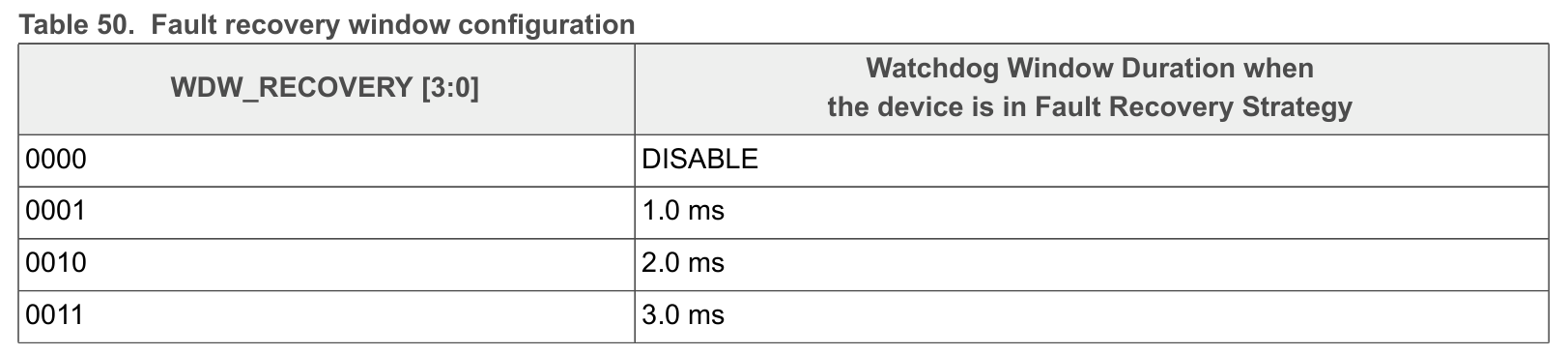

在INIT_FS阶段可以使用WDW_RECOVERY [3:0]位字段(FS_WD_WINDOW寄存器)配置此开放窗口持续时间。

当FCCU引脚指示错误并且FS0B被断言时,从WD_WINDOW到WDW_RECOVERY的转换发生。

如果MCU在WDW_RECOVERY持续时间结束之前发送了一个良好的看门狗刷新信号,并且FCCU引脚不再指示错误,则设备会切换回WD_WINDOW持续时间和相关的占空比。否则,将启动新的WDW_RECOVERY周期。

如果MCU在WDW_RECOVERY持续时间结束之前没有发送良好的看门狗刷新信号,则会生成复位脉冲,并且故障安全状态机返回INIT_FS状态。

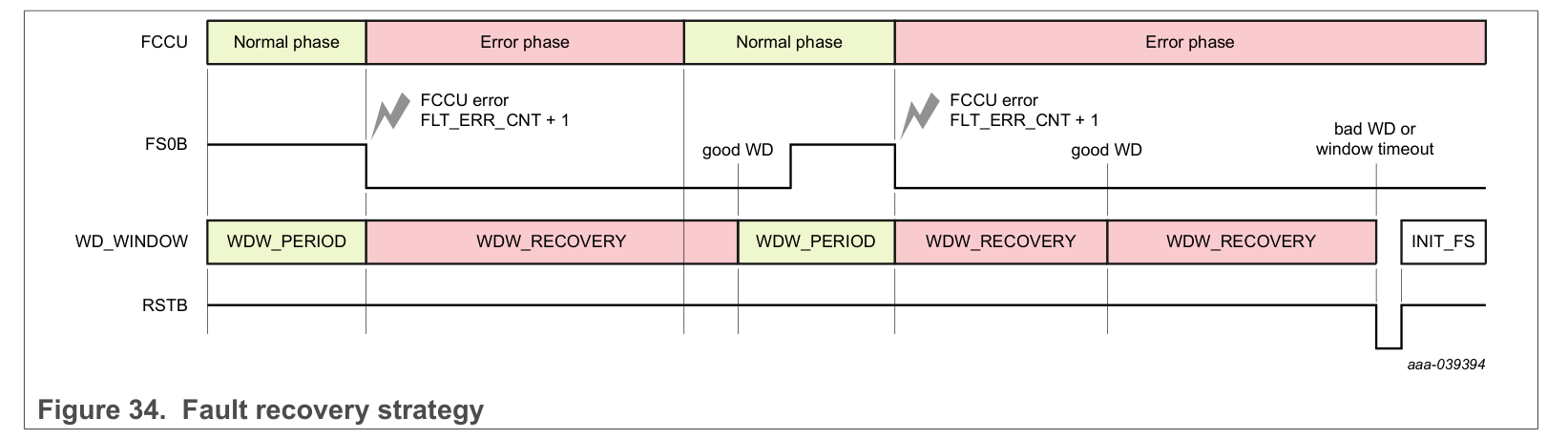

22.5 FCCU监控

FCCU输入引脚监测MCU的硬件故障。FCCU输入引脚可以通过成对配置,或作为单独的独立输入进行配置。只要第一个良好的看门狗刷新关闭INIT_FS,FCCU监测就会激活。使用FCCU_CFG[1:0]位字段(FS_I_SAFE_INPUTS寄存器)来配置FCCU输入引脚,可以成对配置或单独设置。

22.5.1 FCCU12通过成对监控

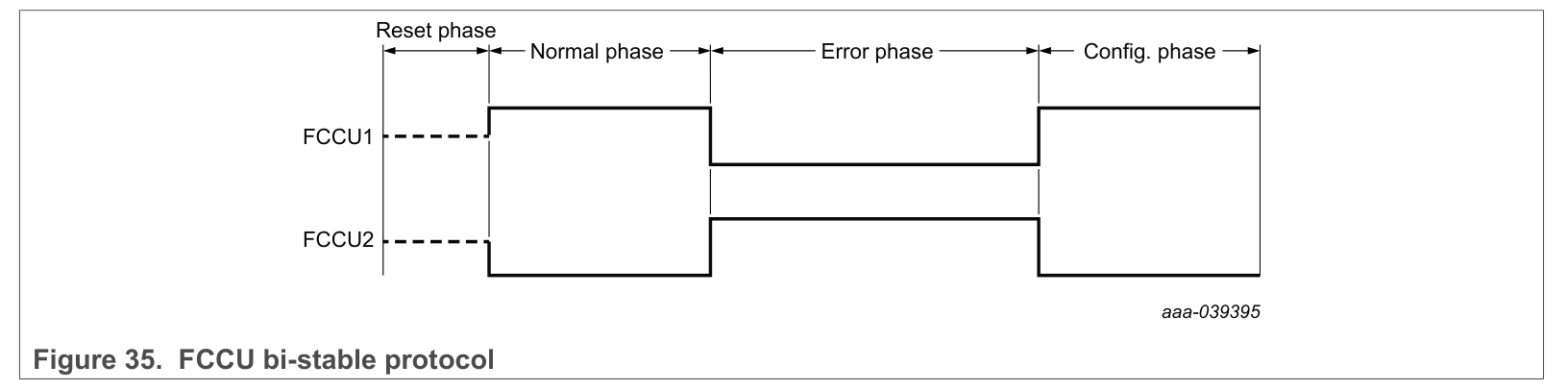

当FCCU12成对使用时,双稳态协议得到支持,如图35所示。

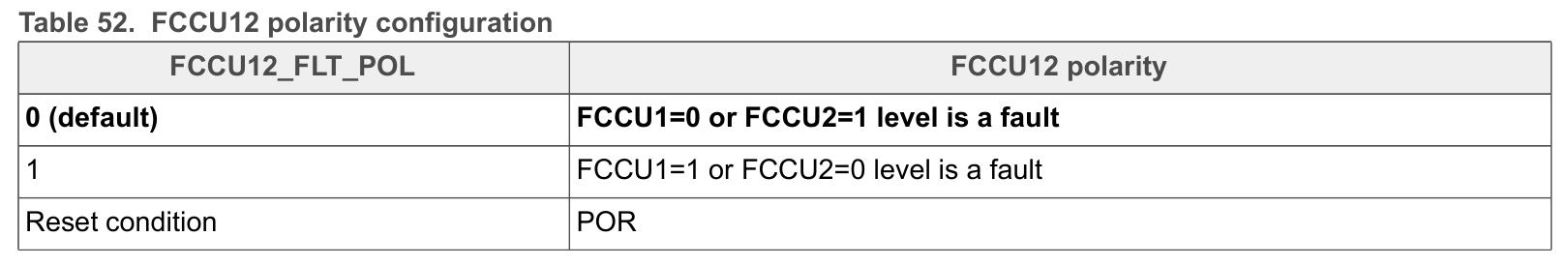

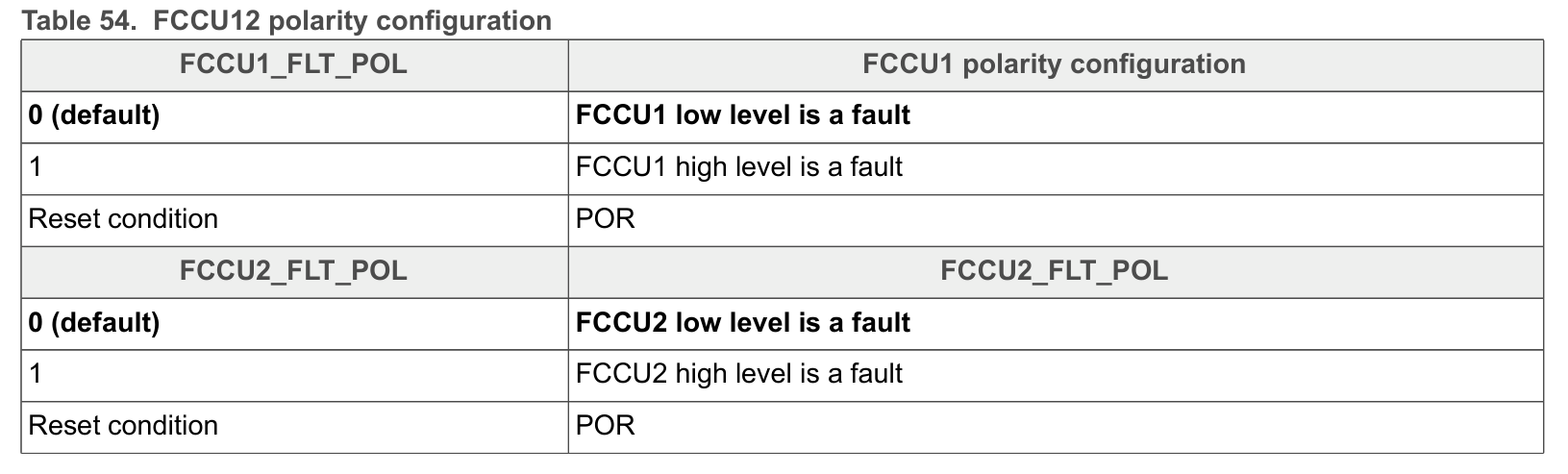

FCCU故障信号的极性在INIT_FS阶段可以通过FCCU12_FLT_POL位(FS_I_SAFE_INPUTS寄存器)进行配置。

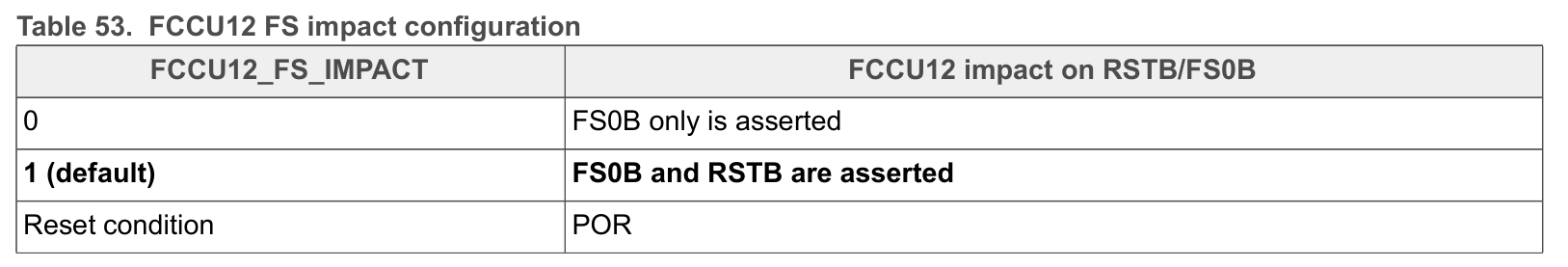

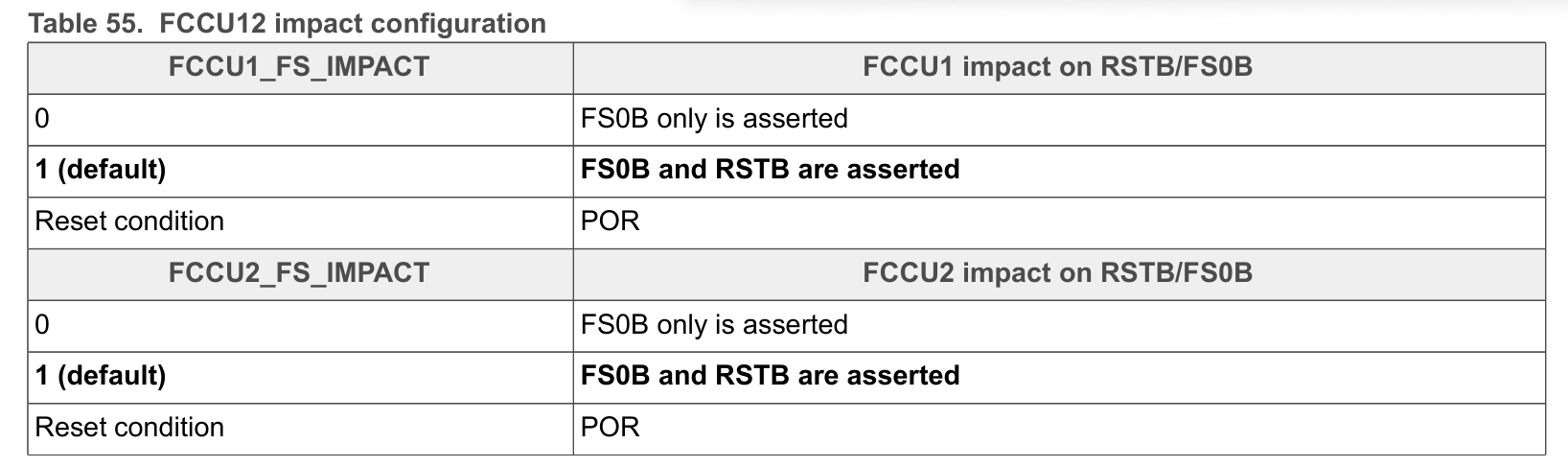

当检测到FCCU故障时,在INIT_FS阶段可以通过FCCU12_FS_IMPACT位(FS_I_SAFE_INPUTS寄存器)对RSTB和/或FS0B上的失效安全反应进行配置。

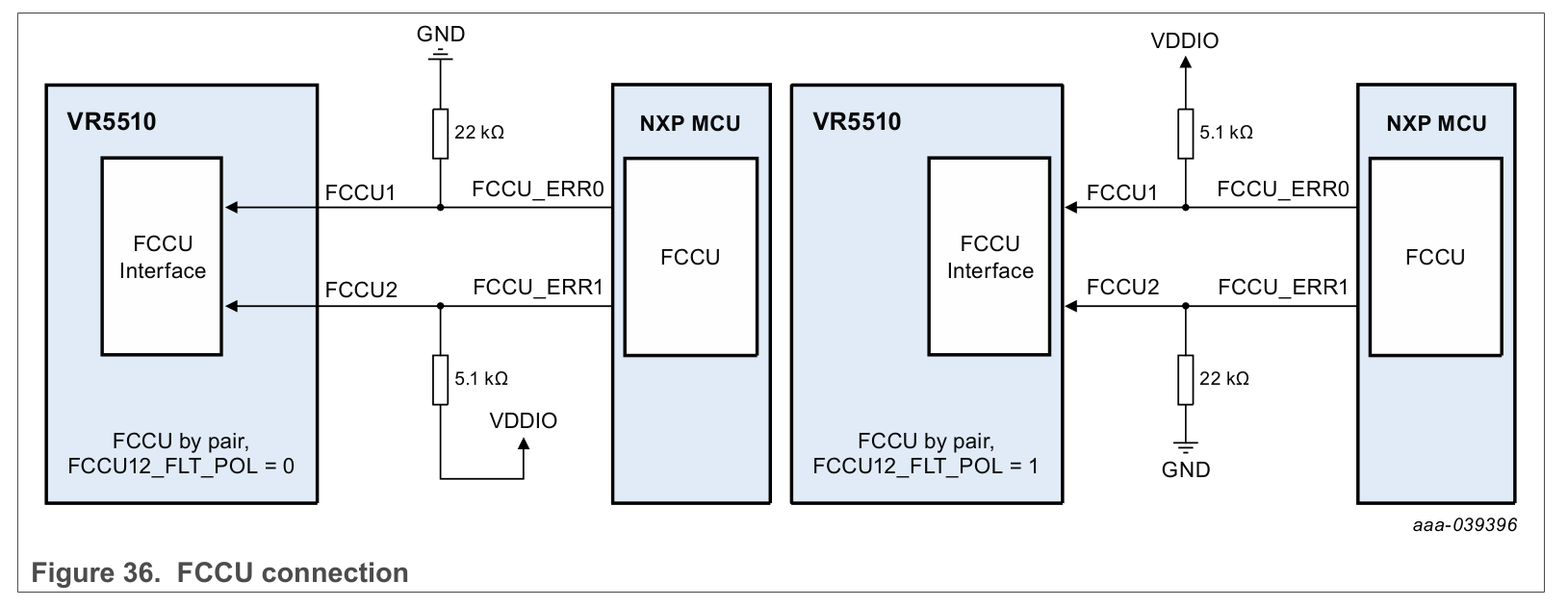

如果MCU不驱动其FCCU输出引脚,则需要外部上拉/下拉电阻来提供被动错误状态。

无论VDDIO电压是1.8V还是3.3V,为了检测到FCCU1短路至FCCU2故障模式,下拉电阻值必须至少是上拉电阻值的四倍。

22.5.2 FCCU12独立监测

当FCCU1和/或FCCU2独立使用时,FCCU输入可以监测两个不同且独立的错误信号。对于每个输入,在INIT_FS阶段可以通过FCCU1_FLT_POL和FCCU2_FLT_POL位(FS_I_SAFE_INPUTS寄存器)进行配置以确定FCCU故障信号的极性。

当检测到FCCU故障时,在INIT_FS阶段可以通过配置FCCU1_FS_IMPACT和FCCU2_FS_IMPACT位(FS_I_SAFE_INPUTS寄存器)来设置RSTB和/或FS0B上的失效安全反应。

22.5.3 i.MX处理器的FCCU1 WDI功能

FCCU1可以通过OTP配置为工作在WDI引脚上,以便与i.MX处理器应用兼容。要将FCCU1配置为WDI引脚,请将FCCU_OR_WDI_OTP位(CFG_1_OTP寄存器)设置为1。极性是通过WDI_POL_OTP位(CFG_I2C_OTP寄存器)进行配置的。当MCU触发WDI引脚时,系统会进入深度故障安全模式,然后重新启动应用程序。

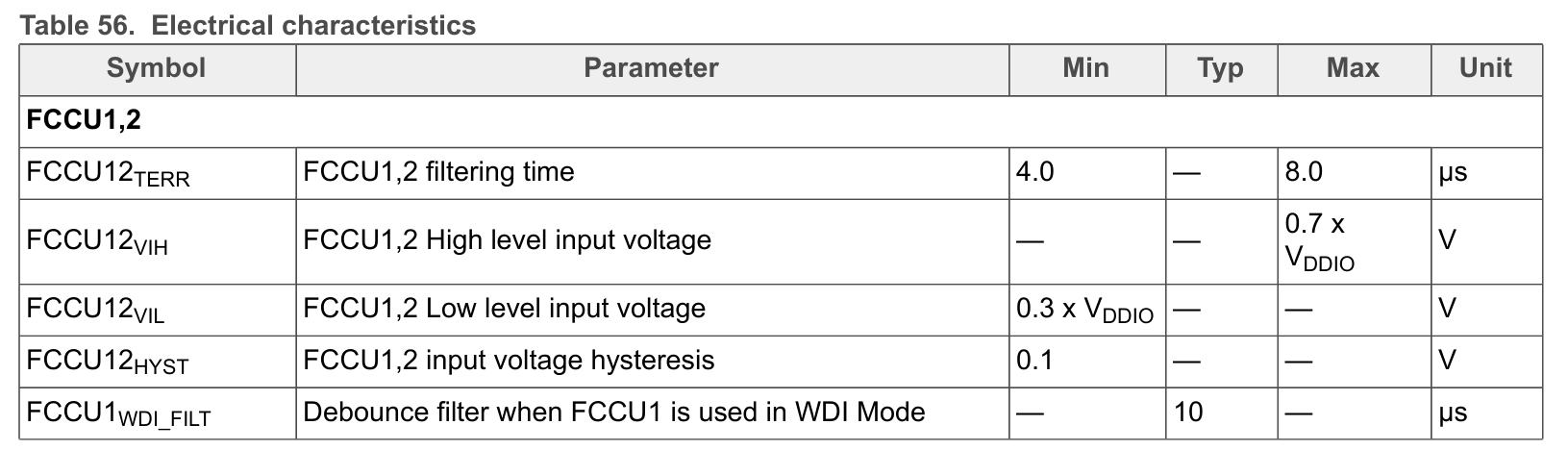

22.5.4 FCCU12 电气特性

除非另有规定,否则TA范围为-40°C至125°C。除非另有规定,VSUP范围为VSUP_UVH至36V。所有电压均以地面为参考。典型值基于TA=25°C。

22.6 电压监控器

电压监控器监测VCOREMON、HVLDO、VDDIO和VMON1/2/3/4输入引脚上的过压和欠压情况。当由这些引脚之一监测到VR5510调节器的过压时,相关的VR5510调节器将被关闭,直到故障解除为止。只要FS_ENABLE=1,电压监控就会生效。根据情况报告UV/OV标志位。

22.6.1 VCOREMON 电压监控

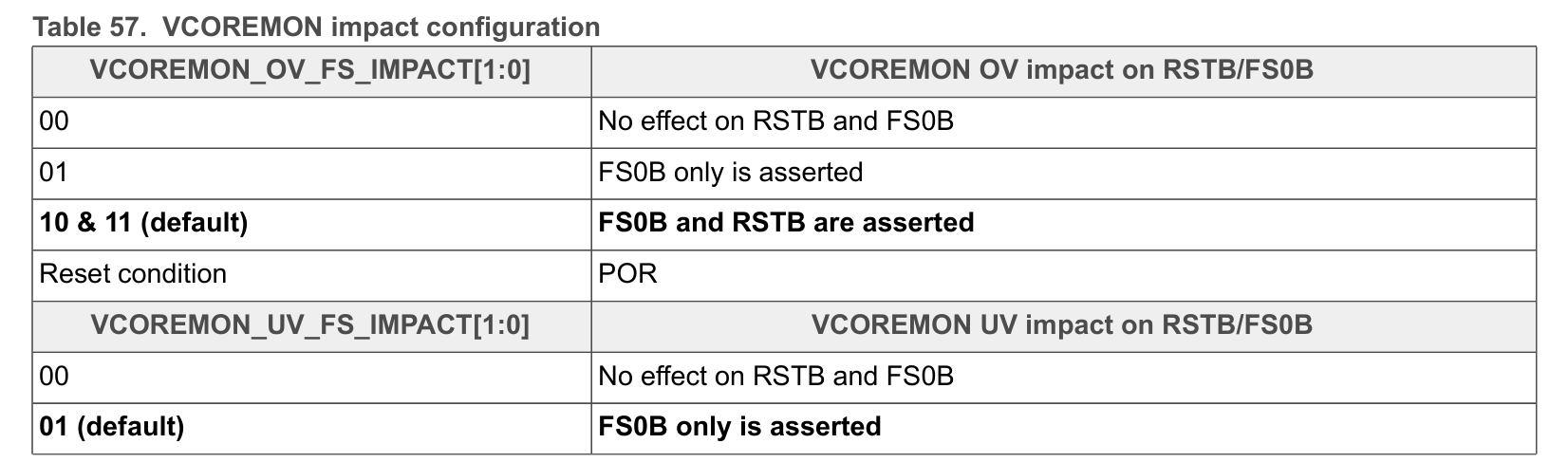

VCOREMON输入引脚专用于BUCK1或BUCK1和BUCK2在双相操作中。当检测到过压或欠压故障时,在INIT_FS阶段可以通过VCOREMON_OV_FS_IMPACT[1:0]和VCOREMON_UV_FS_IMPACT[1:0]位字段(FS_I_OVUV_SAFE_REACTION1寄存器)配置RSTB和/或FS0B上的失效安全反应。

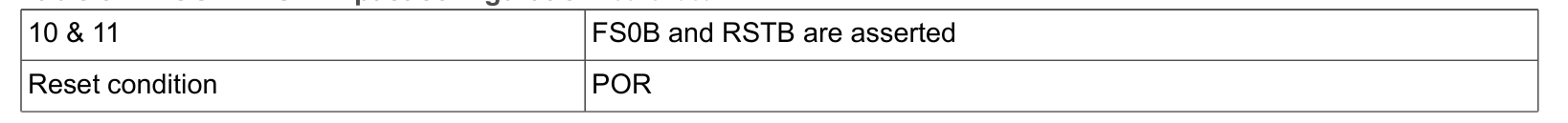

VCOREMON OV阈值可以通过OTP VCOREOVTH_OTP[3:0]位字段(CFG_UVOV_2_OTP寄存器)进行配置。VCOREMON UV阈值可以通过OTP VCOREUVTH_OTP[3:0]位字段(CFG_UVOV_6_OTP寄存器)进行配置。VCOREMON OV滤波可通过OTP OV_MCU_OTP位字段进行配置,而UV则可通过UV_MCU_OTP[1:0]位字段进行配置。这两个位字段都在CFG_DEGLITCH1_OTP寄存器中。

22.6.2 Static voltage scaling (SVS)

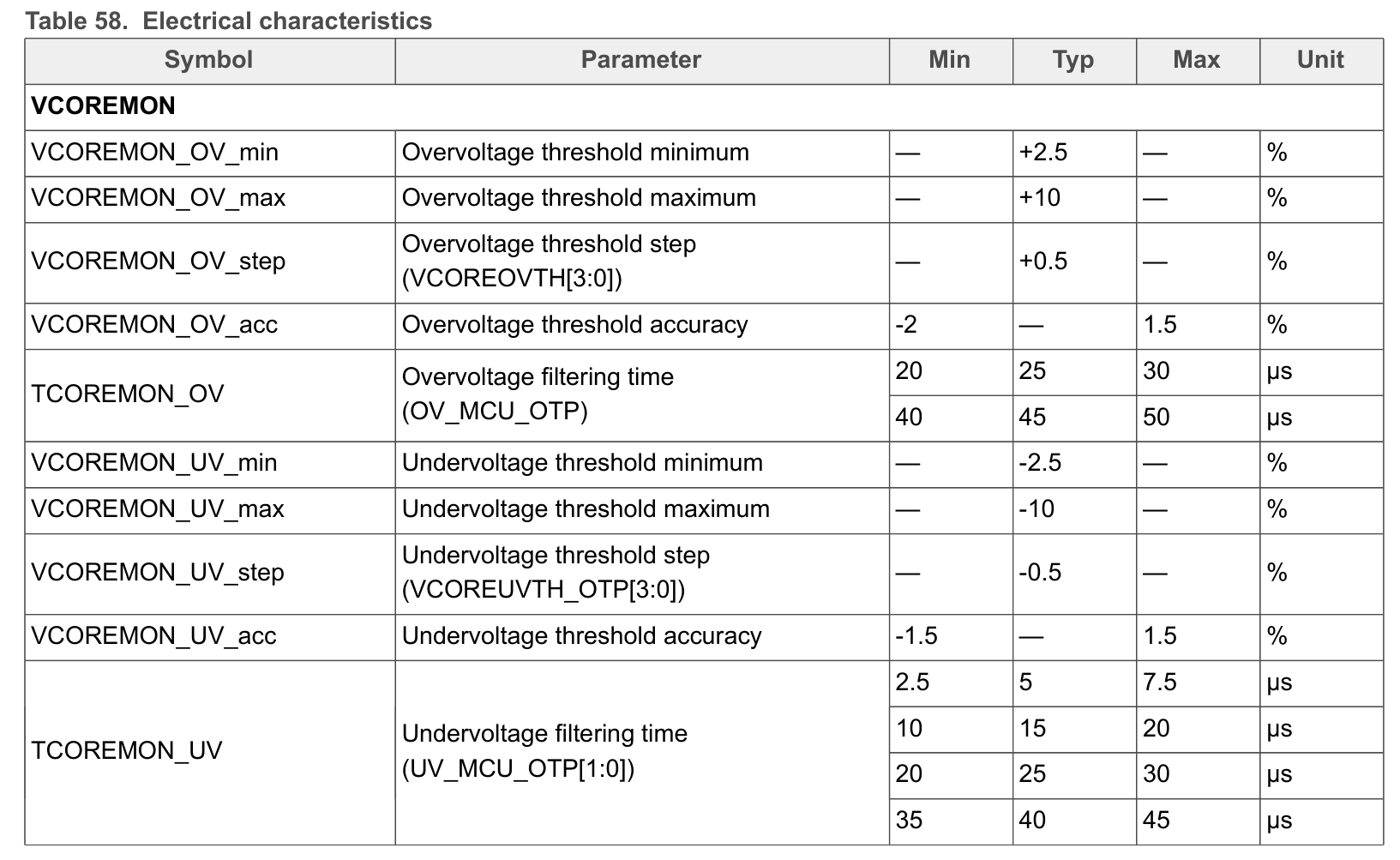

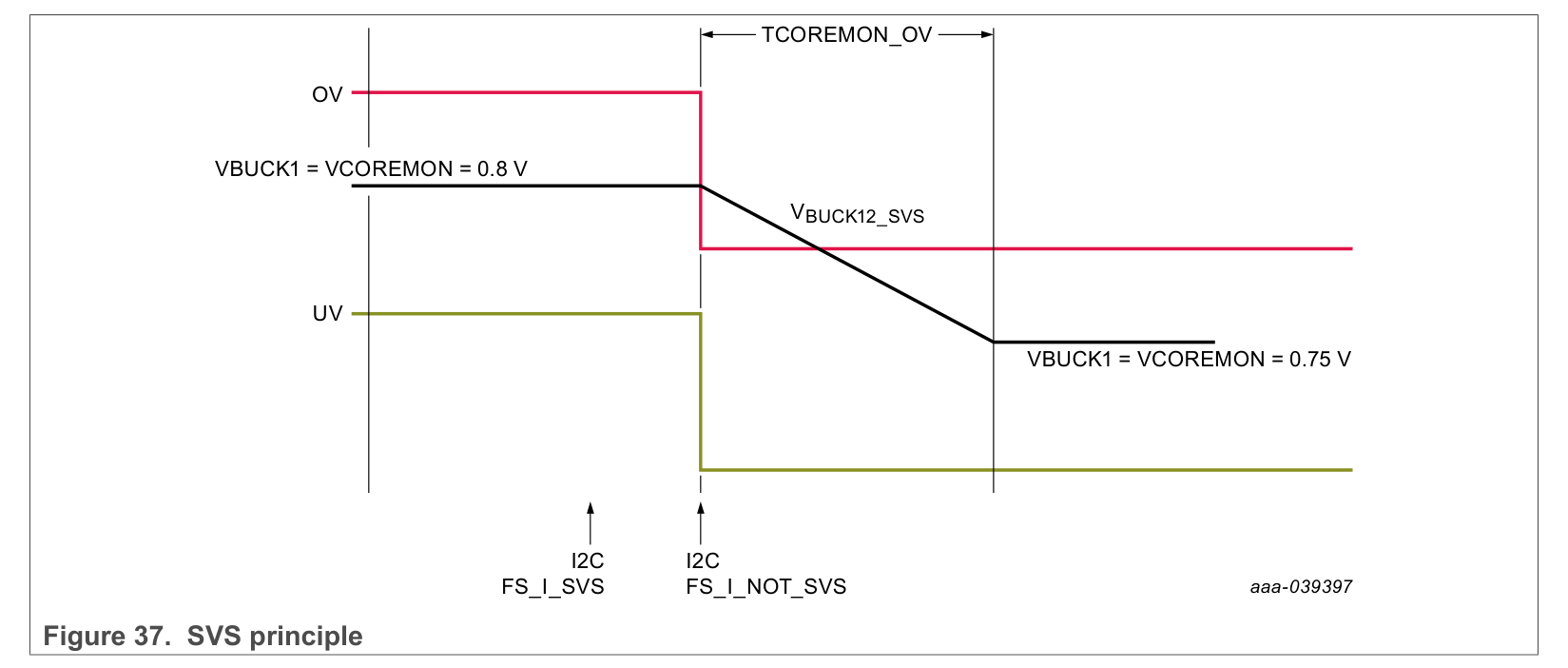

静态电压缩放功能允许MCU在BUCK1启动时降低或增加初始配置的输出电压(如果使用多相则还包括BUCK2)。SVS配置必须在INIT_FS阶段完成。偏移值可以通过I2C进行配置,使用SVS_OFFSET[5:0]位字段(FS_I_SVS寄存器),并且必须将精确的补码值写入NOT_SVS_OFFSET[5:0]位。

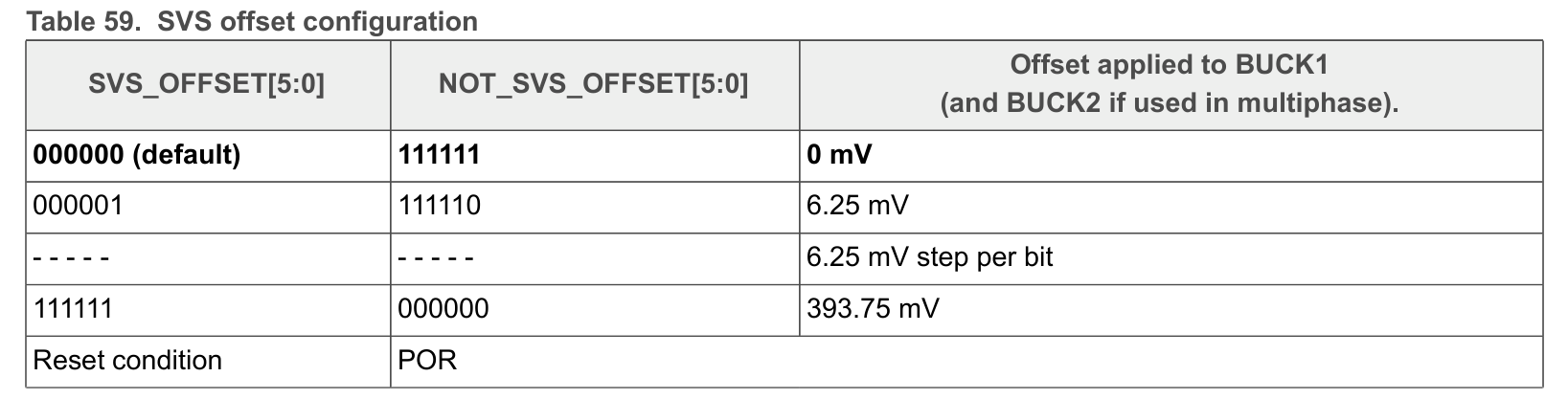

VCORE_SVS_CLAMP_OTP[5:0]位域(CFG_UVOV_3_OTP寄存器)设置应用程序可用的最大步数值。

VCORE_SVS_FULL_OFFSET_OTP位域(CFG_UVOV_3_OTP寄存器)将完整的偏移范围设置为仅负偏移或负偏移和正偏移。如果设置了完整的偏移范围,SVS_OFFSET_SIGN位(FS_I_SVS寄存器)选择偏移的符号。当接收到并确认有效的NOT_SVS_OFFSET[5:0] I2C命令时,BUCK1/2输出电压转换开始。

如果通过I2C命令发送的NOT_SVS_OFFSET[5:0]值不是与通过I2C命令发送的SVS_OFFSET[5:0]值一补码,则不执行SVS过程,并且BUCK1输出电压保持原始值。当接收到并确认有效的NOT_SVS_OFFSET[5:0] I2C命令时,OV/UV阈值立即发生变化。

因此,BUCK1输出电压转换在OV/UV滤波时间内完成。根据所需的偏移量,可能需要分多个步骤更改电压以避免触发OV/UV事件。

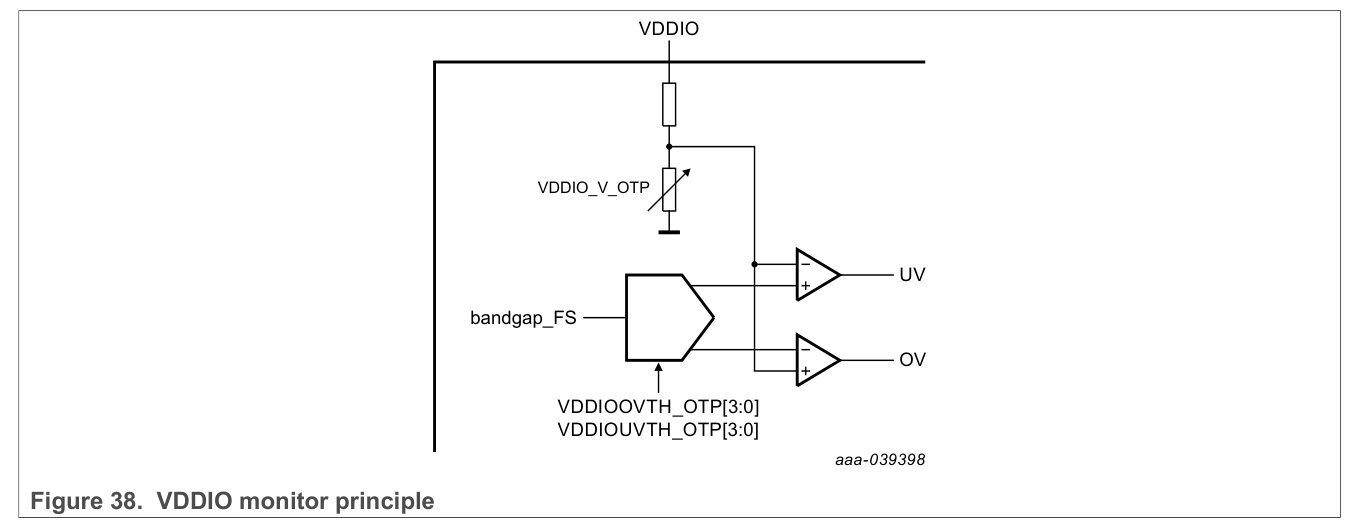

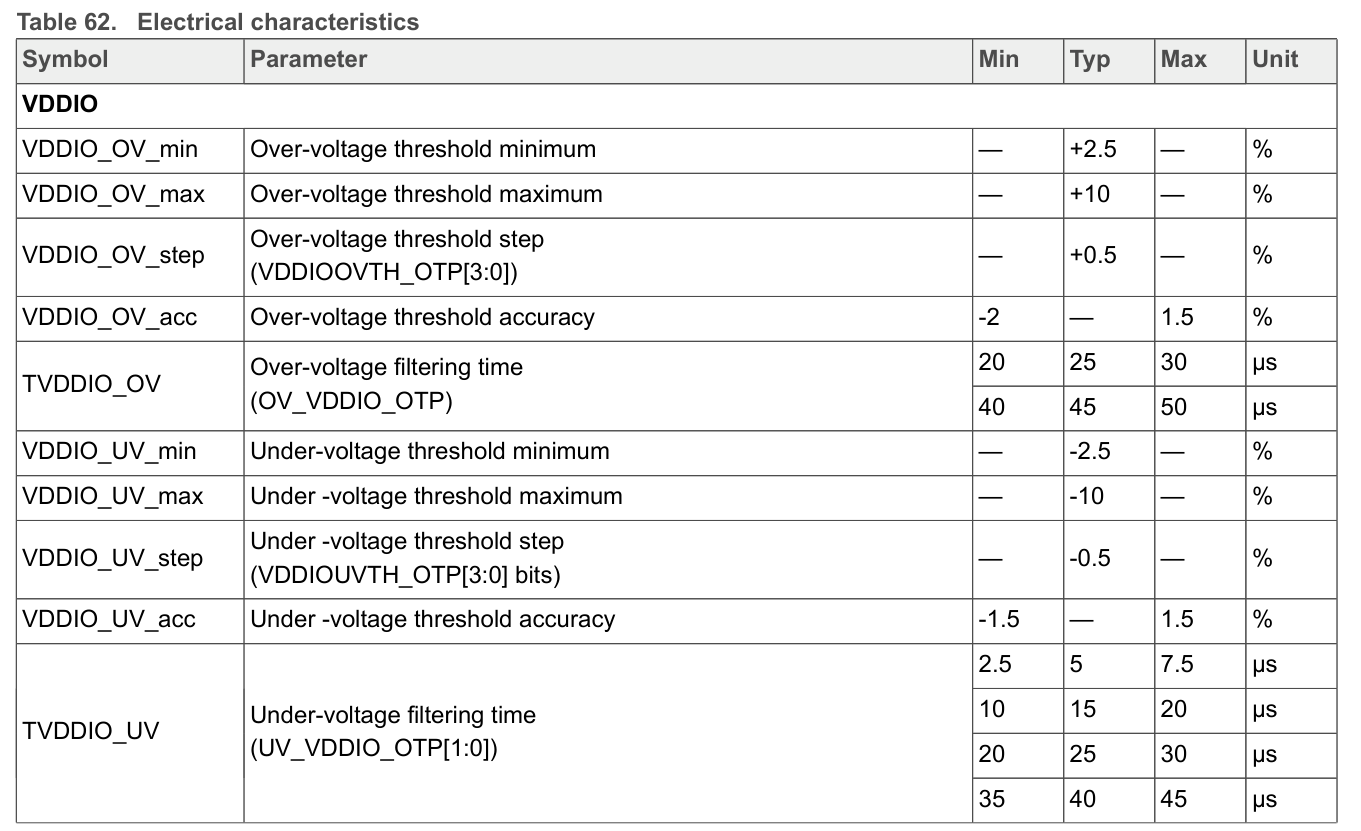

22.6.3 VDDIO monitoring

VDDIO输入引脚可以连接到VPRE、LDO1、LDO2、LDO3、BUCK2、BUCK3或外部调节器。连接到VDDIO的调节器必须为1.8 V或3.3 V,以与过压和欠压监测阈值兼容。通过VDDIO_REG_ASSIGN_OTP[2:0]位字段(CFG_I2C_OTP寄存器)中的配置设置来指定连接到VDDIO的调节器(因此,在发生过压检测时关闭哪个调节器)。

如果将外部调节器连接到VDDIO,则无法关闭该调节器,但会向MCU报告过压标志,MCU可以采取适当措施。

在所有情况下,RSTB和/或FS0B上的故障安全反应是通过FS_I_OVUV_SAFE_REACTION1寄存器中的VDDIO_OV_FS_IMPACT[1:0]和VDDIO_UV_FS_IMPACT[1:0]位字段进行配置的。

故障安全电压(1.8 V或3.3 V)可以通过VDDIO_V_OTP位(CFG_ 1_OTP寄存器)进行设置。

VDDIO OV阈值可通过OTP VDDIOOVTH_OTP[3:0]位字段(CFG_UVOV_2_OTP寄存器)进行配置。VDDIO UV阈值可通过OTP VDDIOUVTH_OTP[3:0]位字段(CFG_UVOV_6_OTP寄存器)进行配置。

VDDIO OV滤波可通过OTP寄存器OV_VDDIO_OTP位(CFG_DEGLITCH1_OTP寄存器)进行配置,而UV则可以通过UV_VDDIO_OTP[1:0]位字段(CFG_DEGLITCH1_OTP寄存器)进行配置。

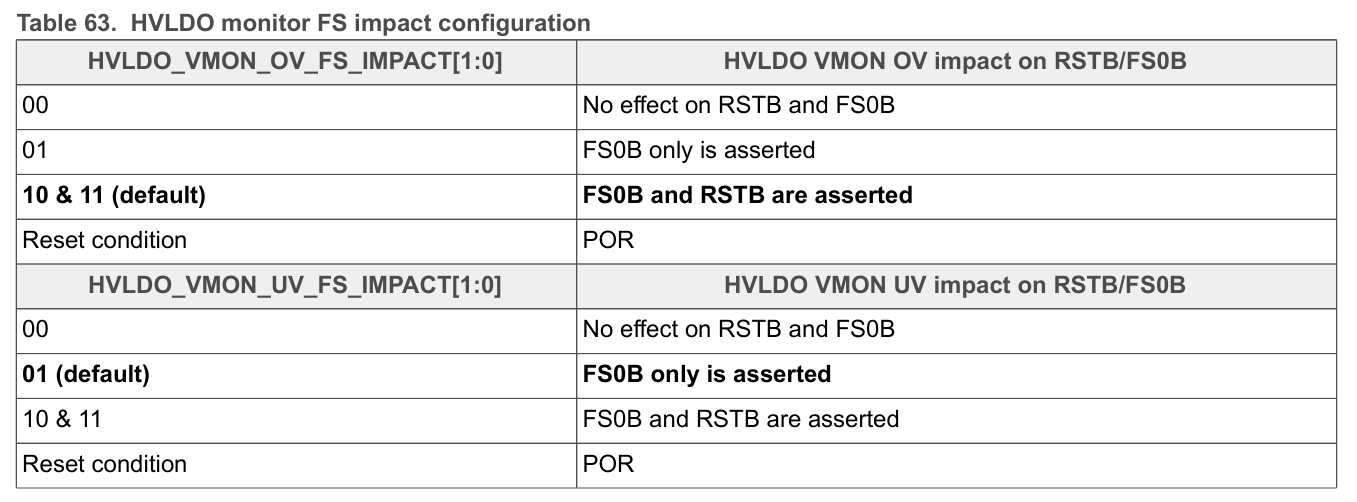

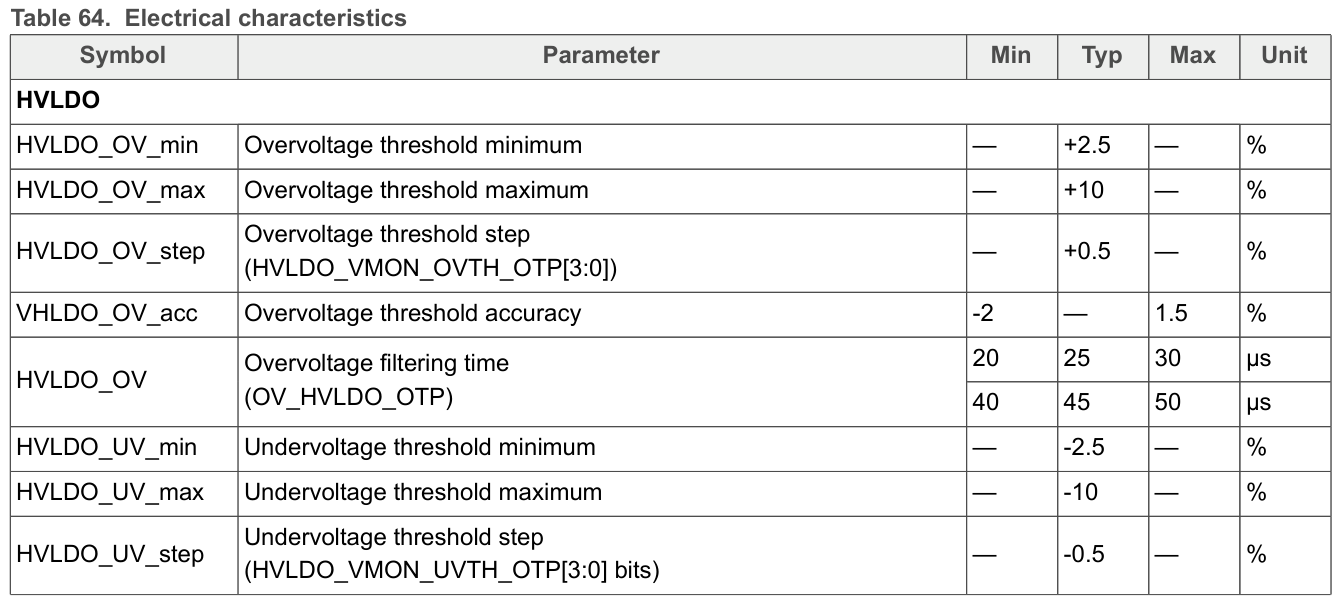

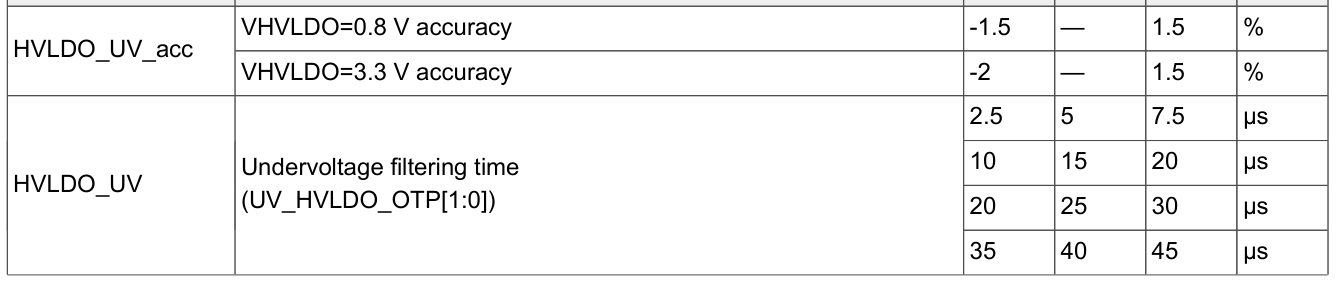

22.6.4 HVLDO监控

HVLDO电压监测器内部与HVLDO输出相连接。

HVLDO VMON可以通过HVLDO_MODE_OTP位(CFG_1_OTP寄存器)在两种模式下进行配置——开关模式和LDO模式。在开关模式下,参考电压内部跟踪Buck1 DVS DAC。开关模式只能使用0.8V。在LDO模式下,电压可以通过HVLDO_V_OTP位(CFG_1_OTP寄存器)设置为0.8V或3.3V。

在所有情况下,对RSTB和/或FS0B的故障安全反应由HVLDO_VMON_OV_FS_IMPACT[1:0]和HVLDO_VMON_UV_FS_IMPACT[1:0]位字段配置。这两个位字段都在FS_I_OVUV_SAFE_REACTION1寄存器中。

HVLDO VMON OV阈值可通过OTP HVLDO_VMON_OVTH_OTP[3:0]位字段(CFG_UVOV_9_OTP寄存器)进行配置。HVLDO VMON UV阈值可通过OTP HVLDO_VMON_UVTH_OTP[3:0]位字段(CFG_UVOV_9_OTP寄存器)进行配置。

HVLDO VMON OV滤波可通过OTP OV_HVLDO_OTP位和UV滤波可通过UV_HVLDO_OTP[1:0]位字段进行配置。两者都在CFG_DEGLITCH1_OTP寄存器中。

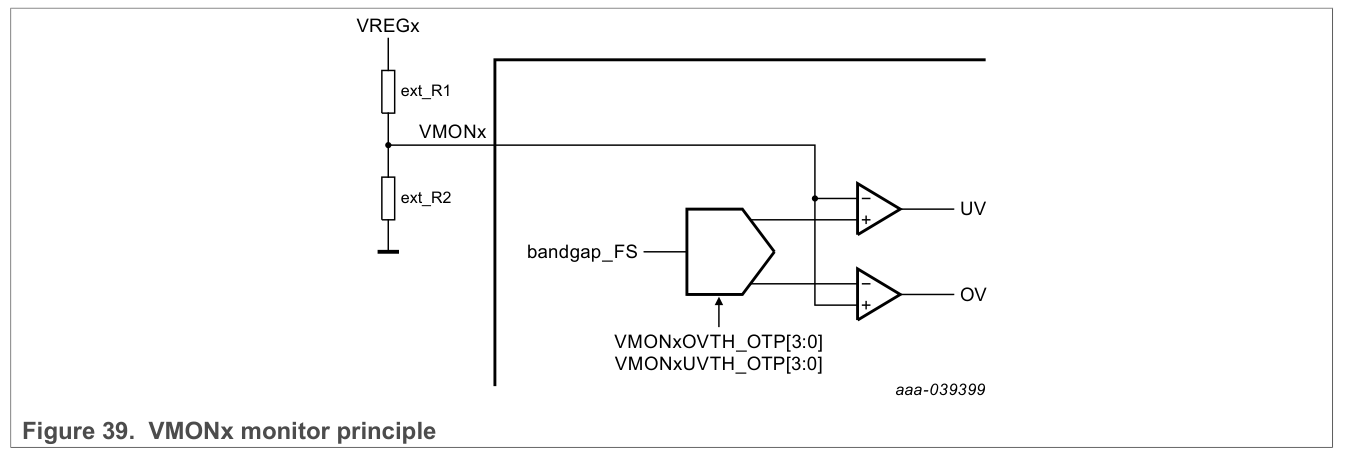

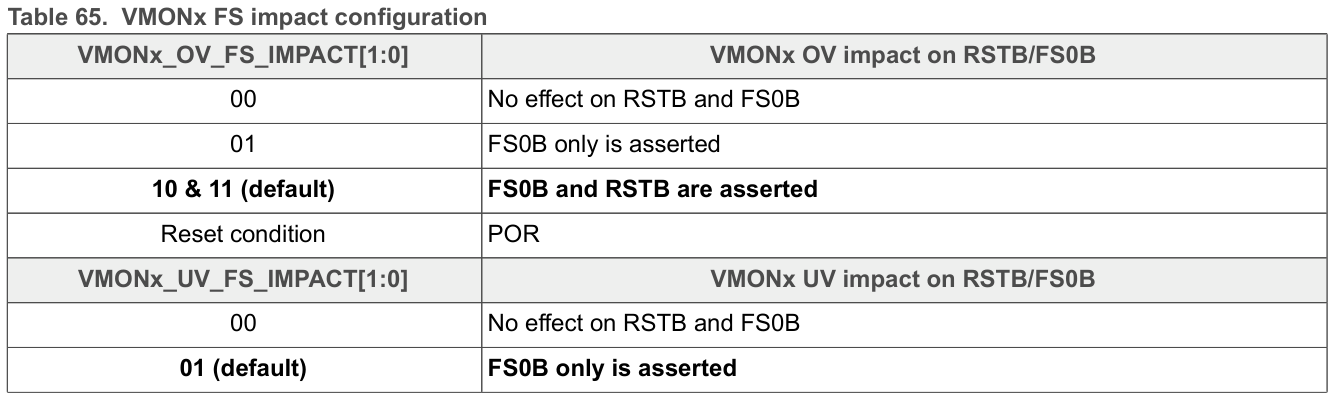

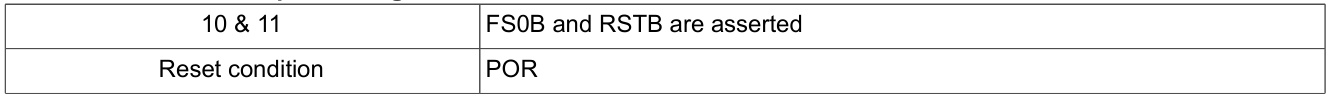

22.6.5 VMONx监控

VMONx输入引脚可以连接到VPRE、LDO1、LDO2、LDO3、BUCK1、BUCK2、BUCK3、BOOST或外部调节器。通过I2C在M_VMON_REGx寄存器中指定连接到VMONx引脚的调节器(因此,在发生过压检测时关闭哪个调节器),如果将外部调节器连接到VMONx引脚,则无法关闭该调节器,但是超压标志会报告给MCU,以便采取适当的措施。

在所有情况下,RSTB和/或FS0B上的故障安全反应都由FS_I_OVUV_SAFE_REACTION2寄存器中的VMONx_OV_FS_IMPACT[1:0]和VMONx_UV_FS_IMPACT[1:0]位字段配置。

连接到VMONx的外部电阻桥必须计算出一个0.8V的中点。使用±0.1%或更低的电阻精度。

VMONx OV阈值可以通过OTP VMONxOVTH_OTP[3:0]位域(CFG_UVOV_4_OTP和CFG_UVOV_5_OTP寄存器)进行配置。

VMONx UV阈值可以通过OTP VMONxUVTH_OTP[3:0]位域(CFG_UVOV_7_OTP和CFG_UVOV_8_OTP寄存器)进行配置。

VMONx OV滤波可以通过OTP OV_VMONx_OTP位以及UV可通过UV_VMONx_OTP[1:0]位域(CFG_DEGLITCHx_OTP寄存器)进行配置。

22.7 错误管理

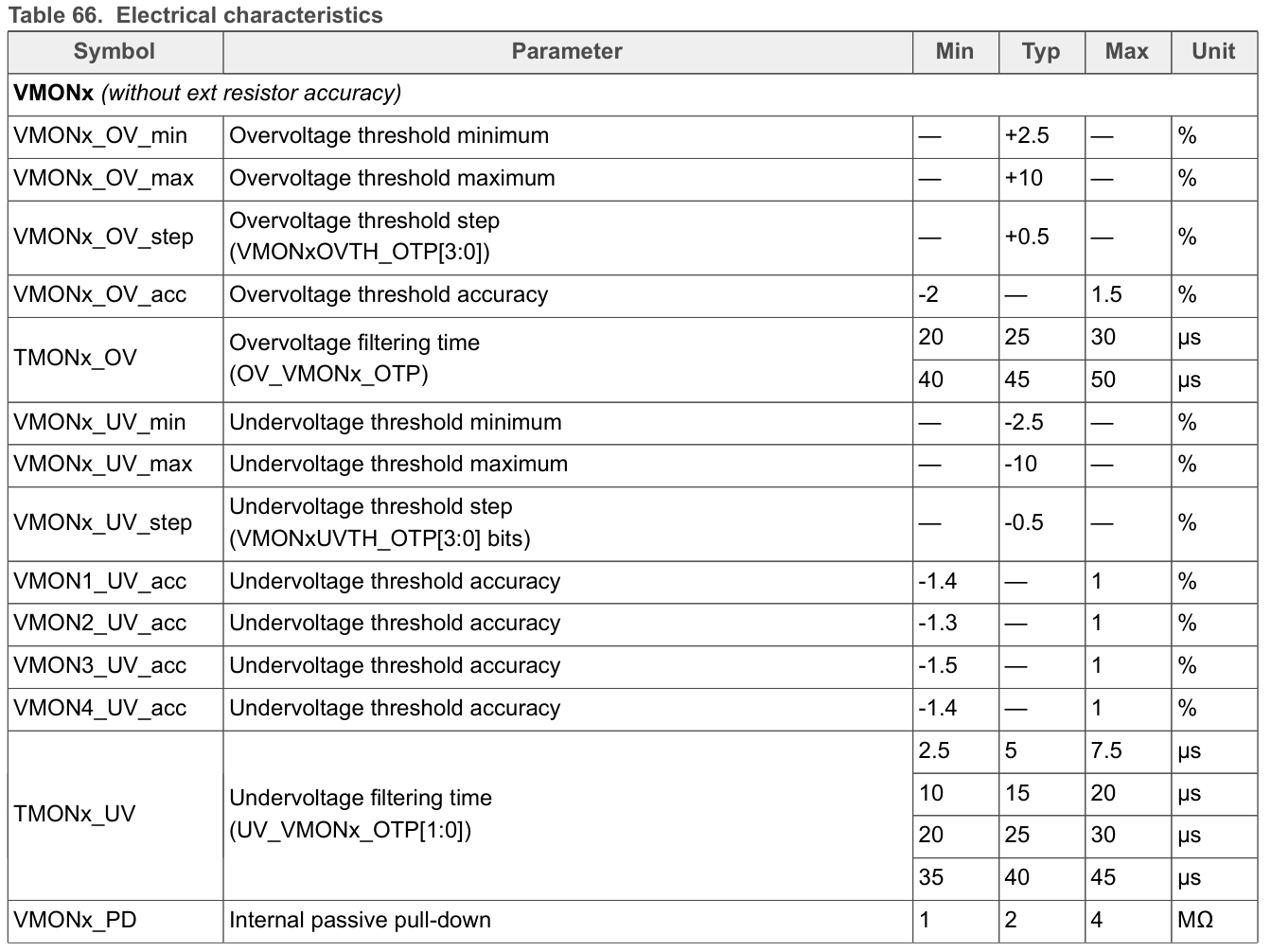

22.7.1 错误计数 Fault error counter

VR5510集成了一个可配置的故障错误计数器,用于计算与设备本身相关的故障数量以及由外部事件引起的故障数量。

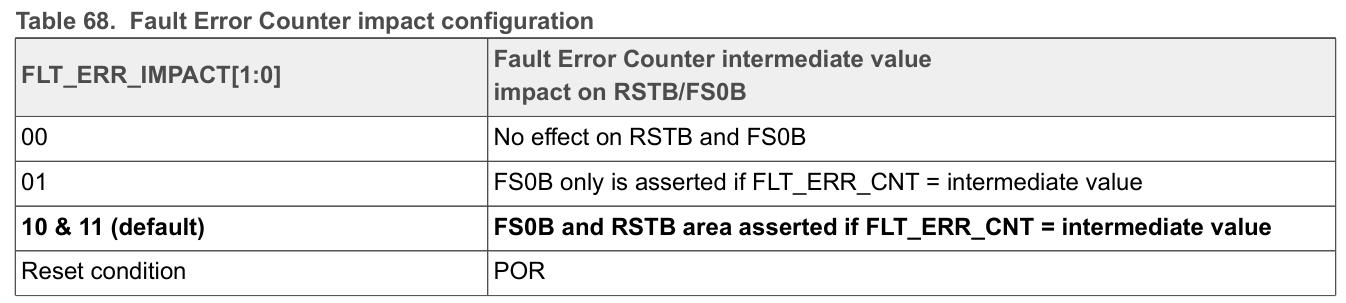

故障错误计数器在POR(上电复位)或从待机模式恢复后,从级别1开始。故障错误计数器的最终值用于进入深度失效安全模式。在INIT_FS阶段,可以通过FLT_ERR_CNT_LIMIT[1:0]位字段(FS_I_FSSM寄存器)进行配置,以设置该计数器的最大值。

FLT_ERR_CNT_LIMIT[1:0]表示故障错误计数器的最大值配置。

故障错误计数器有两个输出值:中间和最终。根据FLT_ERR_IMPACT[1:0]位字段(FS_I_FSSM寄存器)的配置,可以使用中间值来强制激活FS0B或生成RSTB脉冲。

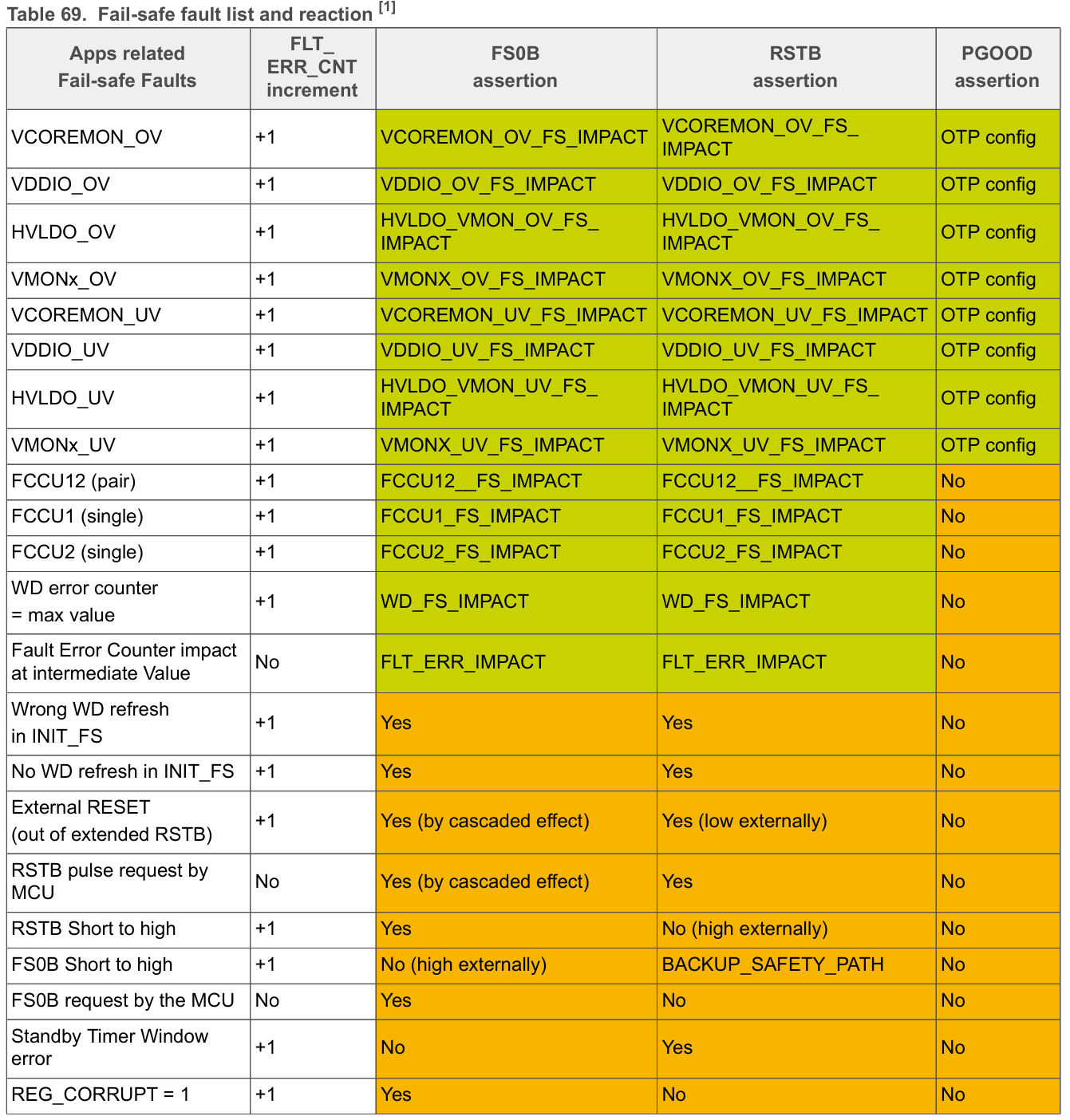

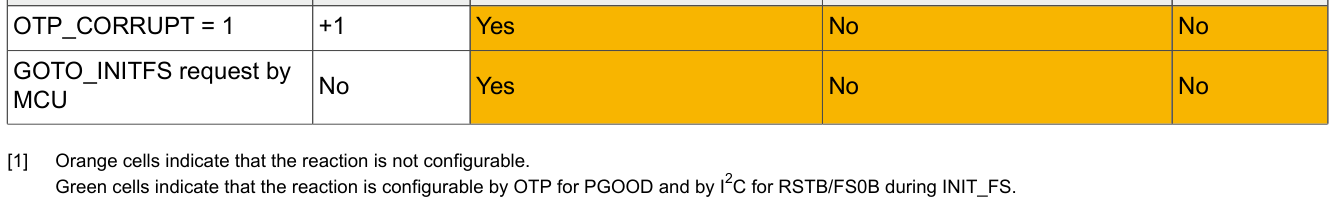

22.7.2 Fault source and reaction

在正常操作中,当FS0B和RSTB被释放时,如果VR5510故障安全状态机检测到故障,则会增加故障错误计数器。根据设备配置,表69列出了所有的故障及其对PGOOD、RSTB和FS0B引脚的影响。未配置为断言RSTB和FS0B的故障不会增加故障错误计数器。

在这种情况下,只有标志位可用于MCU诊断。当FS0B被断言时,每次WD错误计数器达到最大值时,故障错误计数器将继续递增+1。

如果RSTB2PGOOD_OTP = 0,则RSTB和PGOOD引脚独立工作(参见表49)。如果RSTB2PGOOD_OTP = 1(默认配置),则RSTB和PGOOD引脚同时工作,并且除了外部检测到的RSTB故障之外,所有断言RSTB的故障也会断言PGOOD。

22.8 PGOOD, RSTB, FS0B, STBY

为了确保最安全的状态,三个安全输出引脚(PGOOD、RSTB、FS0B)按照优先级进行层次化排序。

- PGOOD具有第一优先级。如果PGOOD被断言,则RSTB和FS0B也会被断言。

- RSTB具有第二优先级。如果RSTB被断言,则FS0B会被断言,但可能不会断言PGOOD。

- FS0B具有第三优先级。如果FS0B被断言,则RSTB和PGOOD可能不会被断言。

RSTB的释放由故障安全状态机管理,并取决于PGOOD的释放和ABIST1的执行。将电压监测分配给PGOOD和ABIST1以确定何时释放RSTB。此配置由OTP完成。

使用STBY输入引脚进入或退出待机模式。待机模式的进入由故障安全状态机处理,而退出则由主状态机处理。

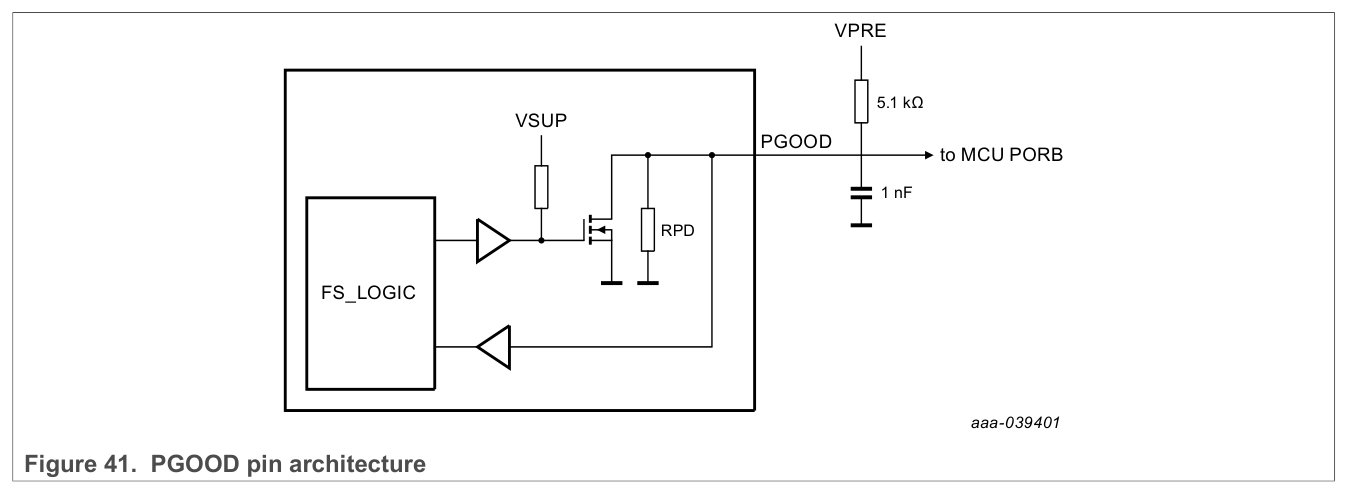

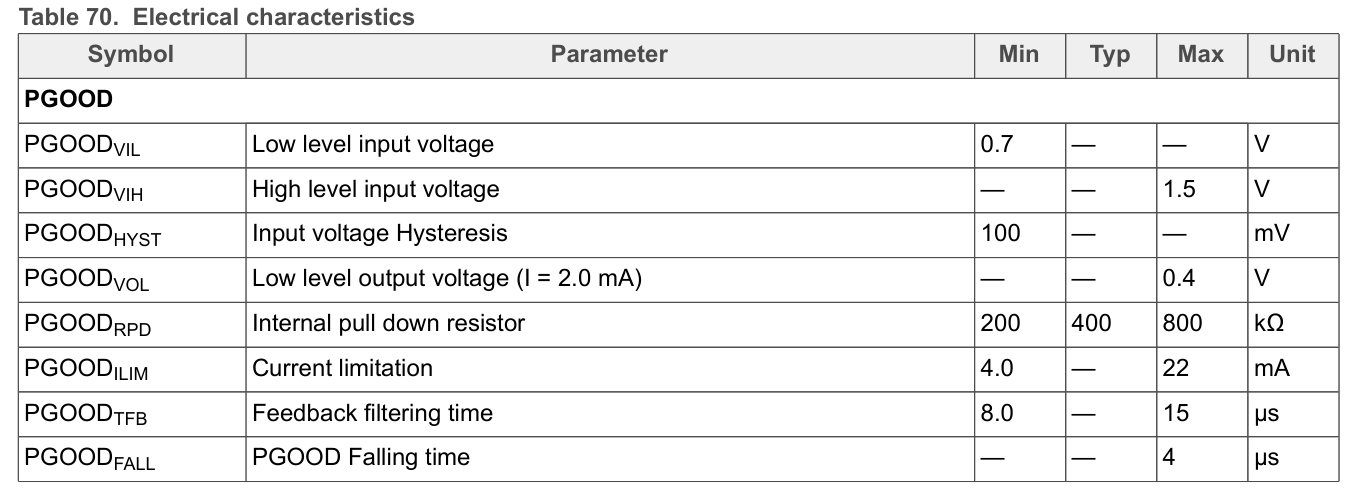

22.8.1 PGOOD

PGOOD是一个开漏输出,可以在应用中连接到MCU的PORB引脚。PGOOD需要外部上拉电阻连接到VDDIO或VPRE,并且需要一个滤波电容连接到GND以提高抗干扰能力。当设备关闭或关机时,内部下拉电阻RPD确保PGOOD保持低电平状态。

当PGOOD被断言为低电平时,RSTB和FS0B也会被断言为低电平。当发生FS_LOGIC故障时,通过对低侧MOS的栅极进行内部上拉来确保PGOOD保持在低电平状态。

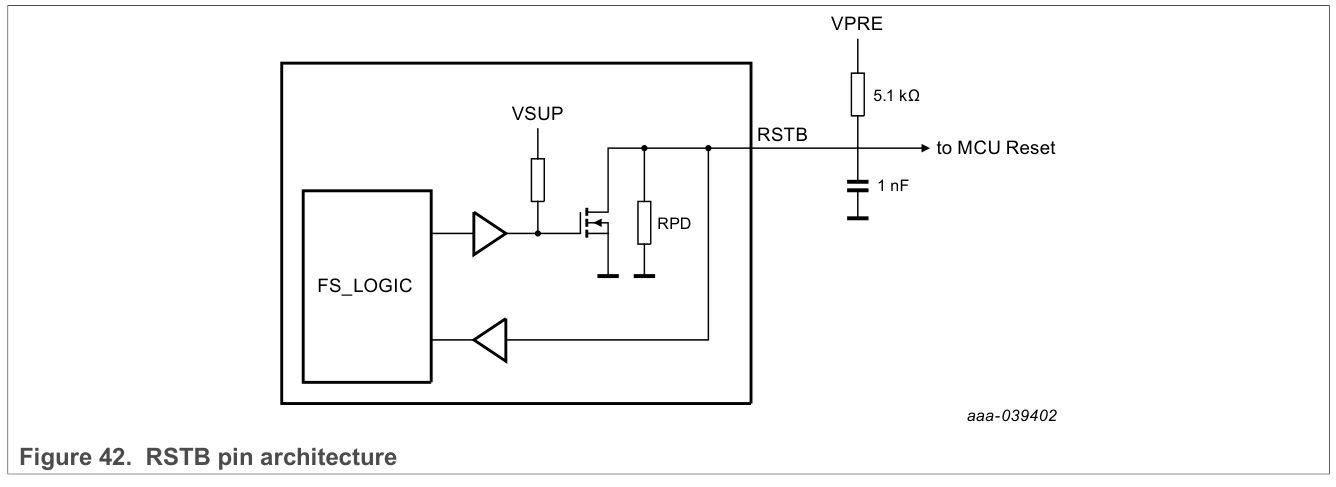

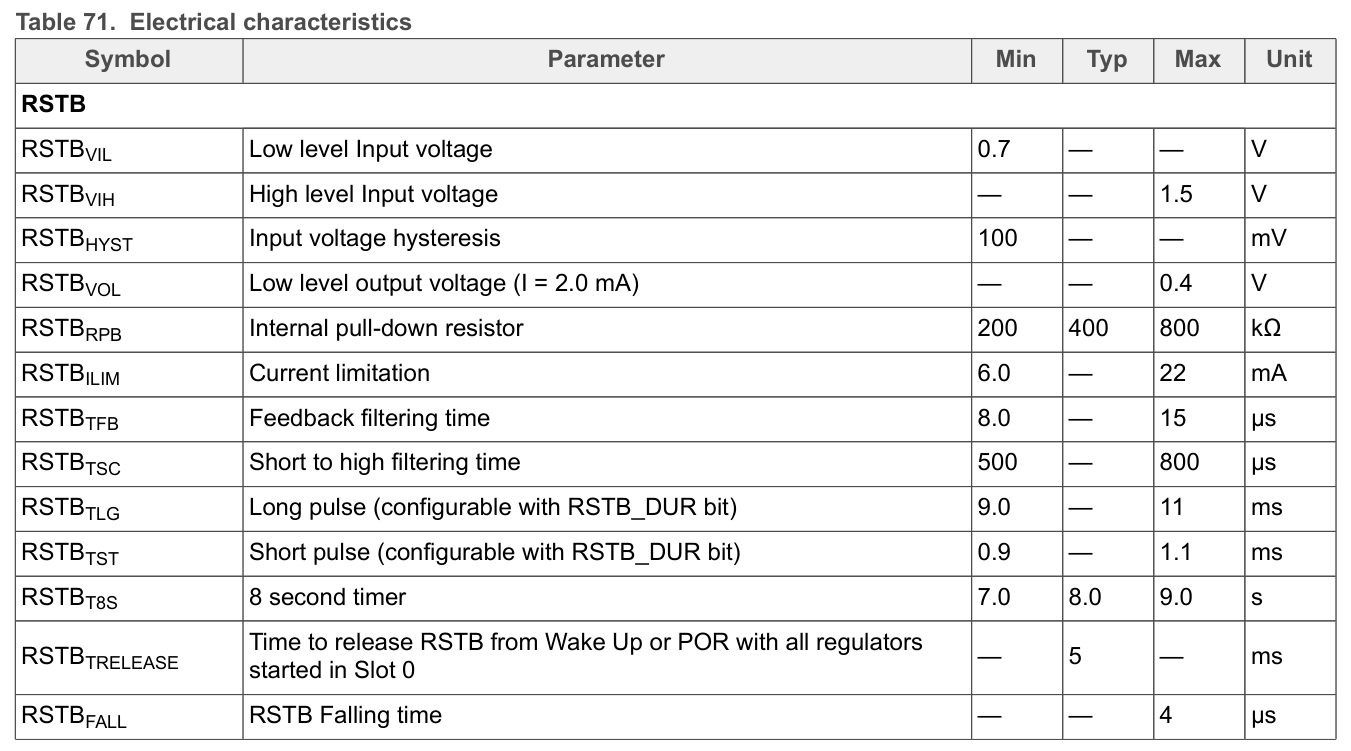

22.8.2 RSTB

RSTB是一个开漏输出,可以在应用中连接到MCU的复位引脚。RSTB需要外部上拉电阻连接到VDDIO或VPRE,并且需要一个接地滤波电容以提高抗干扰能力。当设备关闭或关机时,内部下拉电阻RPD确保RSTB保持低电平状态。

在INIT_FS阶段期间,RSTB的断言取决于设备配置。当RSTB被断言为低电平时,FS0B也会被断言为低电平。

通过对低侧MOS管门极上拉使得当发生FS_LOGIC故障时,RSTB保持在低电平状态。当RSTB连续保持低于 RSTBT8S 的时间时,设备将进入深度失效安全模式。

22.8.3 FS0B

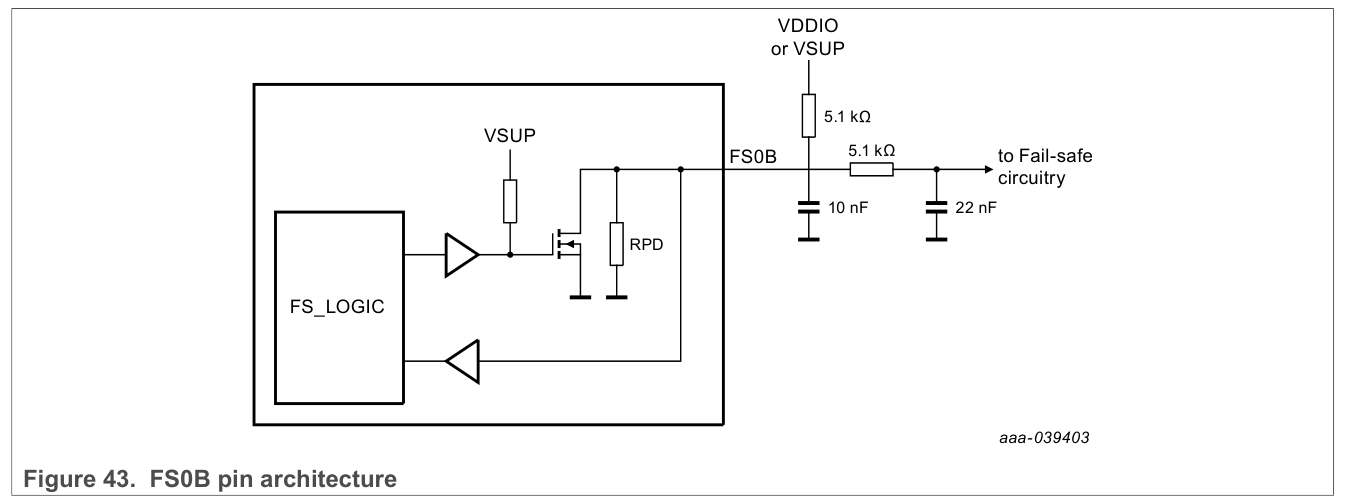

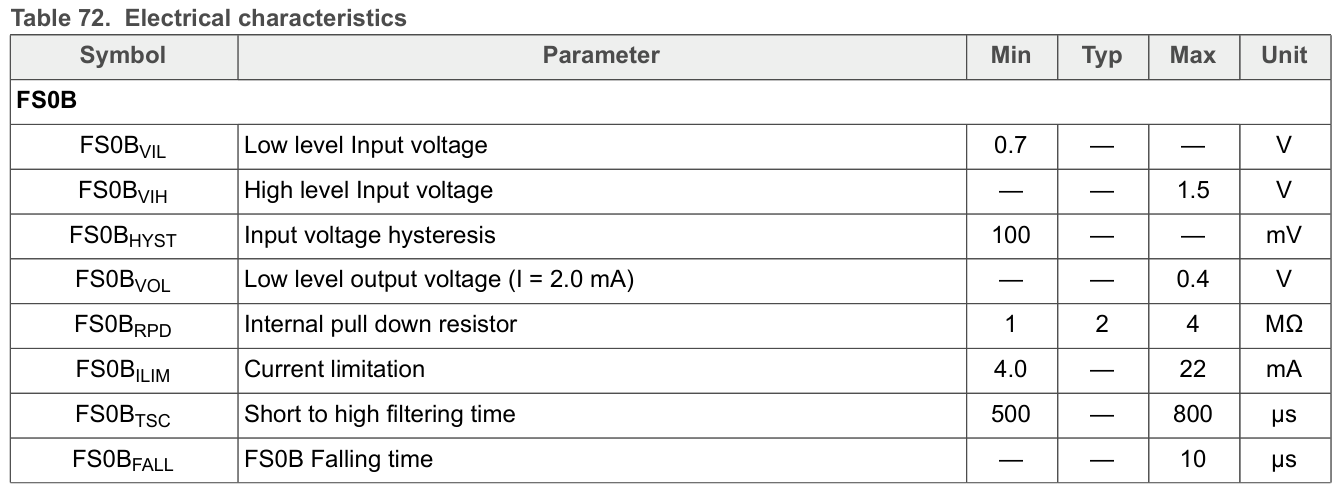

FS0B是一个开漏输出,可用于将系统转换为安全状态。当FS0B作为本地引脚时,需要外部上拉电阻连接到VDDIO或VSUP,并且需要10 nF的滤波电容连接到GND以提高抗干扰能力;当FS0B作为全局引脚时,还需要额外的RC网络来增强其对ESD GUN和ISO 7637瞬态脉冲的鲁棒性。

在待机或关机模式下,通过内部下拉电阻RPD确保FS0B保持低电平。在INIT_FS阶段期间,FS0B的断言取决于设备配置。通过在低侧MOS管门极上设置内部上拉电阻,确保当发生FS_LOGIC故障时,FS0B保持低电平。

22.8.4 FS0B release

当设备由于故障而将失效安全输出FS0B置为低电平时,必须在允许设备释放引脚之前验证三个条件。这些条件是:

-

LBIST_OK = ABIST1_OK = ABIST2_OK = 1

-

故障错误计数器= 0

-

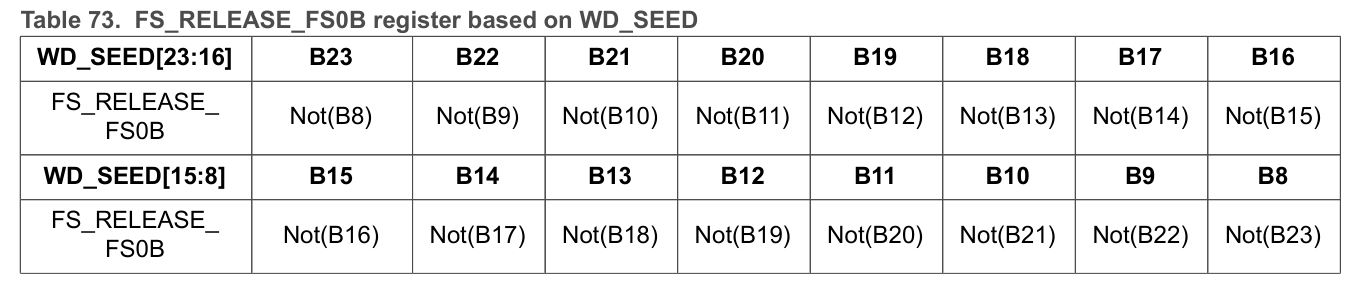

FS_RELEASE_FS0B寄存器填充有正在进行的WD_SEED位字段(FS_WD_SEED寄存器)的反转和补码。

22.8.5 STBY

STBY是一个输入,可以连接到应用程序中的MCU。通过STBY_POLARITY_OTP位(CFG_DEVID_OTP寄存器)可以编程待机输入引脚极性,以在待机模式下为高电平/正常模式下为低电平或在待机模式下为低电平/正常模式下为高电平。通过STBY_EN_OTP位(CFG_2_OTP寄存器)启用STBY功能。

根据STBY_SAFE_DIS_OTP位(CFG_2_OTP寄存器)设置,有两种可能的进入待机模式的路径:

- 仅使用STBY引脚转换的标准路径

- 使用I2C请求(在FS_SAFE_IOS寄存器中的STBY_REQ位)和STBY引脚转换的安全路径

如果使用安全路径,将使用一个由STBY_WINDOW_EN_OTP位(CFG_2_OTP寄存器)启用的待机定时窗口寄存器来定义I2C请求和STBY引脚转换之间的最大时间。

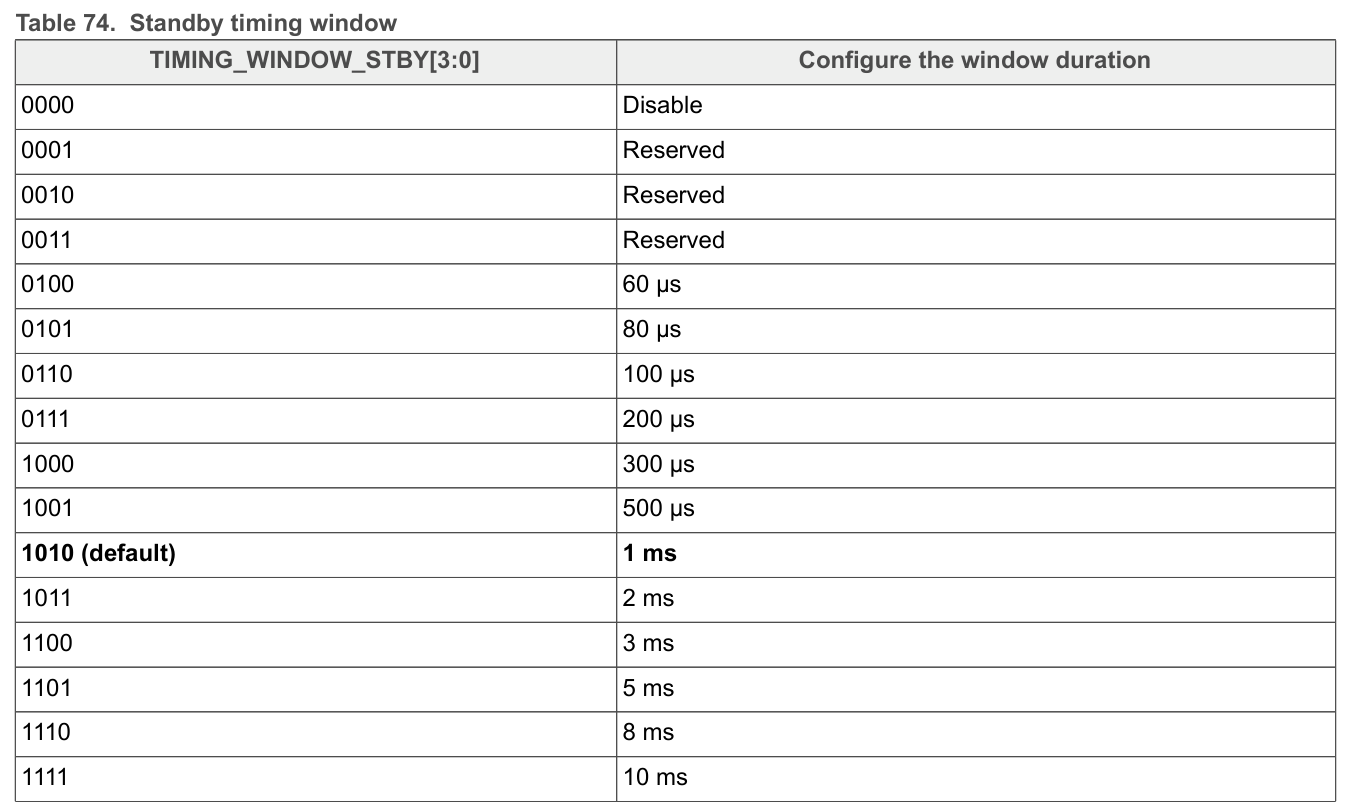

在INIT_FS阶段,通过TIMING_WINDOW_STBY[3:0]位字段(FS_I_SAFE_INPUTS寄存器),可以通过I2C对待机定时窗口进行配置。

22.9 Built-in self-test (BIST)

22.9.1 Logical BIST

故障安全状态机包括一个逻辑内置自检(LBIST),用于验证安全逻辑监控的正确功能。每次上电复位(POR)或从待机唤醒后,都会执行LBIST。如果LBIST失败,则释放RSTB和PGOOD信号,但FS0B保持低电平且无法释放。

LBIST_PASS标志(FS_DIAG_SAFETY寄存器)可通过I2C进行MCU诊断。典型的LBIST持续时间为3毫秒,最长LBIST持续时间为5毫秒。

22.9.2 Analog BIST

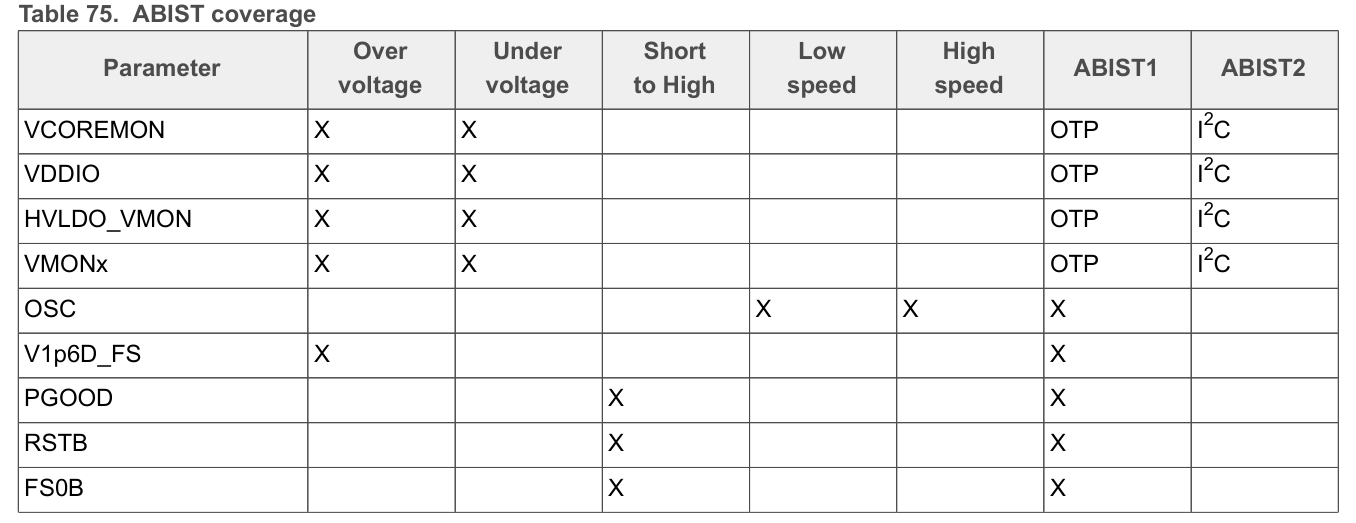

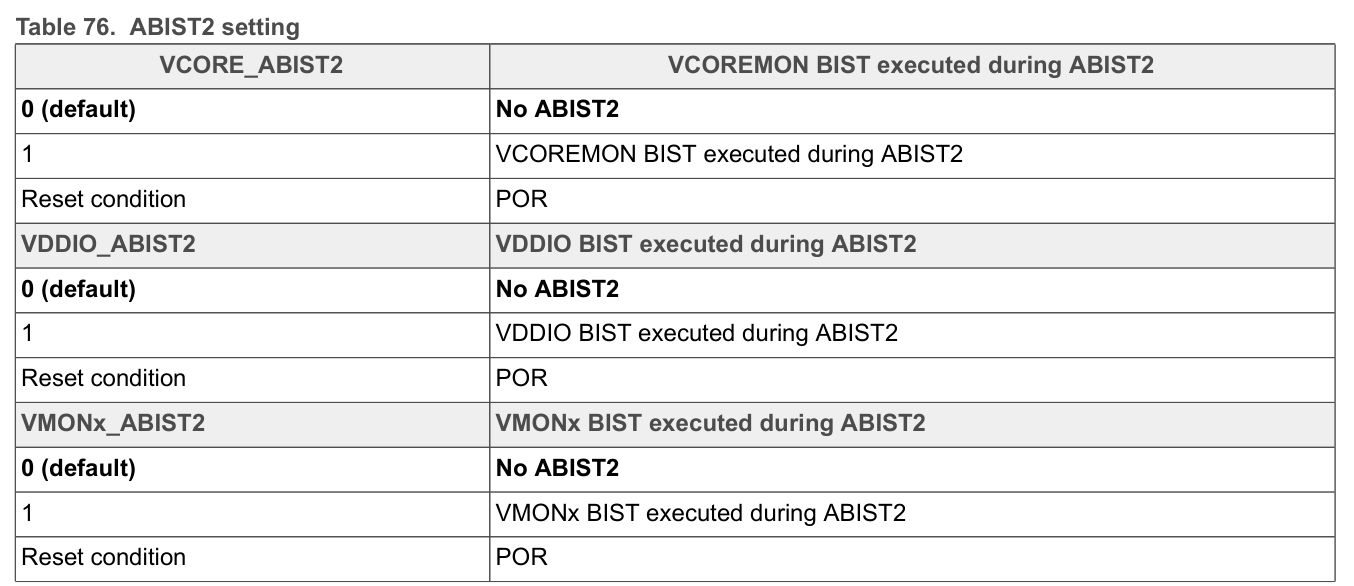

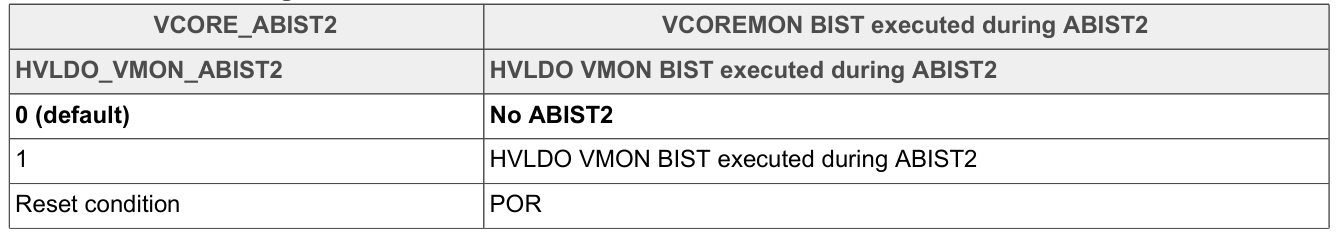

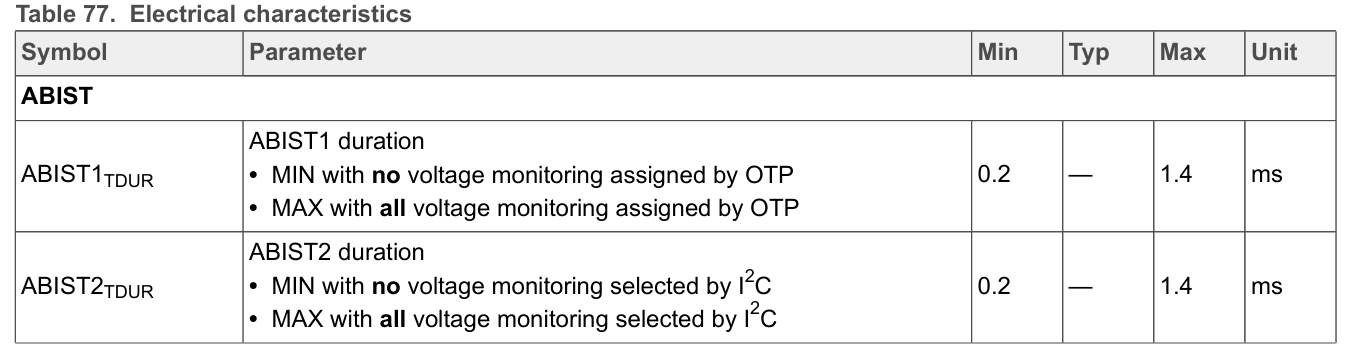

故障安全状态机包括两个模拟内置自检(ABIST),用于验证安全模拟监控的正确功能。每次上电复位(POR)或从待机唤醒后,都会自动执行ABIST1。

由OTP确定在ABIST1期间检查哪个调节器。在INIT_FS阶段之后,通过I2C执行ABIST2,并使用Vxxx_ABIST2位(FS_I_ABIST2_CTRL寄存器)。

如果ABIST失败,则释放RSTB和PGOOD信号,但FS0B保持低电平无法释放。

MCU诊断可以通过I2C获取FS_DIAG_SAFETY寄存器中的标志位ABIST1_OK和ABIST2_OK来进行诊断。

可用RSTB_DELAY_OTP位在ABIST1结束和RSTB/PGOOD释放之间添加5毫秒的延迟。

23. I2C通信

23.1 概述

VR5510使用I2C接口,遵循高速模式定义,最高传输速率为3.4 Mbit/s。I2C接口协议要求在多设备总线上寻址目标IC时需要一个设备地址。VR5510有两个设备地址:一个用于访问主逻辑,另一个用于访问故障安全逻辑。这两个I2C地址是通过OTP设置的。

I2C接口使用VDDIO作为主供电,并兼容1.8 V / 3.3 V输入供电。SCL和SDA引脚可以通过2.2 kΩ电阻拉到VDDIO上拉电压。更多的定时、图表和详细信息可以在NXP I²C规范UM10204 rev6中找到。

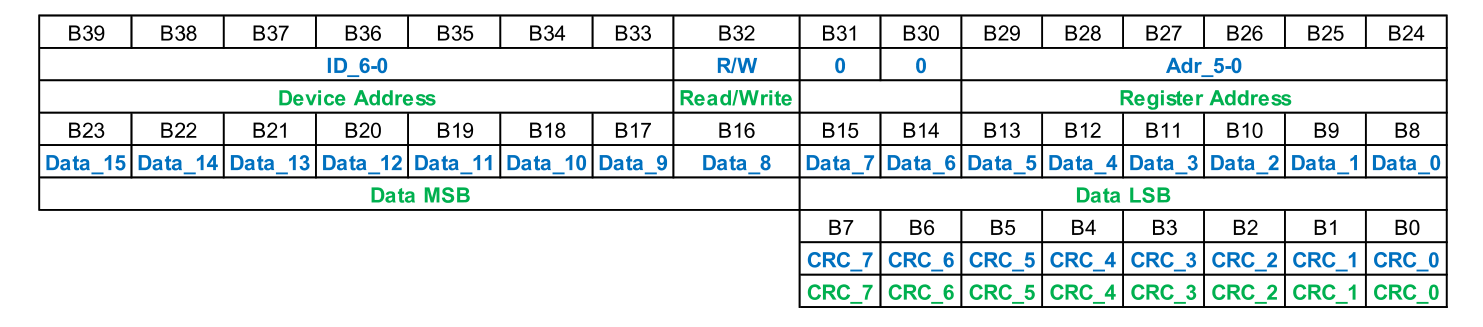

I2C消息排列:

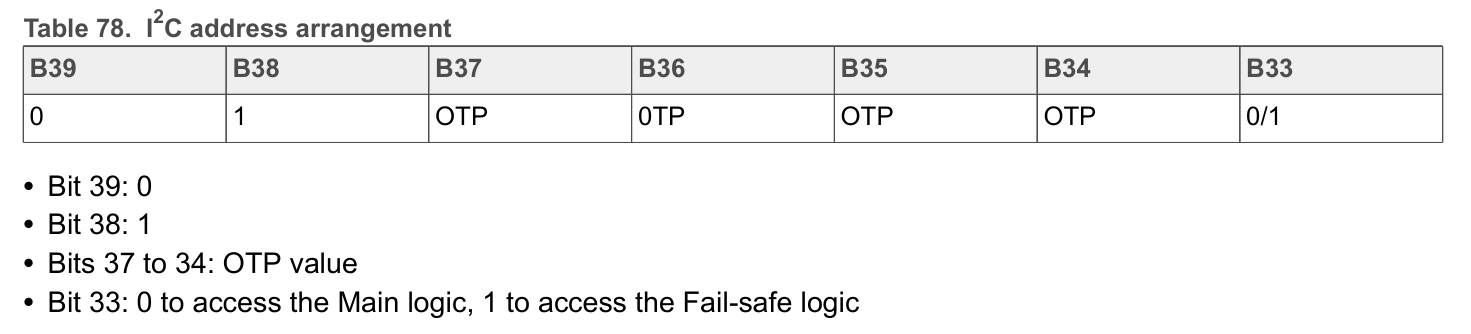

23.2 设备地址

VR5510有两个设备地址:一个用于访问主逻辑,另一个用于访问故障安全逻辑。设备地址是一个7位寄存器,可以使用I2CDEVADDR_OTP位字段(CFG_I2C_OTPregister)进行设置。

I2C地址的排列如下:

23.3 循环冗余校验

每个I2C写入和读取命令都需要进行8位CRC校验。循环冗余检查的计算是基于二进制多项式除法的数学原理得出的。所使用的CRC多项式为x8+x4+x3+x2+1(或0x1D),SEED种子值为0xFF。

CRC_7 = XOR (B38, B35, B32, B31, B24, B23, B22, B20, B17, B13, B12, B11, 1, 1, 1)

CRC_6 = XOR (B37, B34, B23, B22, B21, B19, B16, B12, B11, B10, 1, 1)

CRC_5 = XOR (B39, B36, B33, B30, B29, B22, B21, B20, B18, B15, B11, B10, B9, 1, 1, 1)

CRC_4 = XOR (B39, B38, B35, B32, B29, B28, B21, B20, B19, B17, B14, B10, B9, B8, 1, 1, 1, 1)

CRC_3 = XOR (B37, B35, B34, B32, B28, B27, B24, B23, B22, B19, B18, B17, B16, B12, B11, B9, B8, 1, 1, 1,

1)

CRC_2 = XOR (B39, B38, B36, B35, B34, B33, B32, B27, B26, B24, B21, B20, B18, B16, B15, B13, B12 B10,

B8, 1,1,1,1,1,1,1)

CRC_1 = XOR (B37, B34, B33, B26, B25, B24, B22, B19, B15, B14, B13, B9, 1, 1, 1)

CRC_0 = XOR (B39, B36, B33, B32, B25, B24, B23, B21, B18, B14, B13, B12, B8, 1, 1, 1, 1)

用I2C通讯计算CRC的提示:

I2C write command: DEVADDR-W + REG_ADDR + MASTER_DATA_MSB + MASTER_DATA_LSB + CRC

🡺 CRC is calculated with bits from B39 to B8

I2C read sequence: DEVADDR-W + REG_ADDR + I2C_REPEAT_START + DEVADDR-R +

SLAVE_DATA_MSB + SLAVE_DATA_LSB + CRC

🡺 CRC is calculated with bits from DEVADDR-R + REG_ADDR + SLAVE_DATA_MSB + SLAVE_DATA_LSB

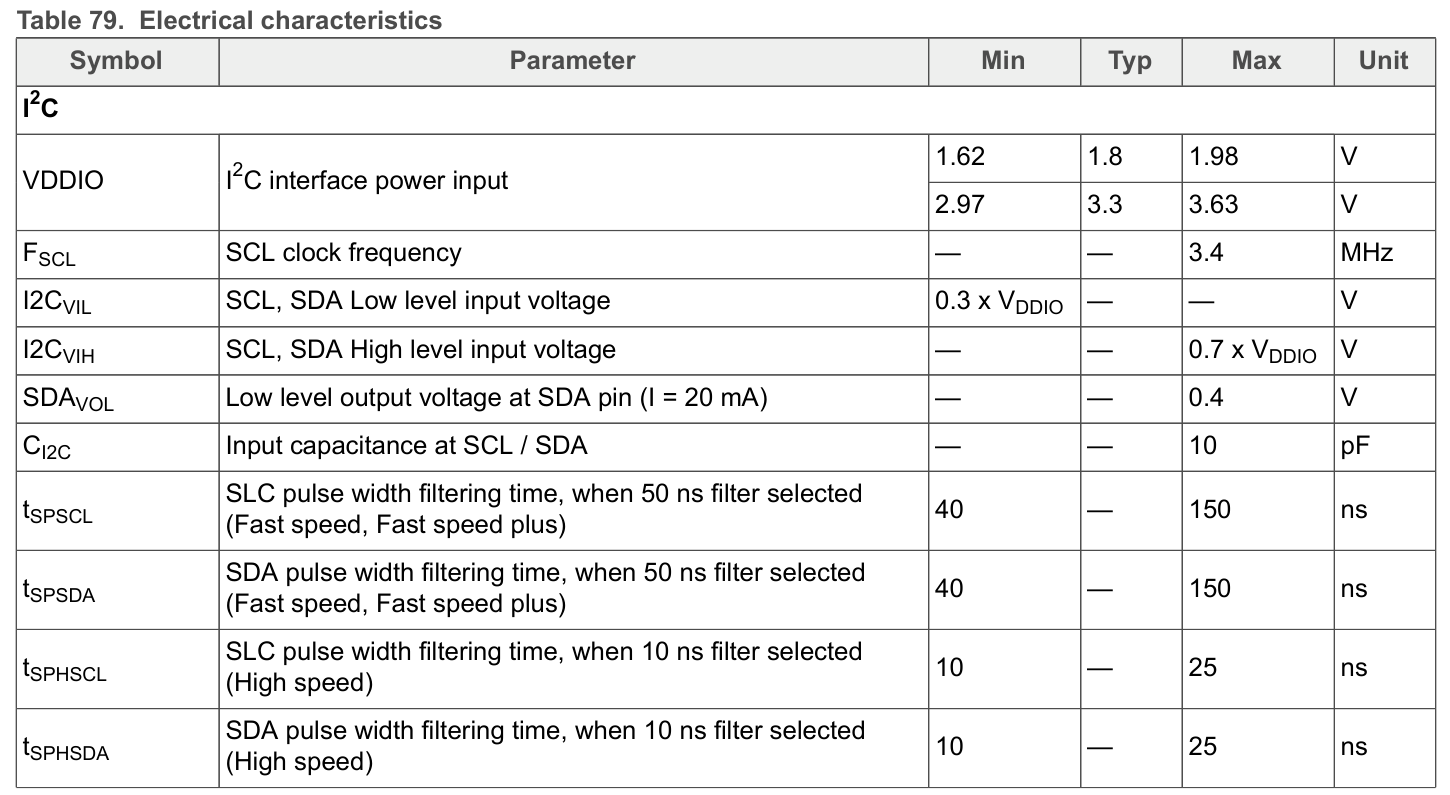

23.4 电气特性

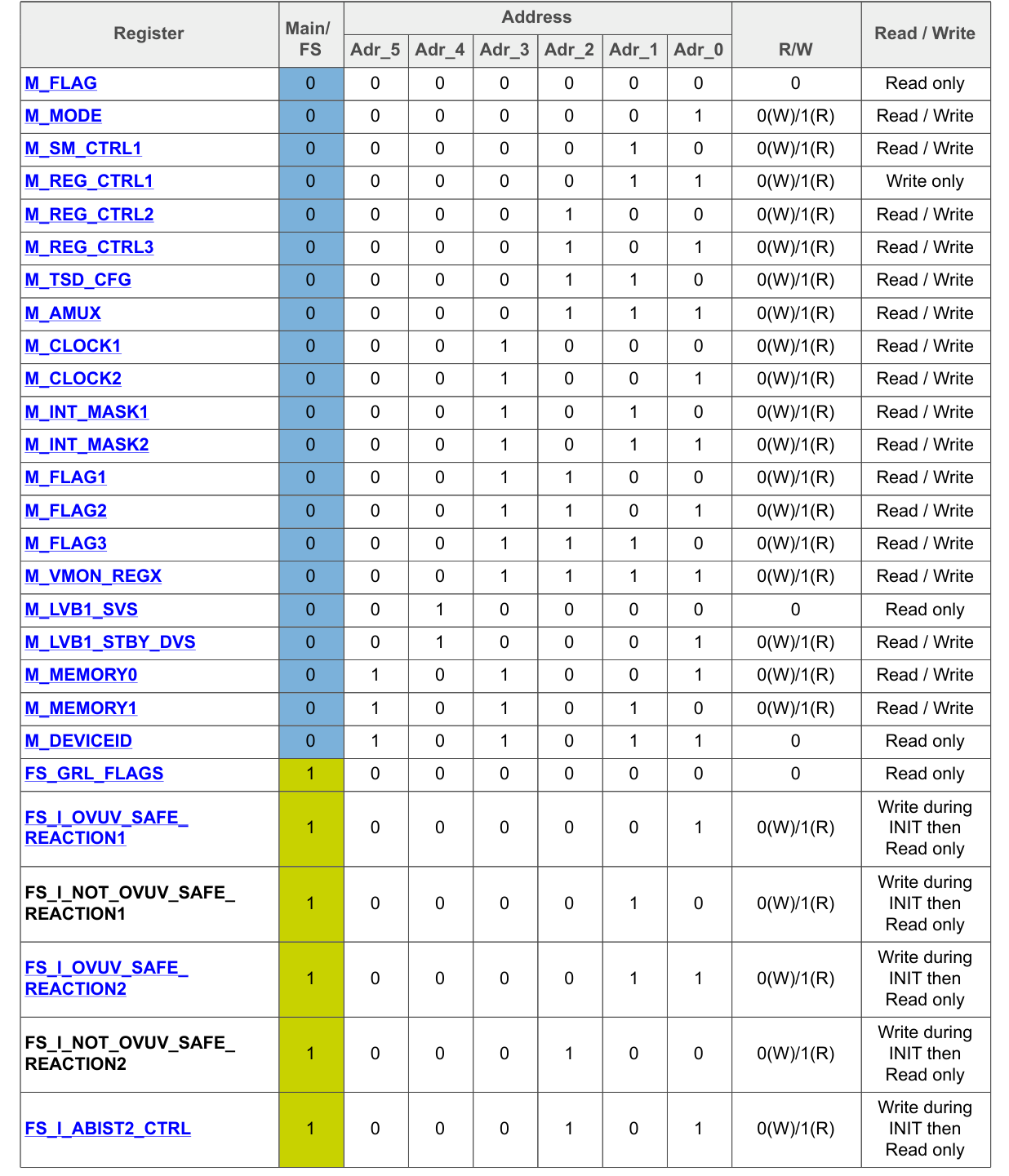

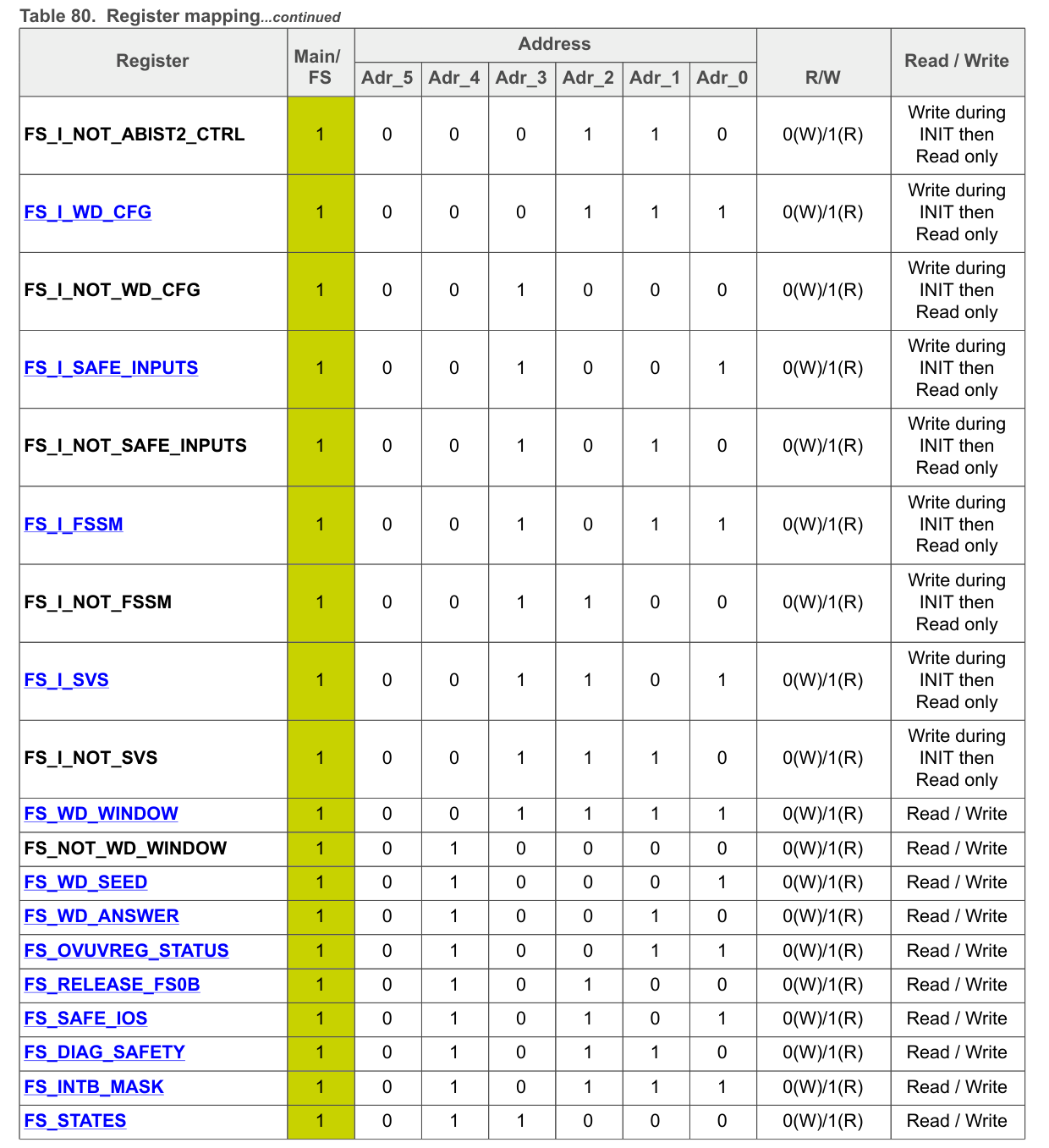

24. 寄存器映射表Register Mapping

1606

1606

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?