此系列记录FPGA在学校的学习过程。

FPGA系列

需要用到的软硬件:

软件:

硬件:

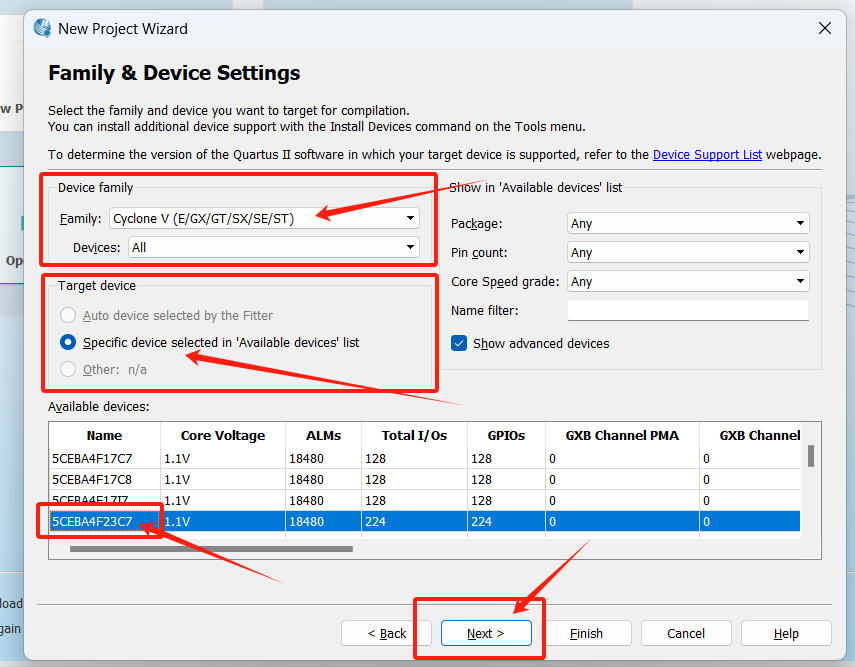

5CEBA4F23C7芯片

开始新建一个工程

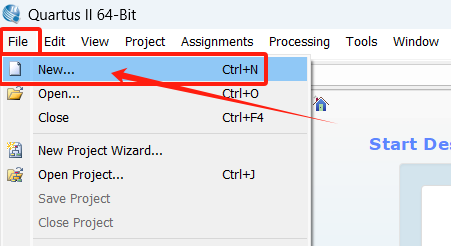

首先打开FPGA的软件

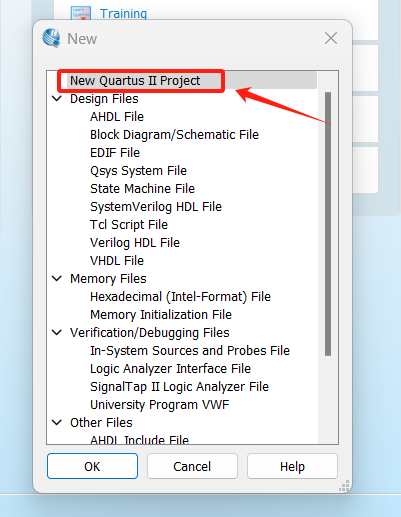

双击“New Quartus II Project”

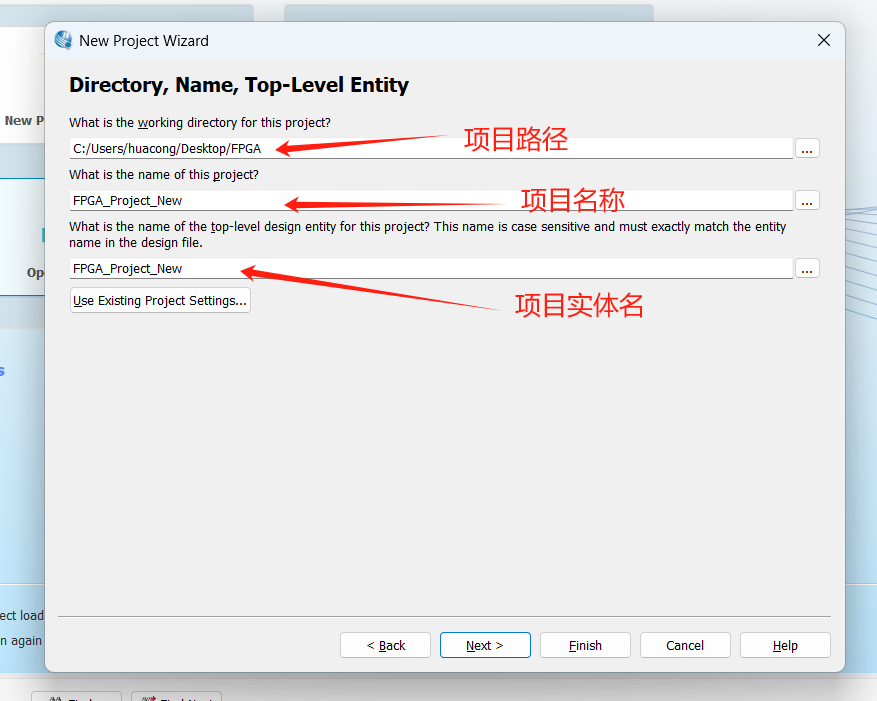

“NEXT”

填入项目路径,名称,实体名

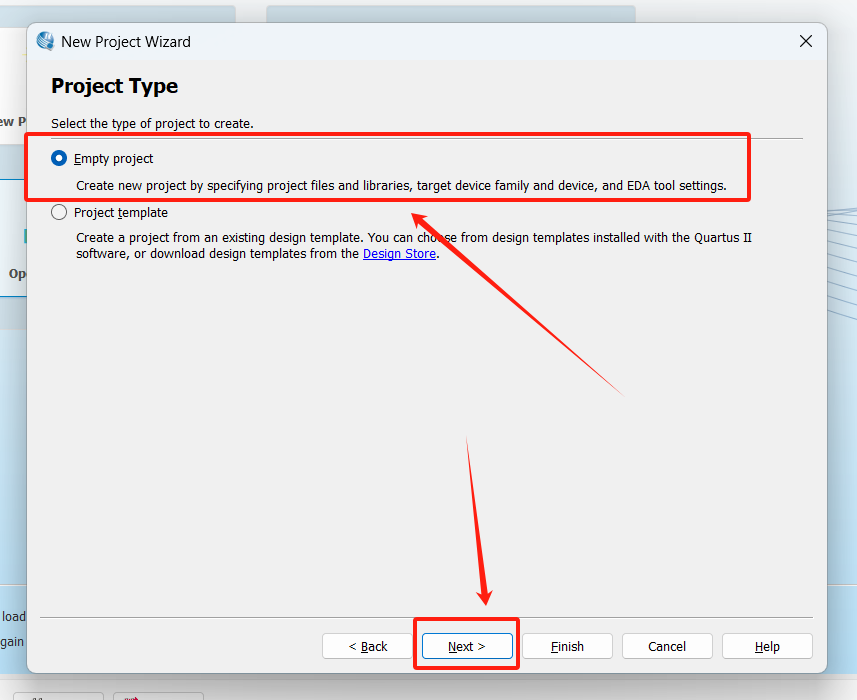

创建一个空项目

可以添加文件,但是我们暂时不添加

开始选择开发板上的芯片

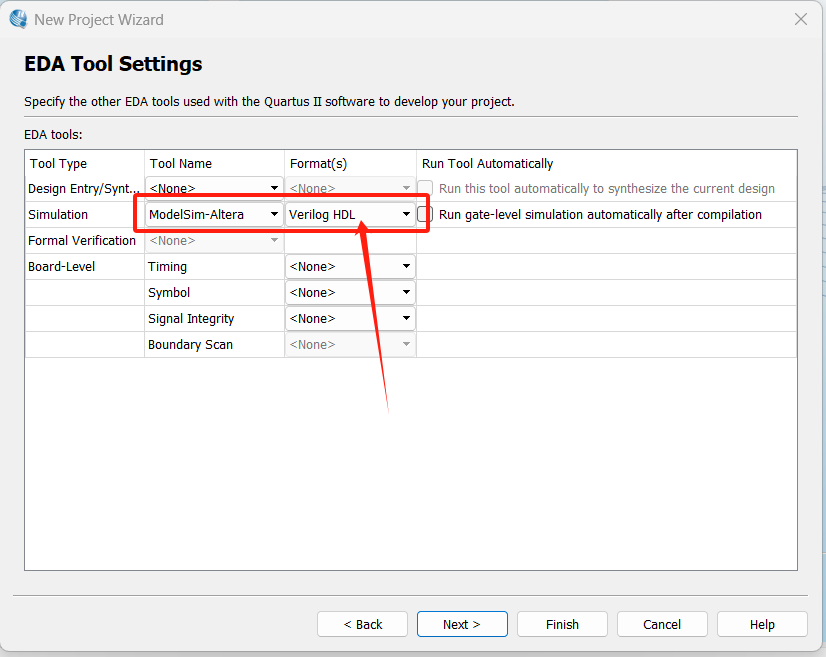

这里使用的是Verilog HDL语言

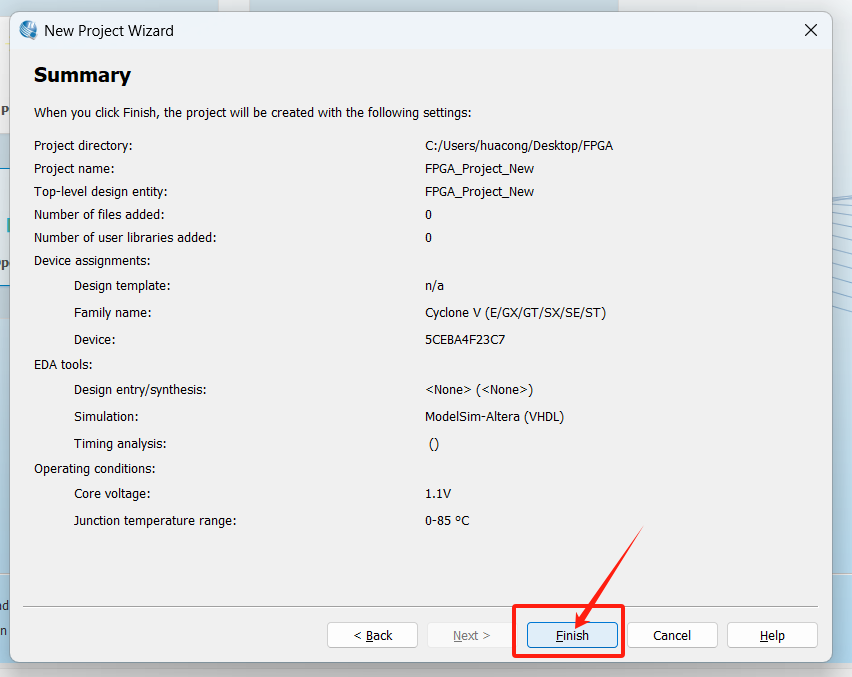

Finsh,完成创建

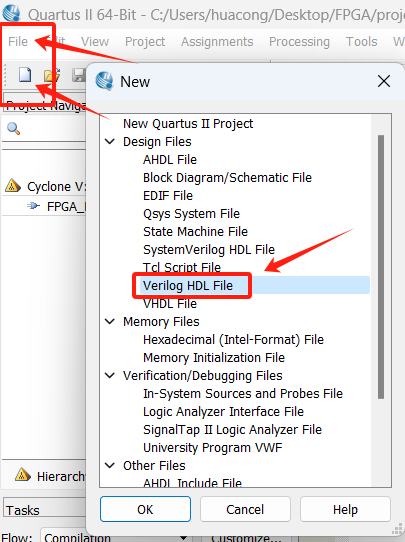

创建Verilog HDL文件(.V文件)

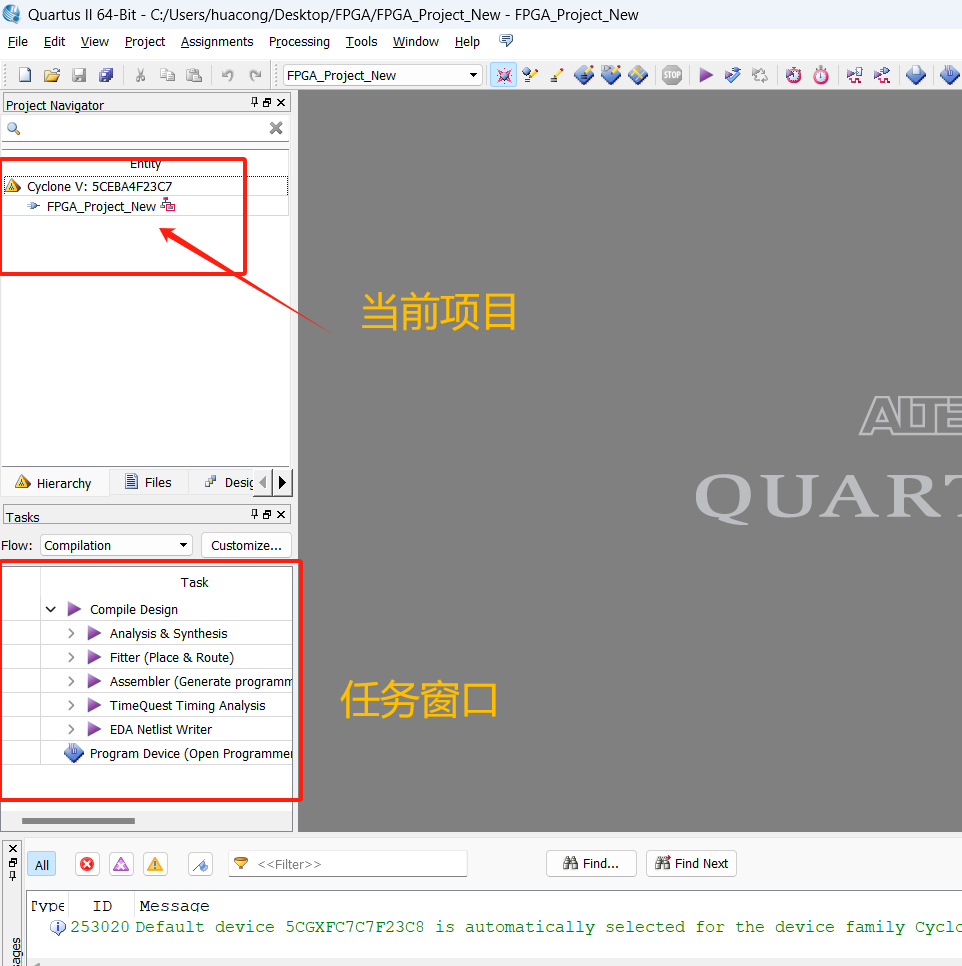

1.窗口界面

2.开始新建一个.v空白文件

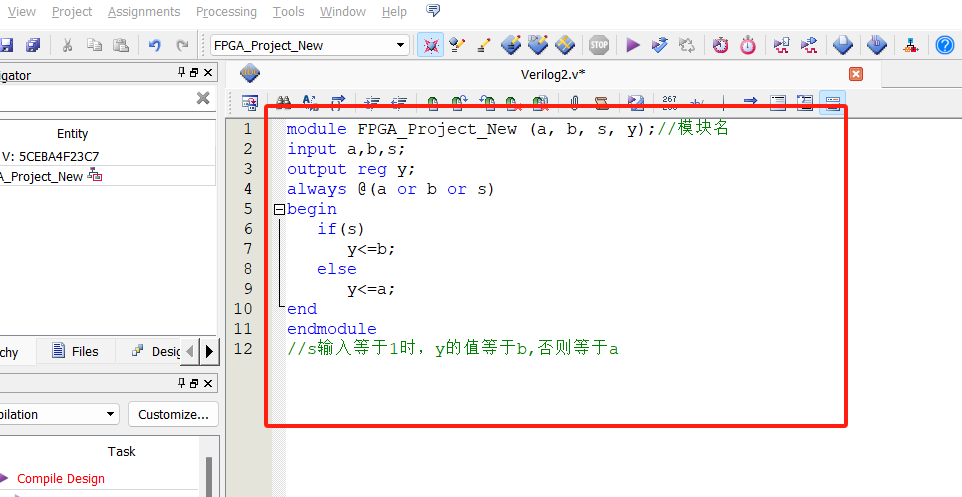

在新建的文件里面添加测试程序

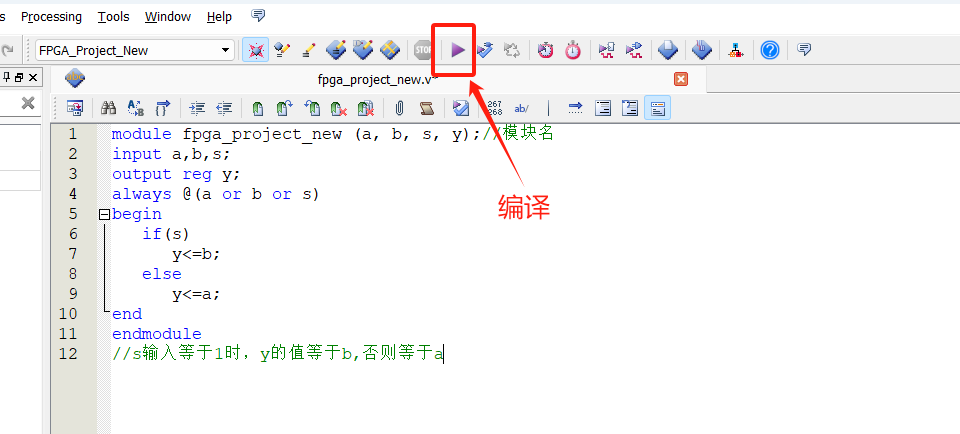

//FPGA 使用:Verilog HDL语言

module FPGA_Project_New (a, b, s, y);//模块名

input a,b,s;

output reg y;

always @(a or b or s)

begin

if(s)

y<=b;

else

y<=a;

end

endmodule

//s输入等于1时,y的值等于b,否则等于a

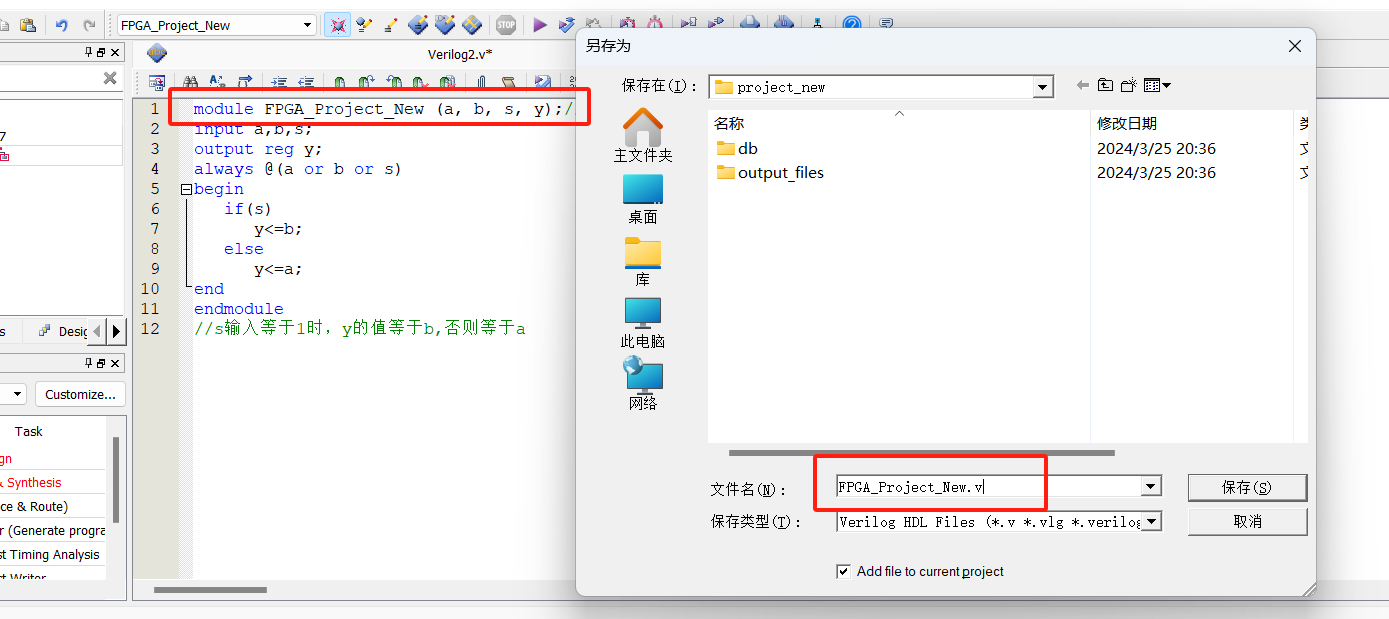

保存一下,名字要和模块名一样

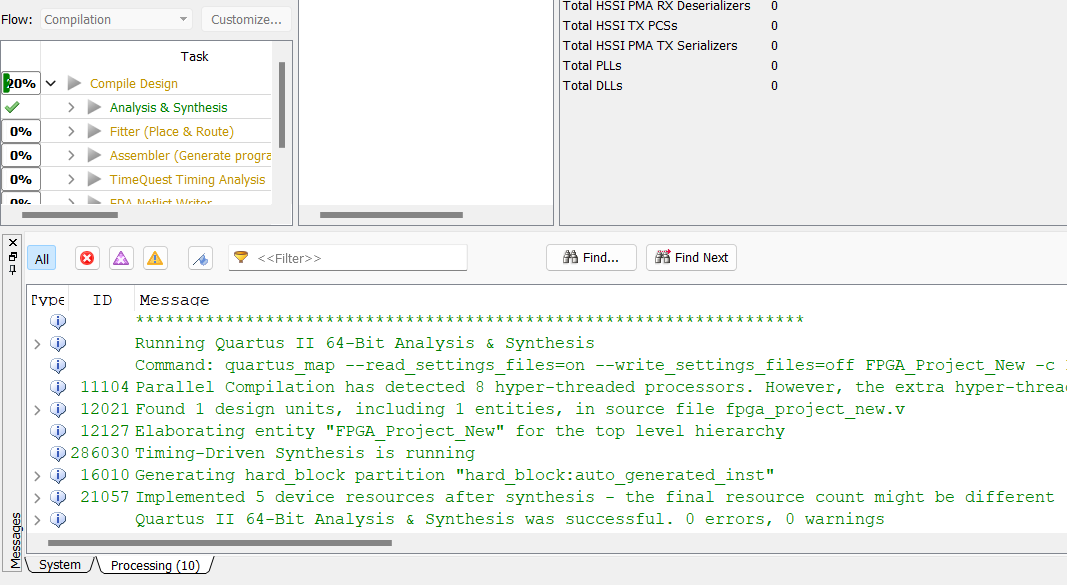

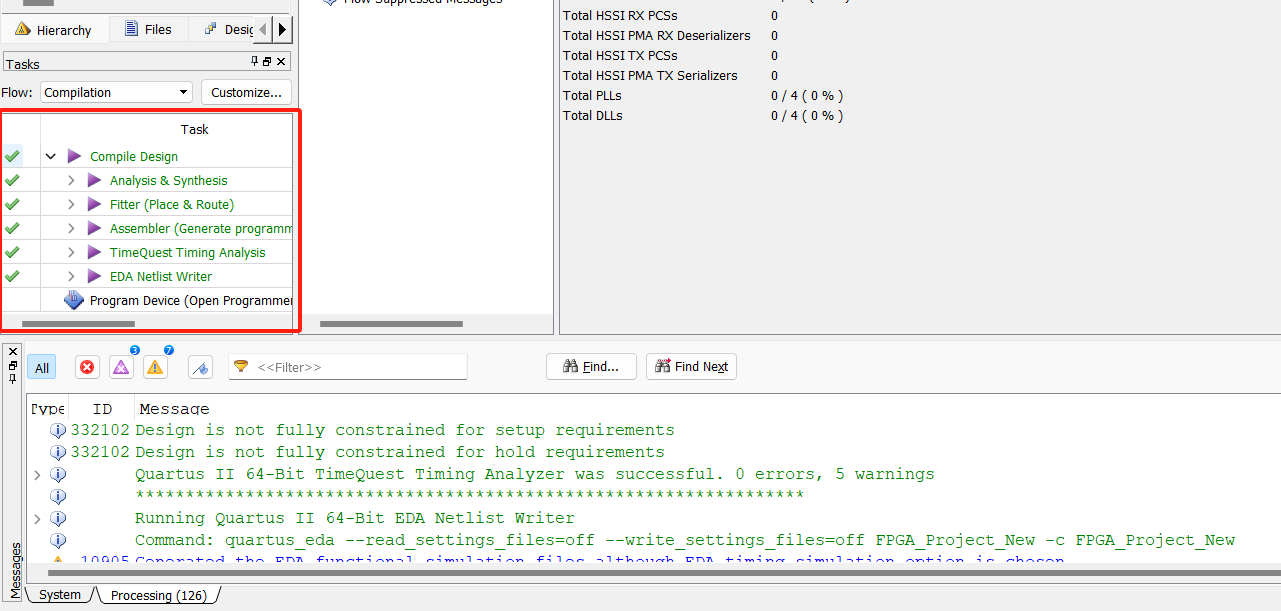

编译

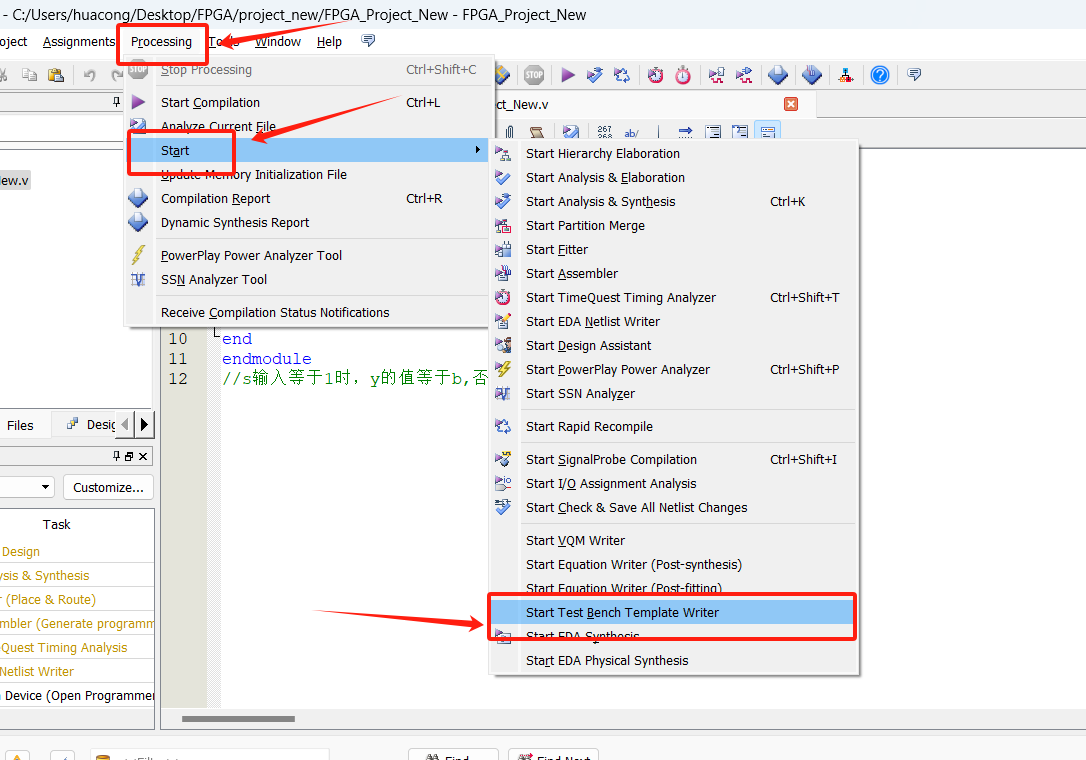

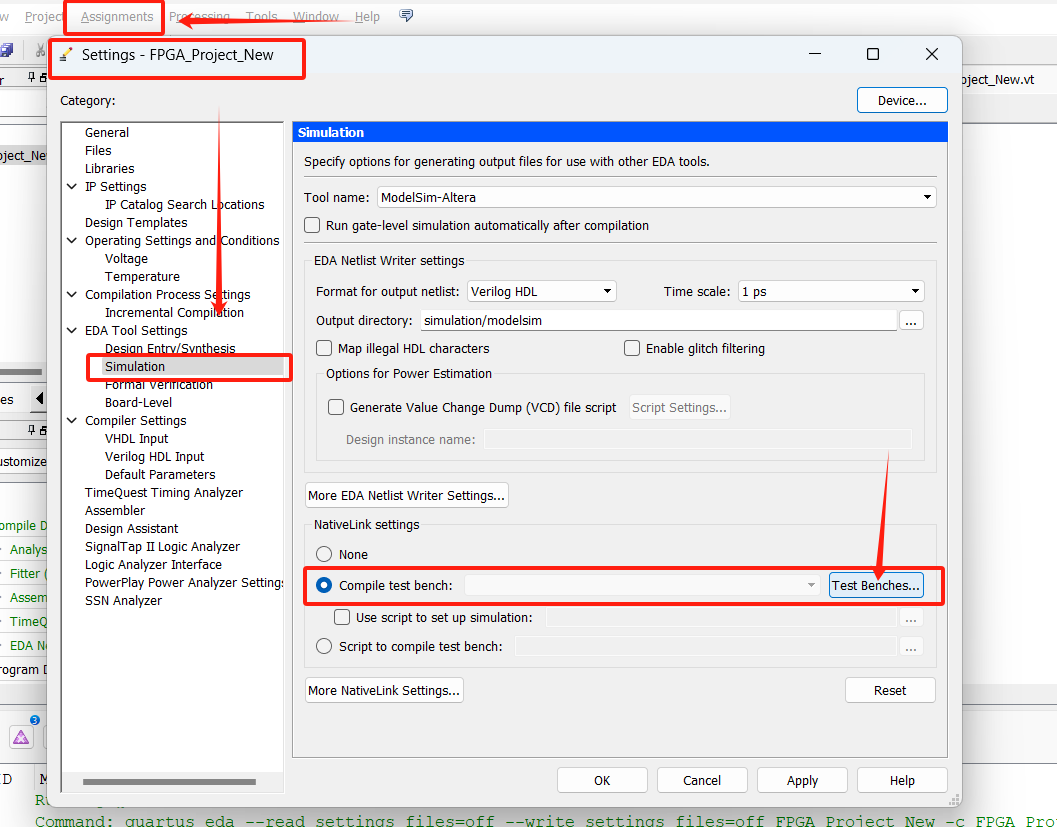

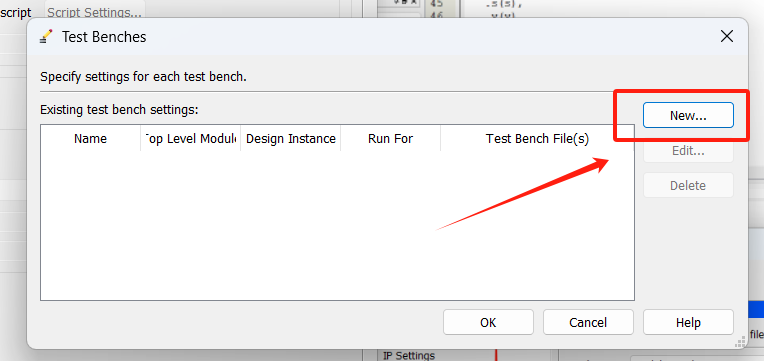

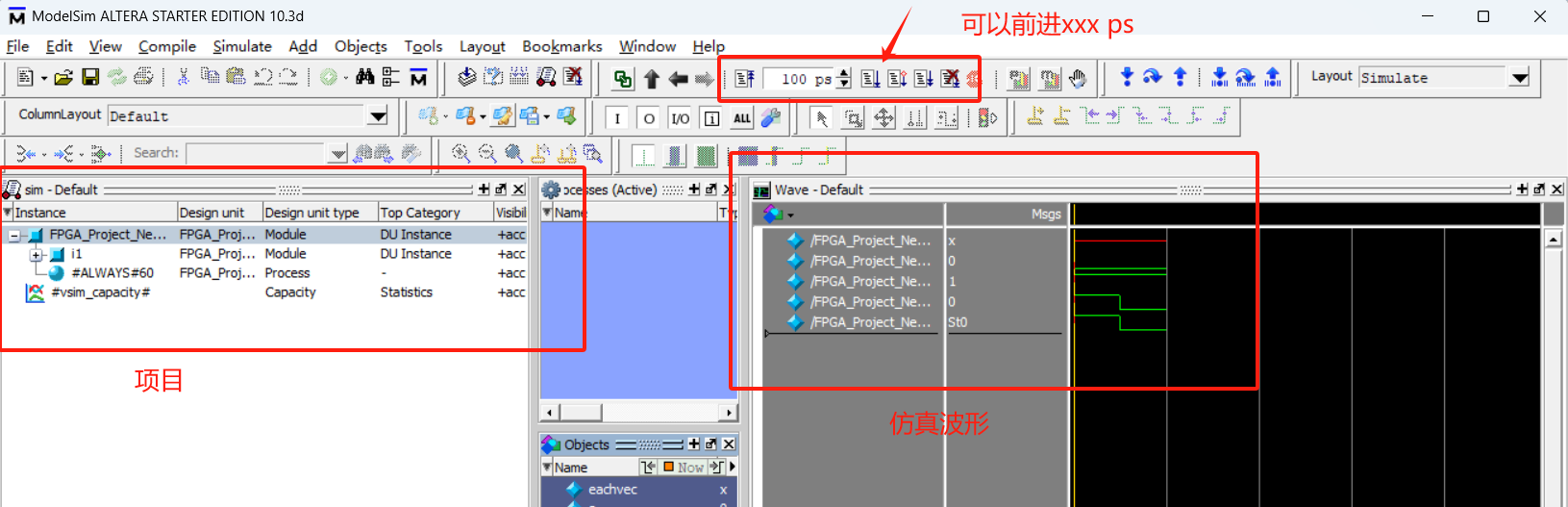

仿真

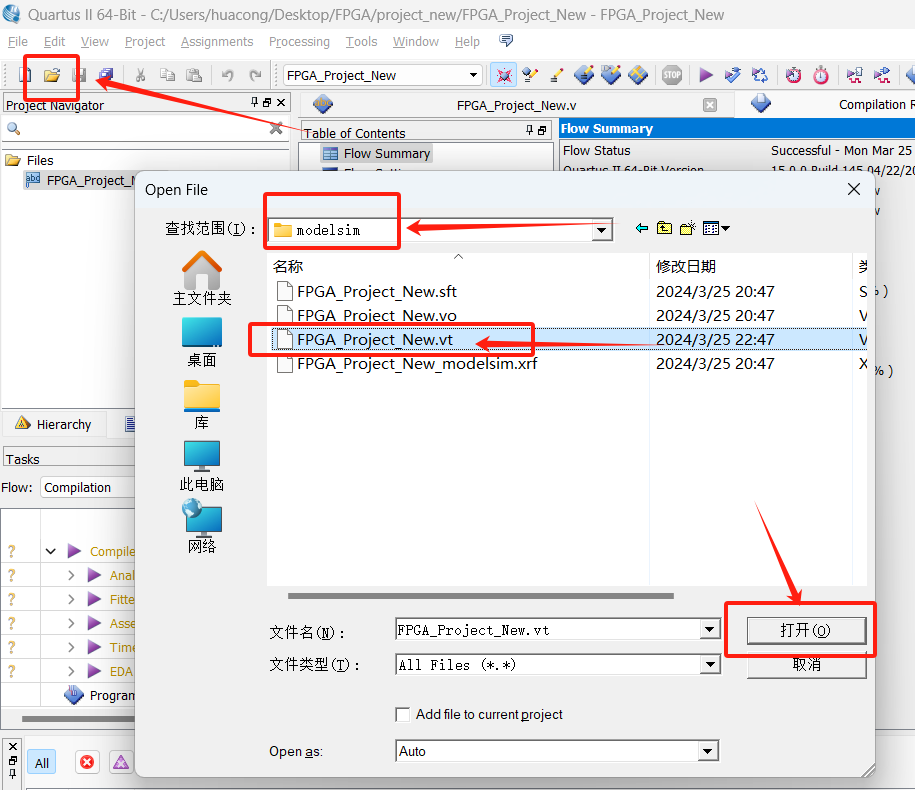

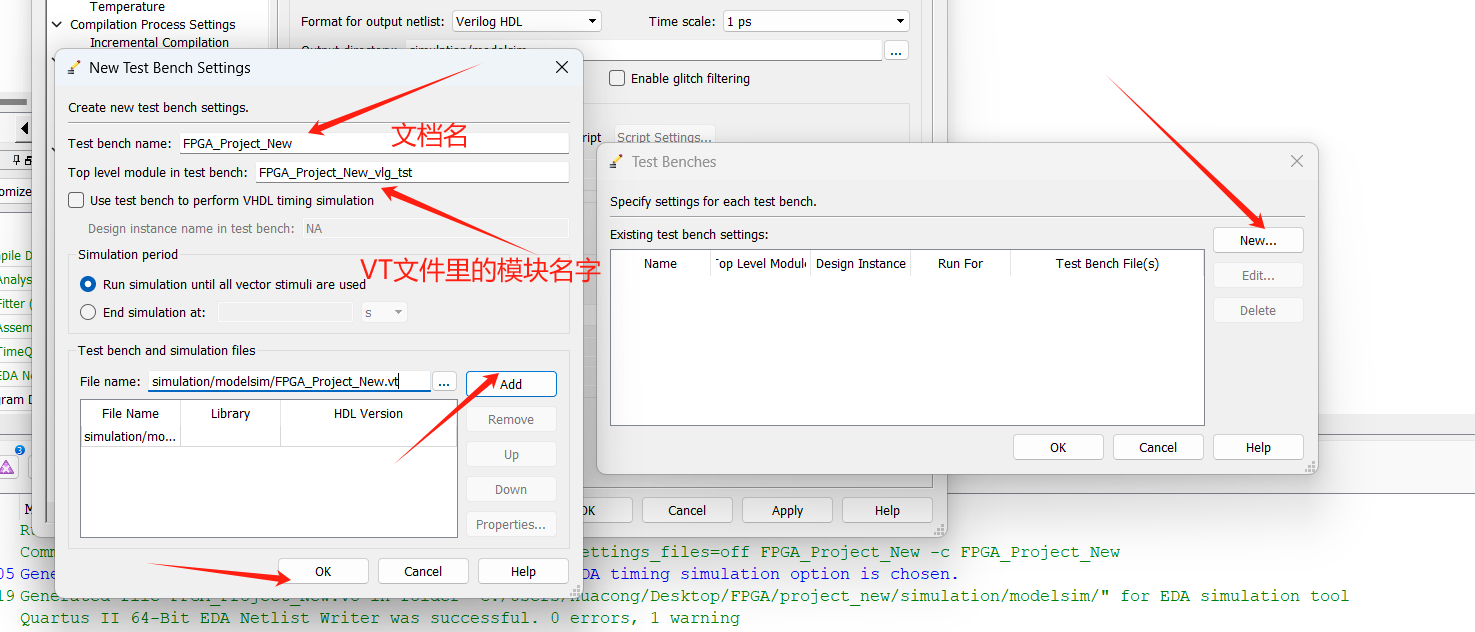

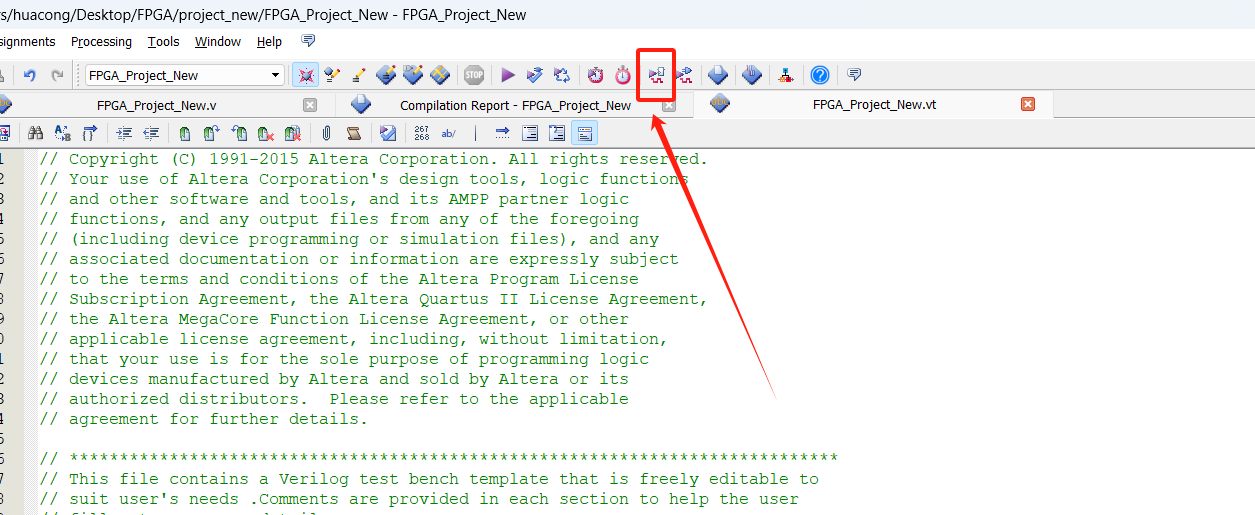

1.生成.VT仿真文件

可以在文件夹找到生成的.vt文件(文件类别选全部可以看见)

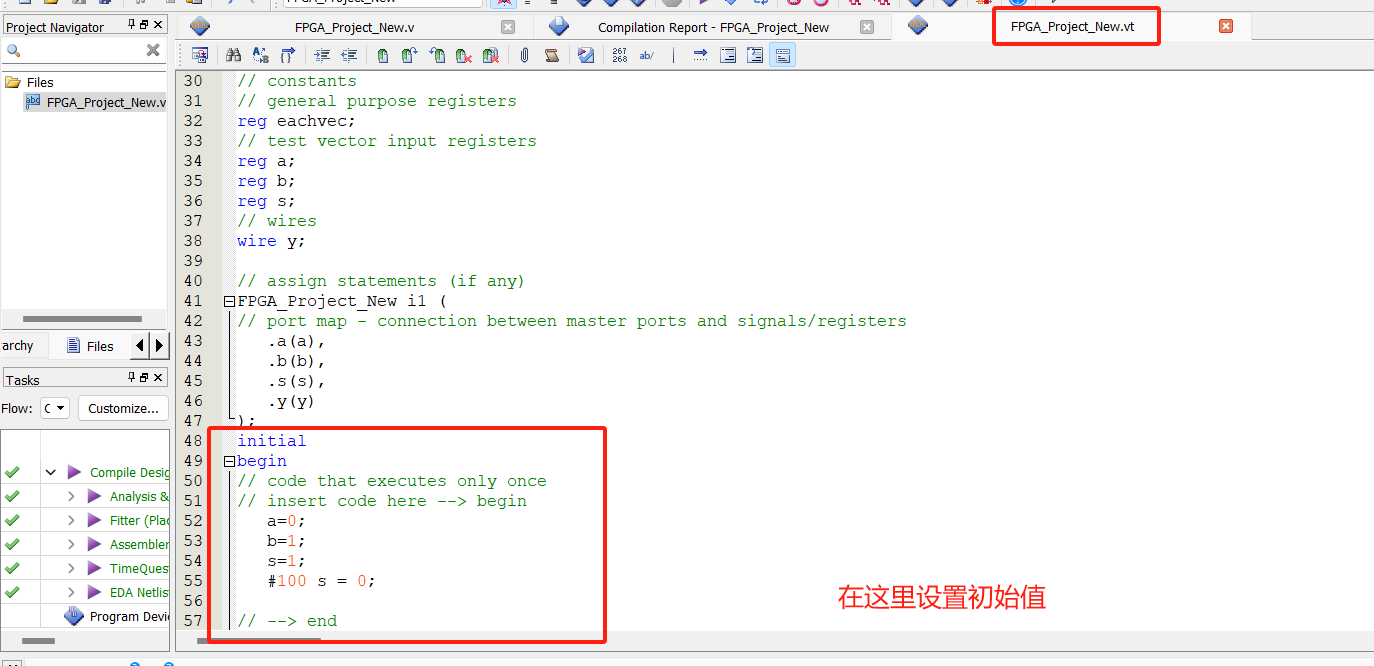

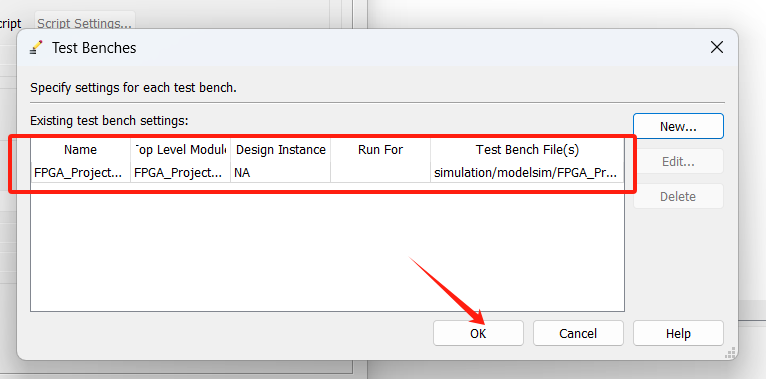

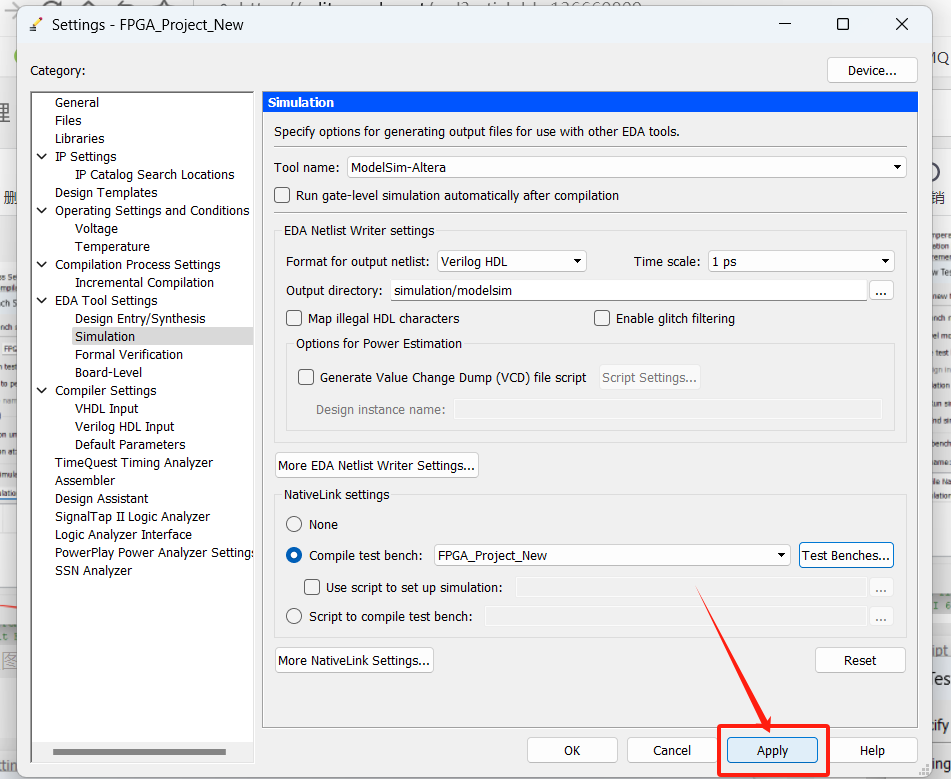

2.设置初始值并仿真

咱们可以设置初始值

initial

begin

// code that executes only once

// insert code here --> begin

a=0;

b=1;

s=1;

#100 s = 0;

// --> end

$display("Running testbench");

end

打开后自动弹出

总结

有一些坑要踩过才知道,所以一定要实际操作一次

本文详细介绍了如何在QuartusII软件中使用VerilogHDL创建FPGA项目,包括新建工程、编写测试模块、生成VT仿真文件以及设置初始值进行仿真的步骤,强调了实践操作的重要性。

本文详细介绍了如何在QuartusII软件中使用VerilogHDL创建FPGA项目,包括新建工程、编写测试模块、生成VT仿真文件以及设置初始值进行仿真的步骤,强调了实践操作的重要性。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?