此系列记录FPGA在学校的学习过程。

目录

FPGA系列

需要用到的软硬件:

软件:Quartus II 15.0 (64-bit)

硬件:

5CEBA4F23C7芯片

1、创建新的工程和开发板烧录在下面链接(带仿真教程)

新建工程带仿真链接:

FPGA在校学习记录系列—新建一个FPGA工程编写程序并仿真(Verilog HDL)

开发板烧录链接:

FPGA在校学习记录系列—实验4不同状态的LED+开发板(Verilog HDL)

这次创建的新工程名字为:IPcore_pll_v3

2、实验内容要求

1、调用并设置锁相环(PLL)IP核;

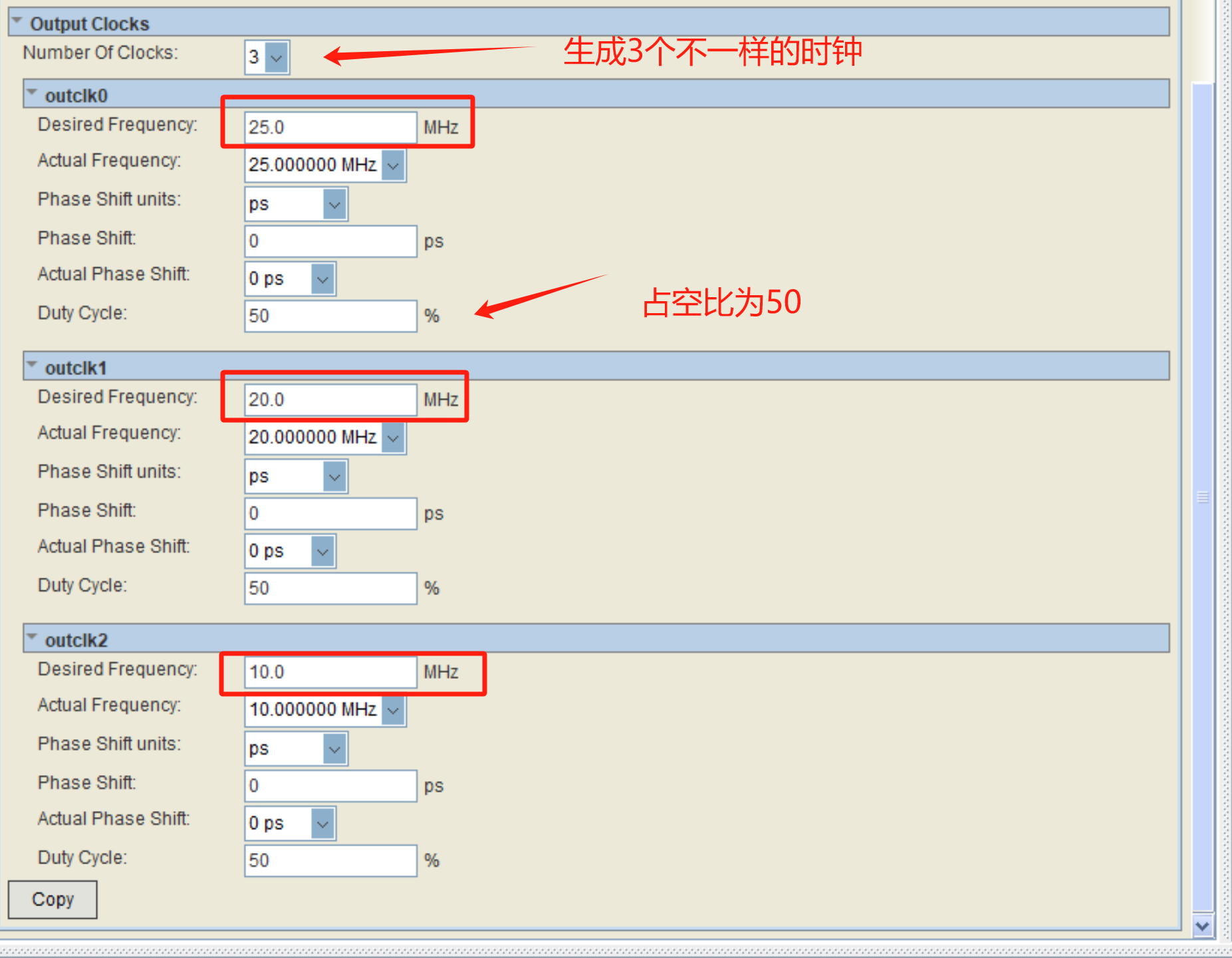

2、设置生成三种不同频率的clk信号;

3、生成并实现基于三种不同频率下的 32进制计数器;

4、编写测试文件,进行仿真测试。

3、创建一个新的工程,并设置Altera PLL

(1)创建新工程在文章顶部链接

这次创建的新工程名字为:IPcore_pll_v3

(2)打开IP内核并设置

FPGA在校学习记录系列—实验7(1)IP核的调用及仿真(ALTPLL)(Verilog HDL)

在上面这篇文章中已经有怎么打开IP核

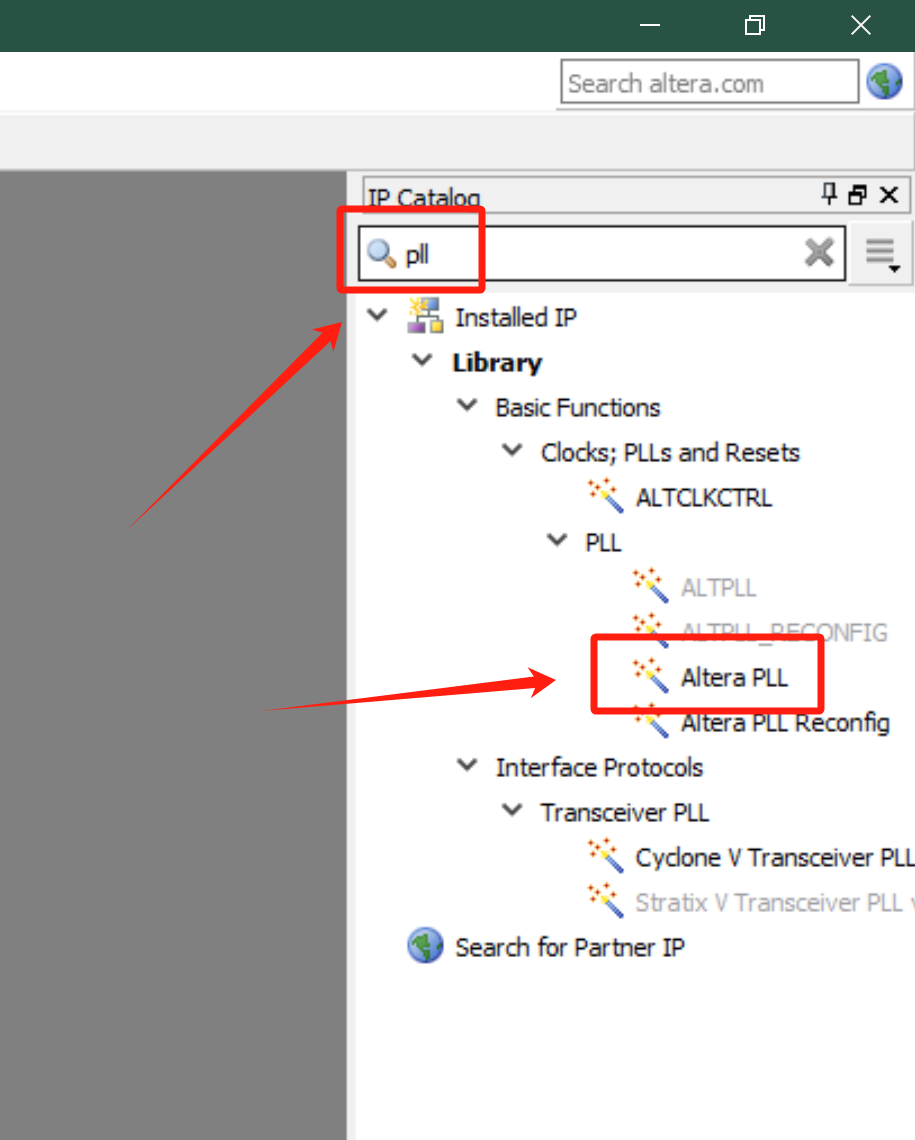

1.创建Altera PLL

双击‘Altera PLL’

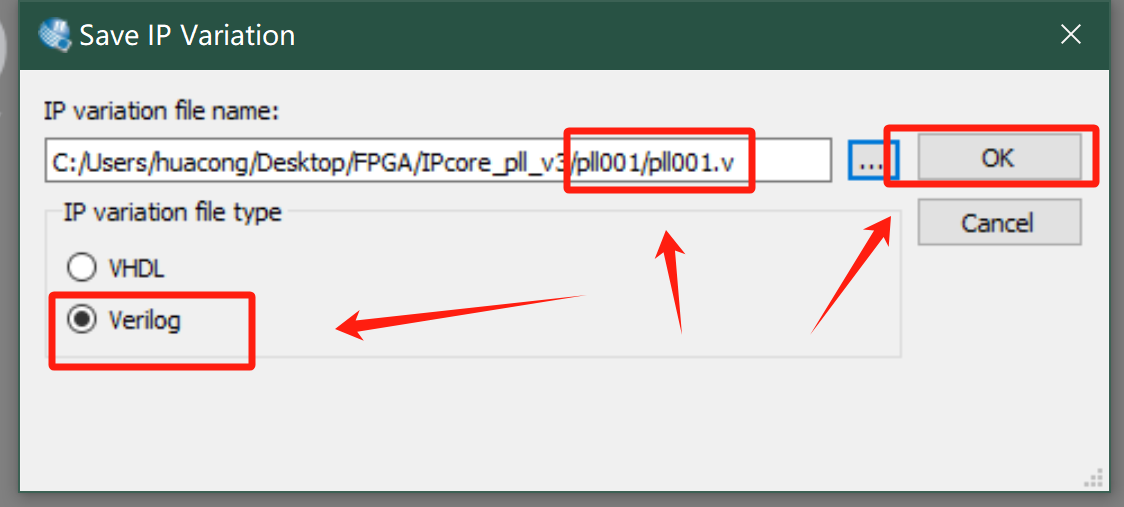

填写好路径:

稍等一下

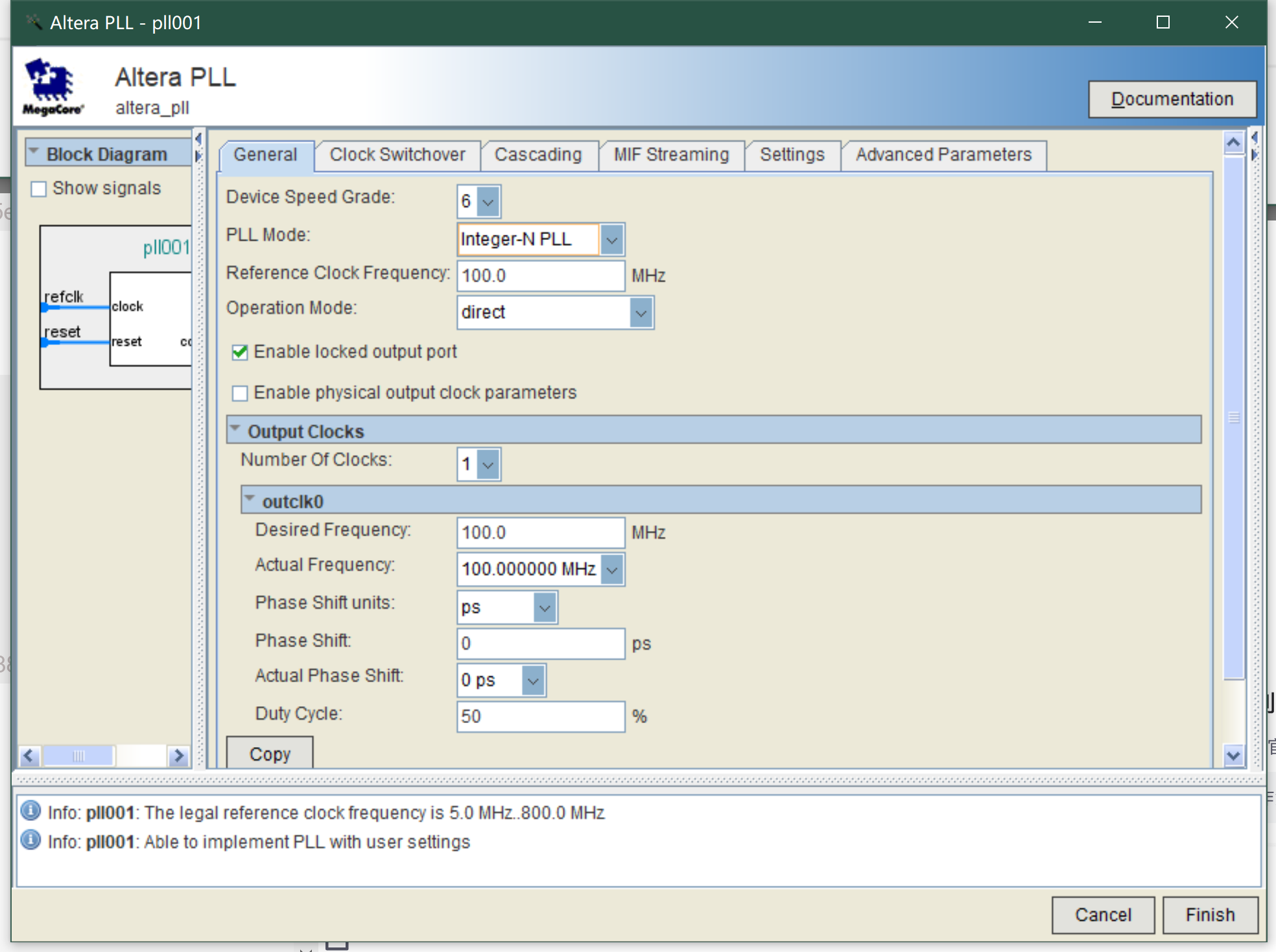

自动弹出设置界面

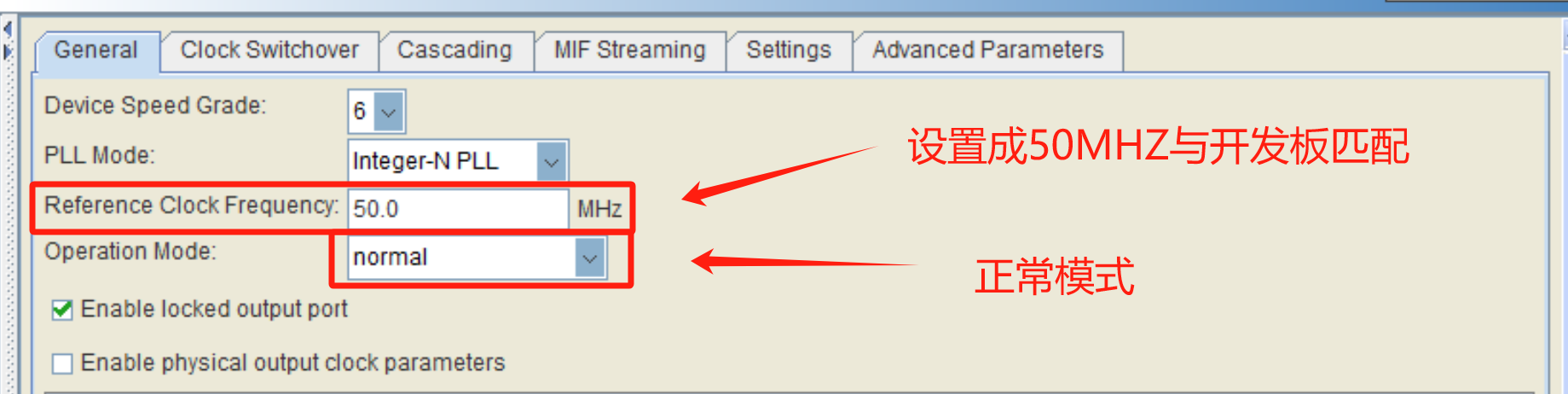

2.设置Altera PLL

设置成50Mh与开发板匹配

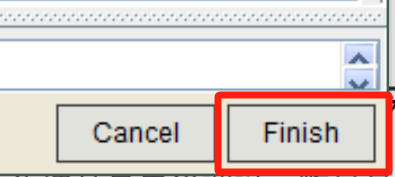

设置好之后点击右下角完成

设置好之后点击右下角完成

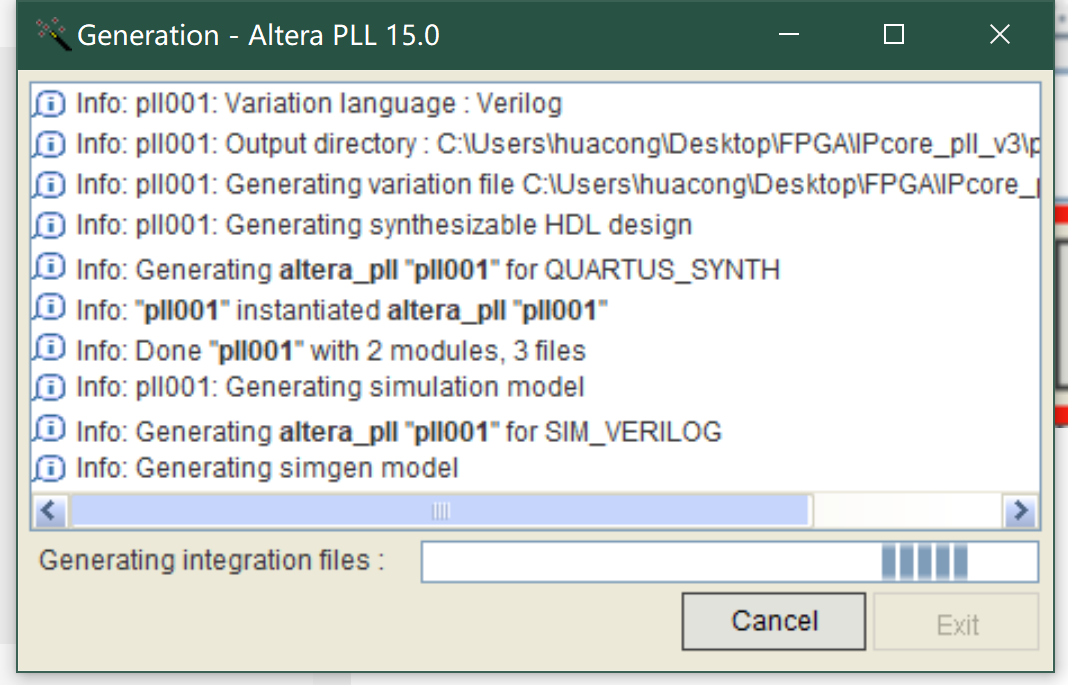

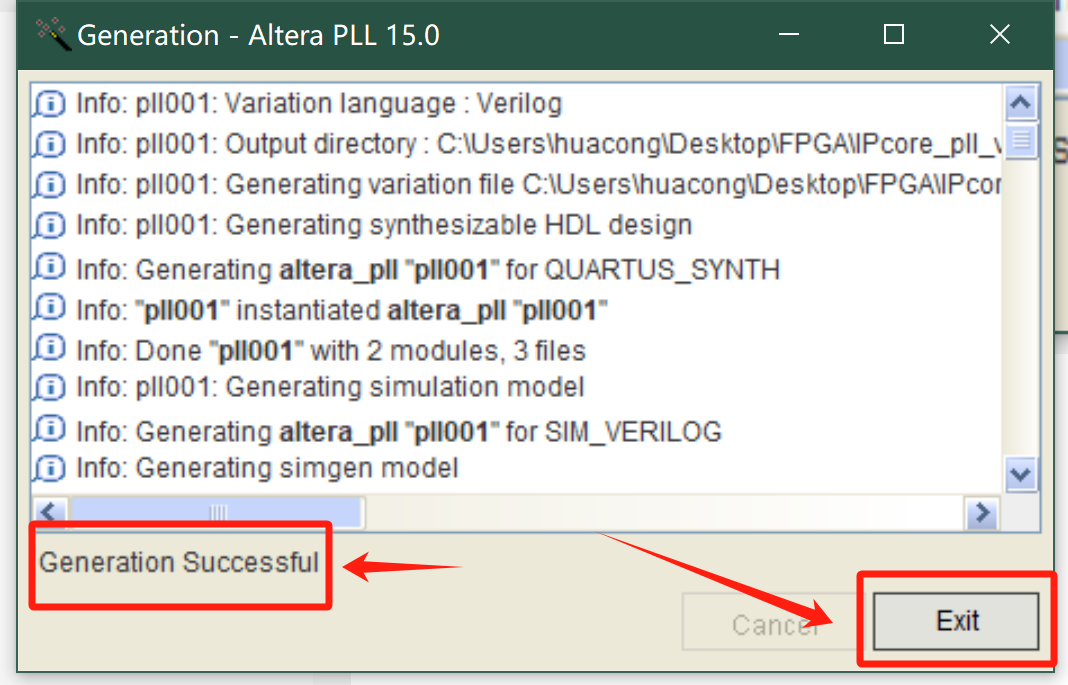

等待一下

电机右下角的推出

电机右下角的推出

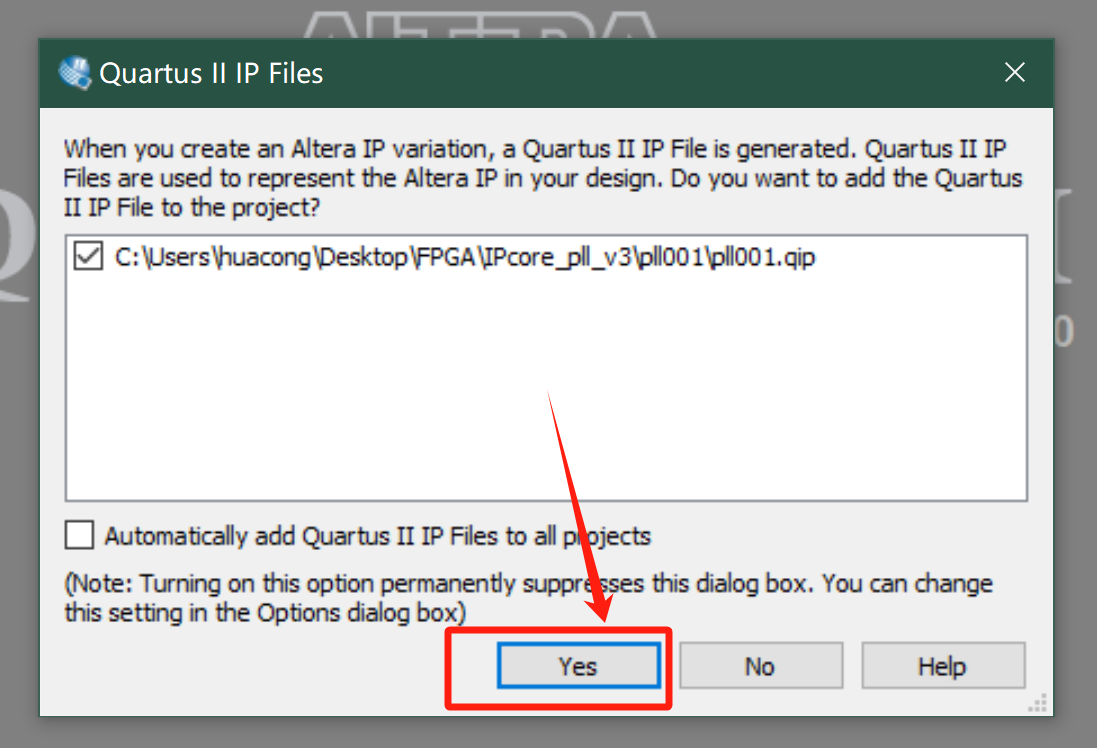

点击yes

点击yes

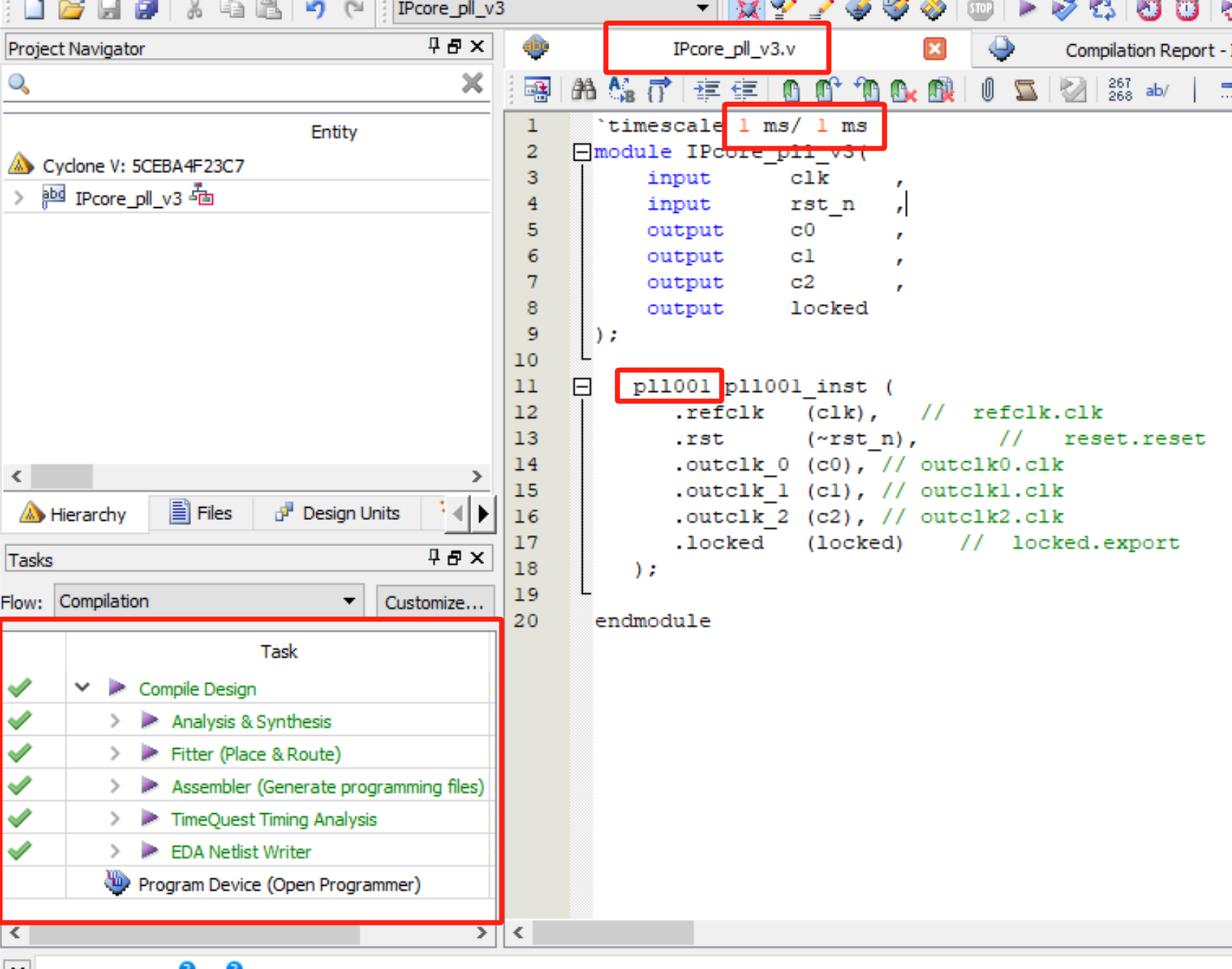

4、调用PLL

新建一个verilog文件

`timescale 1 ms/ 1 ms

module IPcore_pll_v3(

input clk ,

input rst_n ,

output c0 ,

output c1 ,

output c2 ,

output locked

);

pll001 pll001_inst (

.refclk (clk), // refclk.clk

.rst (~rst_n), // reset.reset

.outclk_0 (c0), // outclk0.clk

.outclk_1 (c1), // outclk1.clk

.outclk_2 (c2), // outclk2.clk

.locked (locked) // locked.export

);

endmodule

时间匹配为1ms

时间匹配为1ms

调用上面设置的pll001.v文件,并整理为pll001_inst

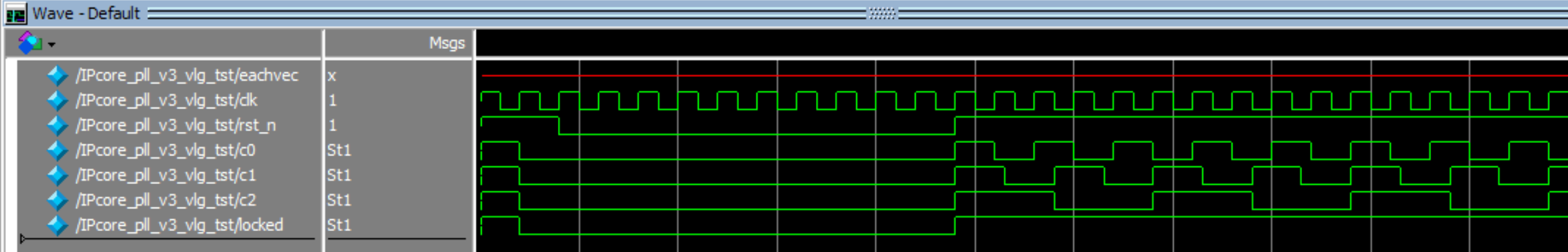

5、pll仿真

添加仿真文件教程在顶部链接

always #10 clk=~clk;

initial

begin

// code that executes only once

// insert code here --> begin

clk = 1;

rst_n = 1;

#40;

rst_n = 0;

#200

rst_n = 1;

#1000

$stop;

// --> end

$display("Running testbench");

end

仿真后结果与设置的相同

不同频率下的32进制计数器

(1)首先调用第一个频率

`timescale 1 ms/ 1 ms

module IPcore_pll_v3(

input clk ,

input rst_n ,

output c0 ,

output c1 ,

output c2 ,

output locked ,

input en1, //使能

output reg [5:0] cnt1

);

reg [3:0] units1; //个位计数缓存

reg [3:0] tens1; //十位计数缓存

pll001 pll001_inst (

.refclk (clk), // refclk.clk

.rst (~rst_n), // reset.reset

.outclk_0 (c0), // outclk0.clk

.outclk_1 (c1), // outclk1.clk

.outclk_2 (c2), // outclk2.clk

.locked (locked) // locked.export

);

always @(posedge c0 or negedge en1)

begin

if(!en1)

begin

cnt1 = 0;

units1 = cnt1 % 10;

tens1 = ((cnt1-units1)/10)%10;

end

else

begin

cnt1 <=(cnt1 == 31)?0:(cnt1 + 1);

units1 = cnt1 % 10;

tens1 = ((cnt1-units1)/10)%10;

end

end

endmodule

仿真要将时间改成ms

always #10 clk=~clk;

initial

begin

// code that executes only once

// insert code here --> begin

clk = 1;

en1= 0;

rst_n = 1;

#40

rst_n = 0;

#200

rst_n = 1;

#50

en1=1;

// --> end

$display("Running testbench");

end

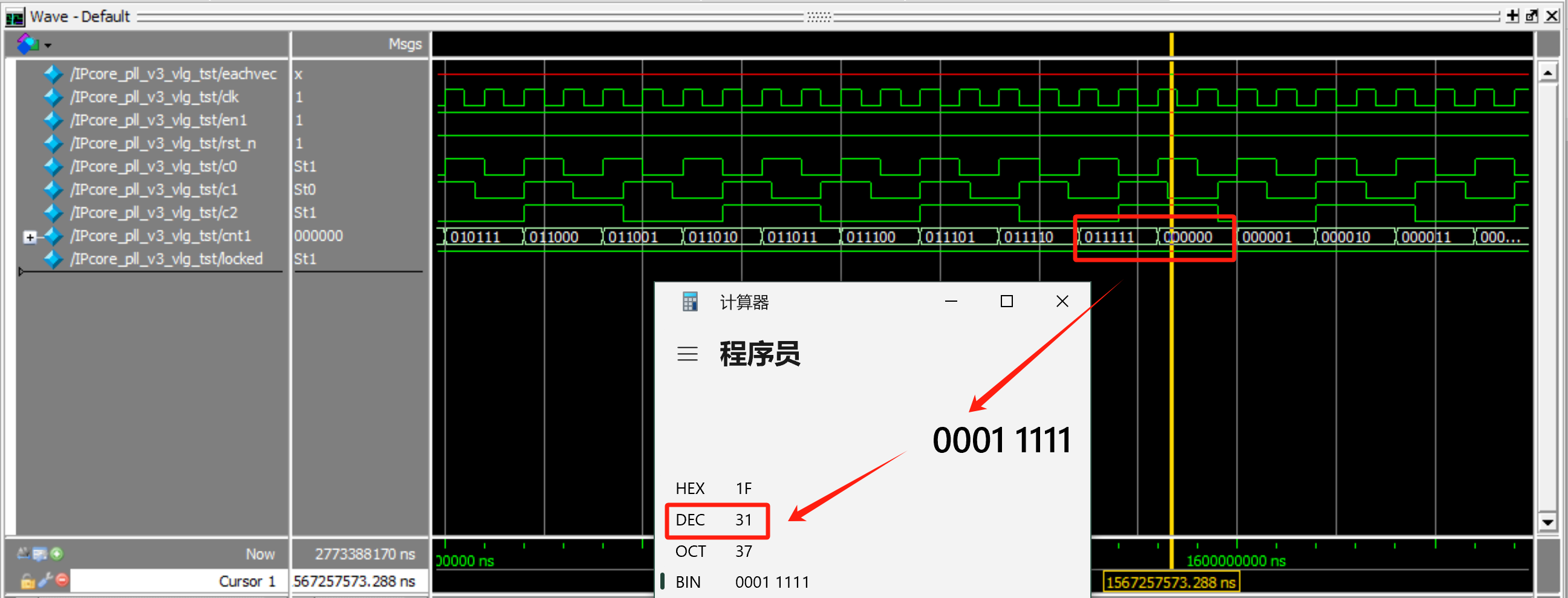

可以看见32位计数器验证成功

可以看见32位计数器验证成功

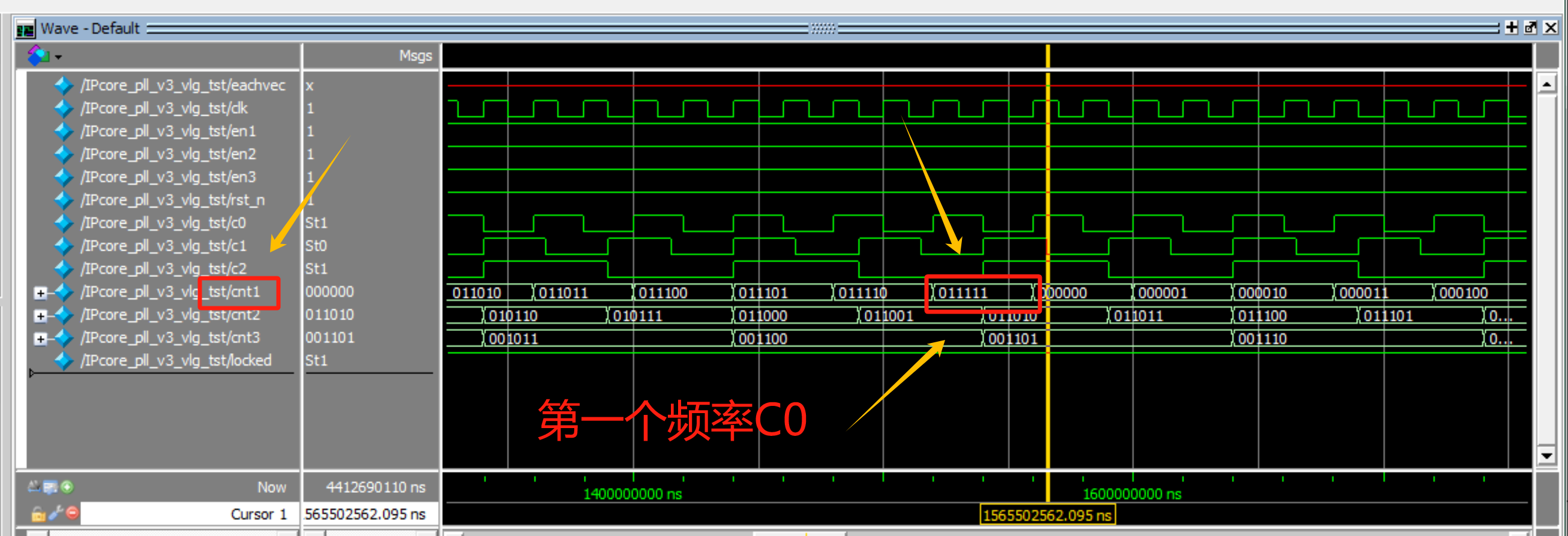

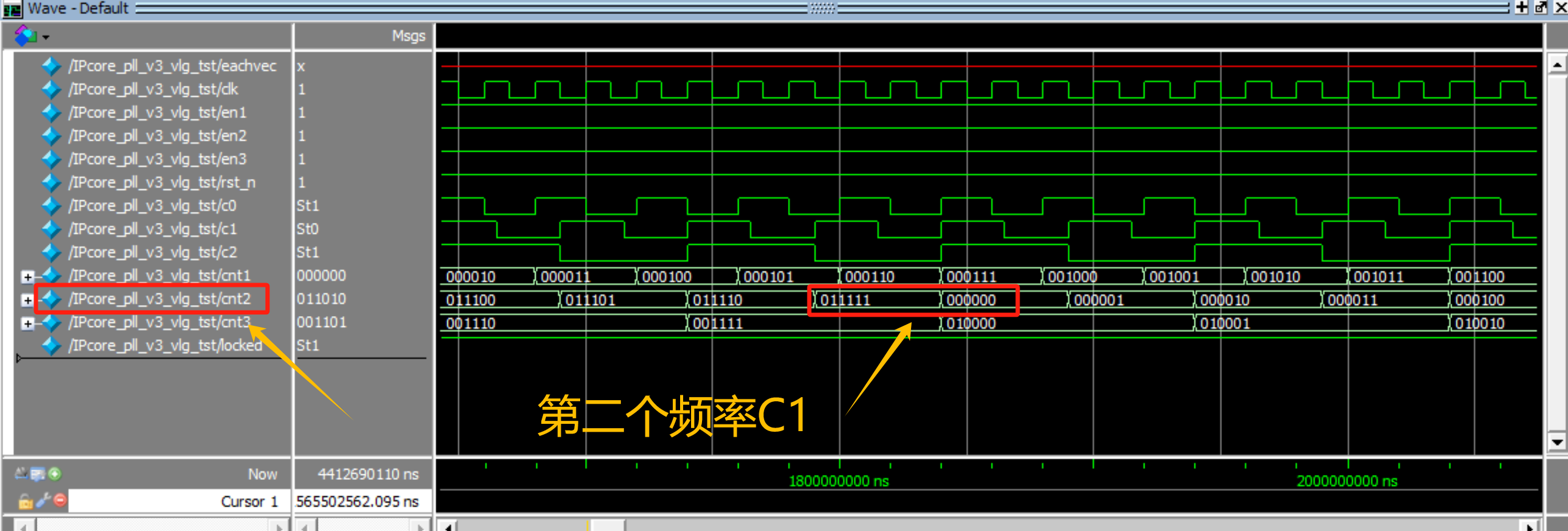

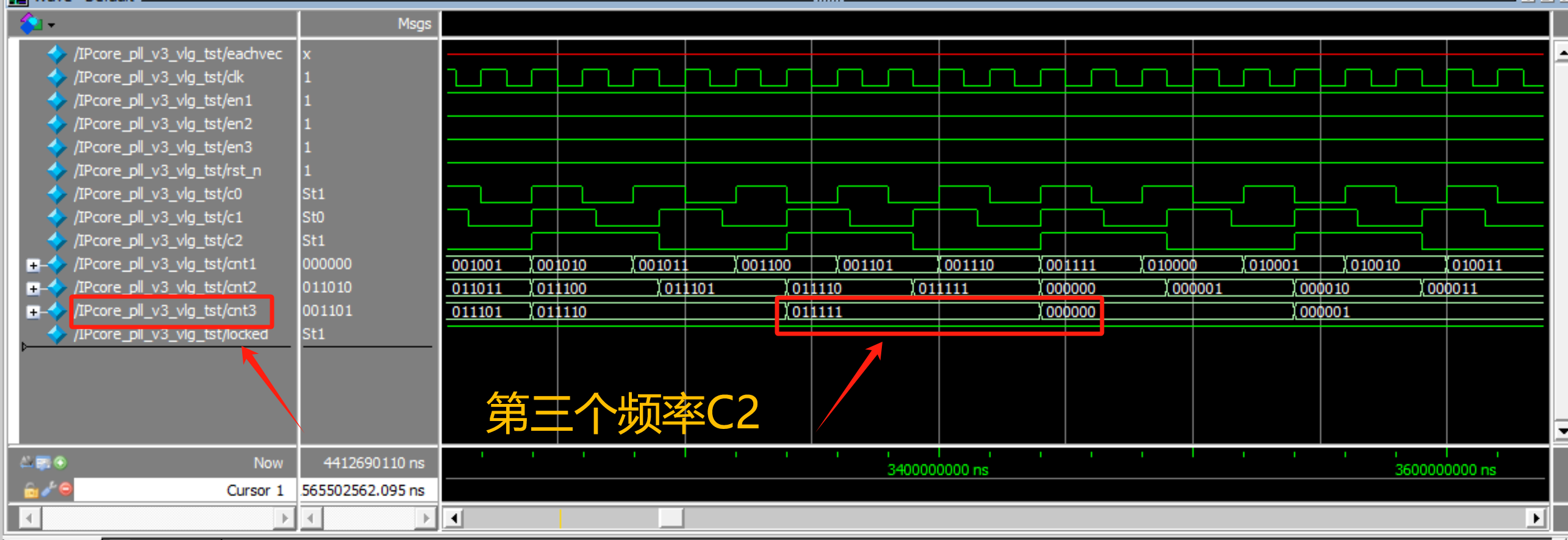

(2)三个频率下的32位计数器

`timescale 1 ms/ 1 ms

module IPcore_pll_v3(

input clk ,

input rst_n ,

output c0 ,

output c1 ,

output c2 ,

output locked ,

input en1, //使能

output reg [5:0] cnt1,

input en2, //使能

output reg [5:0] cnt2,

input en3, //使能

output reg [5:0] cnt3

);

reg [3:0] units1; //个位计数缓存

reg [3:0] tens1; //十位计数缓存

reg [3:0] units2; //个位计数缓存

reg [3:0] tens2; //十位计数缓存

reg [3:0] units3; //个位计数缓存

reg [3:0] tens3; //十位计数缓存

pll001 pll001_inst (

.refclk (clk), // refclk.clk

.rst (~rst_n), // reset.reset

.outclk_0 (c0), // outclk0.clk

.outclk_1 (c1), // outclk1.clk

.outclk_2 (c2), // outclk2.clk

.locked (locked) // locked.export

);

always @(posedge c0 or negedge en1)

begin

if(!en1)

begin

cnt1 = 0;

units1 = cnt1 % 10;

tens1 = ((cnt1-units1)/10)%10;

end

else

begin

cnt1 <=(cnt1 == 31)?0:(cnt1 + 1);

units1 = cnt1 % 10;

tens1 = ((cnt1-units1)/10)%10;

end

end

always @(posedge c1 or negedge en2)

begin

if(!en2)

begin

cnt2 = 0;

units2 = cnt2 % 10;

tens2 = ((cnt2-units2)/10)%10;

end

else

begin

cnt2 <=(cnt2 == 31)?0:(cnt2 + 1);

units2 = cnt2 % 10;

tens2 = ((cnt2-units2)/10)%10;

end

end

always @(posedge c2 or negedge en3)

begin

if(!en3)

begin

cnt3 = 0;

units3 = cnt3 % 10;

tens3 = ((cnt3-units3)/10)%10;

end

else

begin

cnt3 <=(cnt3 == 31)?0:(cnt3 + 1);

units3 = cnt3 % 10;

tens3 = ((cnt3-units3)/10)%10;

end

end

endmodule

仿真(时间改成ms)

always #10 clk=~clk;

initial

begin

// code that executes only once

// insert code here --> begin

clk = 1;

en1= 0;

en2= 0;

en3= 0;

rst_n = 1;

#40

rst_n = 0;

#200

rst_n = 1;

#50

en1=1;

en2=1;

en3=1;

// --> end

$display("Running testbench");

end

1945

1945

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?