问题

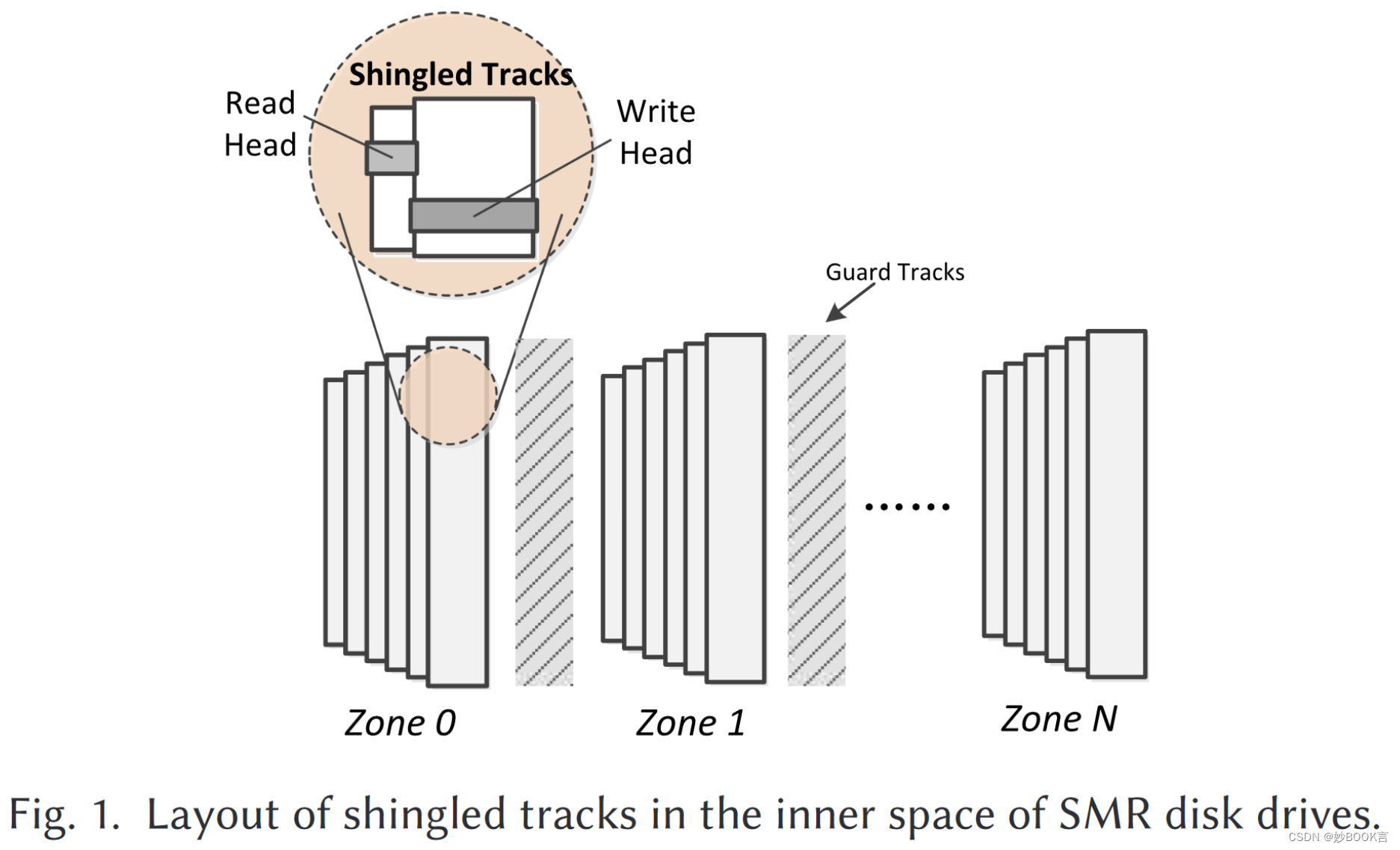

为了满足大数据所需的巨大存储容量,数据中心一直在采用高密度叠瓦式磁盘(SMR),由于SMR可以在不改变存储介质物理特性的情况下提高存储密度,它只改变机械控制器和轨道的布局。然而,SMR只允许顺序写入,导致写放大和不平衡的读写性能,导致其细粒度随机写性能较弱。

目前主要有两种类型的SMR驱动器:驱动器管理的SMR(DM-SMR)和主机管理的SMR(HM-SMR),在数据管理和控制器机制方面有所不同。DM-SMR通过驱动器控制器随机写入,将随机数据顺序地传输到SMR,可以直接使用无需额外编码。HM-SMR不接收随机写入请求,要求应用程序在主机侧主动将其随机写入组织成顺序模式。

现有方法局限性

许多研究提出用固态驱动器(SSD)缓存系统来解决SMR细粒度随机写性能弱的问题。然而,大多数当前的缓存解决方案没有充分考虑SMR驱动器的特性:

-

现有缓存算法中的优化目标不适合于基于SMR的混合存储。例如用于优化缓存流行度的最近最少使用(LRU)算法和用于优化写放大因子的MOST算法,会导致高写放大因子或缓存命中率低,不能充分利用缓存系统的性能。

-

SMR驱动器的写入延迟和吞吐量不稳定,写入速度通常比读取速度慢得多,与CMR不同。在优化时必须考虑数据块的特性(例如流行性)和SMR的读写性能差异。

-

对于DM-SMR,许多基本结构和功能被制造商隐藏(例如,内部持久缓冲区的行为)。缓存算法难以适应SMR驱动器的内部结构和方案。

本文方法

本文提出了SMR感知缓存框架SAC+,以改进基于SMR的混合存储。

-

优化目标设为读取-修改-写入(RMW)计数,不是传统的缓存命中率和写放大因子。实验分析发现,RMW与SMR的I/O时间相关性最高,缓存命中率和写放大因子与SMR的I/O时间相关性较低。

-

充分考虑了SMR驱动器读写性能的不平衡和写入性能的不稳定,对各种工作负载进行自适应,以优化整体性能。

-

集成了DM-SMR和HM-SMR,提供了一个通用的框架。

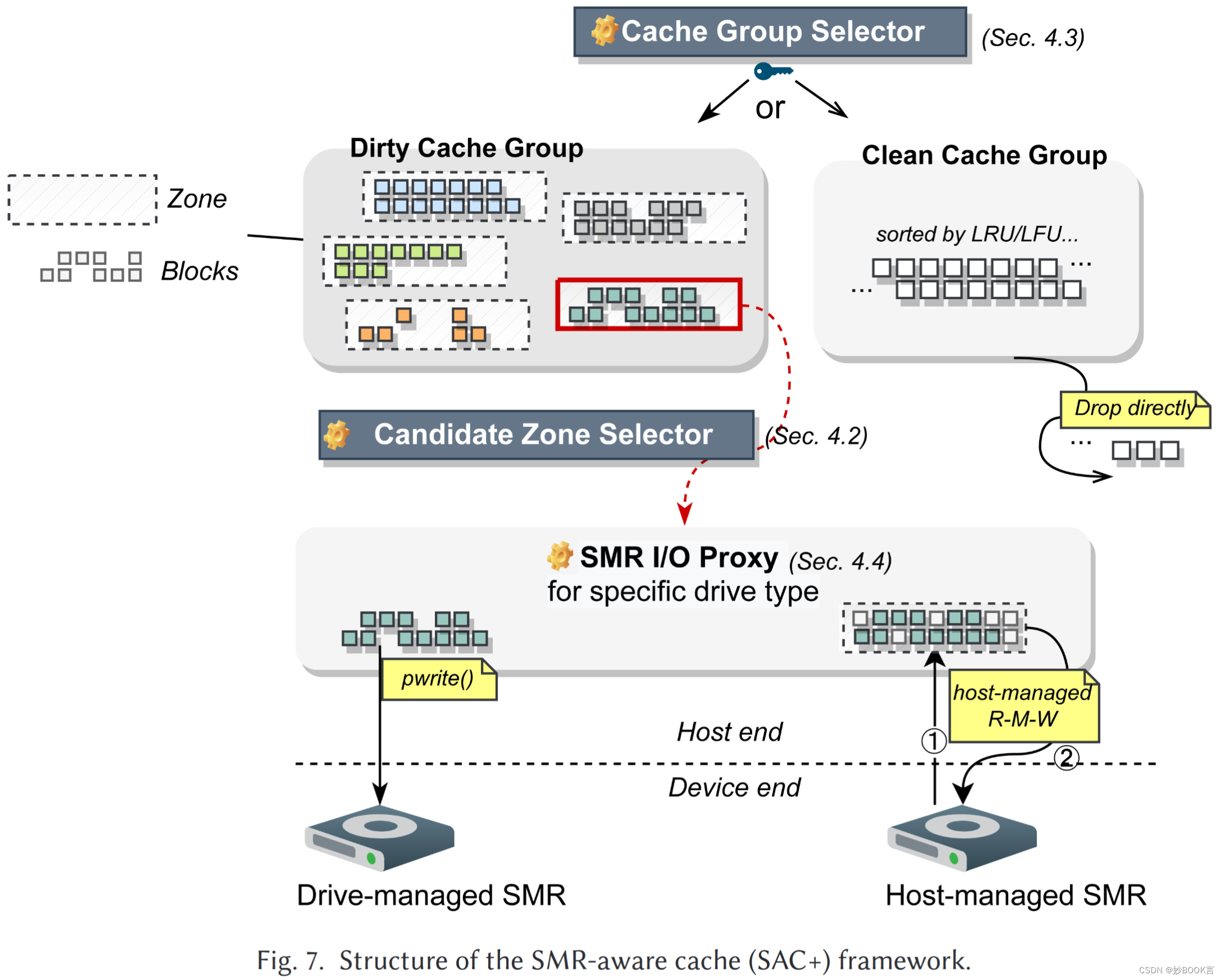

SAC+将缓存的块分为两组:干净块和脏块。干净缓存块专门用于读请求,脏缓存块用于写请求和读请求。这两个缓存组使用不同的算法进行缓存替换。主要包括3个组件:

-

区域选择器:管理脏缓存组中的块,根据脏块的目标区域对脏块进行逻辑分组。每次执行驱逐时,区域选择器选择一个目标区域,并驱逐与该区域相关联的脏块。使用基于可能释放的区块的评分方法选择候选区域,目标是减少总体RMW操作次数。干净缓存块直接用LRU进行管理。

-

组选择器:确定在运行时应收回哪些组的数据。因为从两个缓存组中驱逐数据会导致不同的性能损失,需要计算每个高速缓存组的逐出成本,并以最低成本逐出组中的块。

-

SMR设备代理:用于访问DM-SMR和HM-SMR设备。使用设备访问接口将I/O请求路由到目标SMR设备,并向顶级提供统一的设备抽象。设备代理包含针对某些设备类型优化的高级操作,如快速主机管理的RMW操作、部分RMW操作和写入时排序。

真实世界轨迹的评估结果表明,与最先进的算法相比,SAC+将I/O时间减少了36–93%。

总结

针对SMR设备的缓存框架,如何适应各种SMR设备,同时实现更高的读写性能。本文提出SMR感知缓存框架SAC+,同时适应DM-SMR和HM-SMR两种设备。通过分析将缓存优化目标设为最小化读取-修改-写入(RMW)计数,从而实现最佳的SMR I/O时间。整体将缓存分为两组:干净块(用于读请求)和脏块(用于读写请求),包括3个组件:(1)区域选择器:管理脏块,根据脏块的目标区域对脏块进行逻辑分组。执行驱逐时,基于可能释放块选择一个目标区域,并驱逐与该区域相关联的脏块。干净块直接用LRU进行管理。(2)组选择器:执行驱逐时,计算每个组的逐出成本,逐出最低成本组中的块。(3)SMR设备代理:使用设备访问接口将I/O请求路由到目标SMR设备,并向顶级提供统一的设备抽象。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?