USRP 简介

通用软件无线电外设( USRP ) 是由 Ettus Research 及其母公司National Instruments设计和销售的一系列软件定义无线电。USRP 产品系列由Matt Ettus领导的团队开发,被研究实验室、大学和业余爱好者广泛使用。

X 系列 :X410

USRP X410 (4 TX/RX Channels, 400 MHz BW, Zynq US+ RFSoC ZU28DR)

NI Ettus USRP X410 是一款高性能、多通道、基于 Zynq US+ RFSoC 的软件定义无线电 (SDR),用于设计和部署下一代无线系统。

概述

NI Ettus USRP X410 是一款高性能、多通道软件定义无线电。 SDR 设计用于 1 MHz 至 7.2 GHz 的频率,可调至 8 GHz,采用两级超外差架构,具有 4 个独立的 TX 和 RX 通道,每个通道的瞬时带宽为 400 MHz。 用于数据卸载和控制的数字接口包括两个支持 100 GbE 的 QSFP28 接口、一个 PCIe Gen3 x8 [1] 接口以及标准命令、控制和调试接口:USB-C JTAG、USB-C 控制台、以太网 10/100 /1000。 USRP X410 是一款基于 Xilinx Zynq Ultrascale+ ZU28DR 射频片上系统 (RFSoC) 构建的一体化器件,具有内置数字上下转换和板载软决策前向纠错 (SD-FEC) IP。

使用您选择的软件

NI Ettus USRP X410 完全支持流行的开源 USRP 硬件驱动程序 (UHD) 版本 4.1 或更高版本[2]。 UHD 4.1 旨在支持 400 MHz 带宽和板载多个通道所带来的大数据移动要求。 USRP X410 支持开源 SDR 设计流程,例如 C/C++ 和 GNU Radio 以及 LabVIEW FPGA [1]。 与其他基于 RFSoC 的系统不同,USRP X410 已完全准备好移植您以前的 UHD 设计,以便通过简单的重新编译来利用高性能功能。

联网/单机运行

由于 USRP X410 基于 ZU28DR 射频片上系统 (RFSoC) 器件构建,因此它配备了四核 ARM Cortex-A53 处理子系统,主频高达 1.2 GHz,可满足独立应用要求。 此外,RFSoC 还包含一个双核 ARM Cortex-R5 实时处理单元,用于板载监控。

内置IP

USRP X410 上的板载 RFSoC 包含的 FPGA 可编程逻辑资源是上一代 X 系列 USRP 器件的两倍多。 此外,ZU28DR还配备8个软判决前向纠错(SD-FEC)硬IP核,非常适合无线通信系统。 鉴于 RFSoC 内置 ADC 和 DAC 的高速特性,Zynq 器件具有 8 个数字上变频和数字下变频 IP 内核,可实现快速带内重新调谐或信号减弱。

多电台同步

通过内置 GPSDO(GPS 规范振荡器)或 10 MHz 参考和 1 PPS(每秒脉冲)输入信号接口,可以实现多无线电时钟和定时同步操作。 不支持多无线电相位对齐和相位相干操作,因为 USRP X410 不支持 RF 链 LO 导入和导出功能。

[1] PCIe Gen3 x8 仅受 NI-USRP 和 LabVIEW FPGA 设计流程支持

[2] UHD 4.2 或更高版本支持 100 GBE

特征

- 高通道密度

- 可靠且容错的部署

- 独立(嵌入式)或基于主机(网络流)操作

- 完全集成和组装(USRP X410不支持可插拔子卡)

- 1 MHz 至 7.2 GHz 频率范围(可调至 8GHz)

- 每个通道的瞬时带宽高达 400 MHz

- 半宽 RU 外形中 4 个 RX、4 个 TX

- Xilinx Zynq-Ultrascale+ ZU28DR RFSoC

- 12位ADC、14位DAC

- IQ 采样时钟速率高达 500 MS/s

- 板载SD-FEC、DDC、DUC

- 四核 ARM Cortex-A53 高达 1.2 GHz CPU

- 双核 ARM Cortex-A5 MPCore,频率高达 500 MHz

- 两个 QSFP28 端口(10 Gb 以太网、100 Gb 以太网、Aurora)

- 两个 iPass+™ zHD® 接口 (PCIe Gen3 x 8)

- RJ45 (1 GbE) [1]

- 10 MHz 时钟参考

- PPS时间参考

- 触发输入/输出接口

- 内置GPSDO

- 两个 FPGA 可编程 GPIO 接口 (HDMI)

- 1 个 C 型 USB 主机端口

- 1 个 C 型 USB 端口(串行控制台、JTAG)

- 看门狗定时器

- 开放嵌入式Linux

- USRP Hardware Driver™ (UHD) 开源软件 API 版本 4.1.0 或更高版本

- 射频片上网络 (RFNoC™) FPGA 开发框架

- Xilinx Vivado® 2019.1 设计套件(不含许可证)

- GNU Radio 支持由 Ettus Research™ 通过 GR-UHD 维护,GR-UHD 是 GNU Radio 分发的 UHD 接口

[1] RJ45端口用于设备的远程管理,不支持IQ流。

USRP X410 ZBX 子板信息

ZBX 子板是一款双通道超外差收发器,主要用于 8 GHz 以下频率范围的电信应用。 它支持高达 400 MHz 的模拟带宽。

- ZBX 子板是 Ettus USRP X410 的子板。

功能列表:

- 频率范围(Tx 和 Rx):1 MHz - 7.2 GHz(注:调谐范围扩展至 8 GHz)

- 最大模拟带宽:400 MHz

- 增益范围:0-60 dB。

注意:对于低于 500 MHz 的频率,Rx 增益范围减小至 0-38 dB。 - 板载 CPLD,具有高度灵活性

- 最大输出功率:高达 23 dBm(取决于频率,请参阅规格中的 TX 最大输出功率)

- 最大输入功率:0 dBm(运行,请参阅损坏级别规范)

尽管可以在给定时间调整 ZBX LO,但 X410 不支持定时调整,因为不支持 NCO(在 RFSoC 内)的定时调整。

请参阅 Ettus USRP X410 规格中的 RF 部分,了解全面的 ZBX 子板规格列表。

操作原理

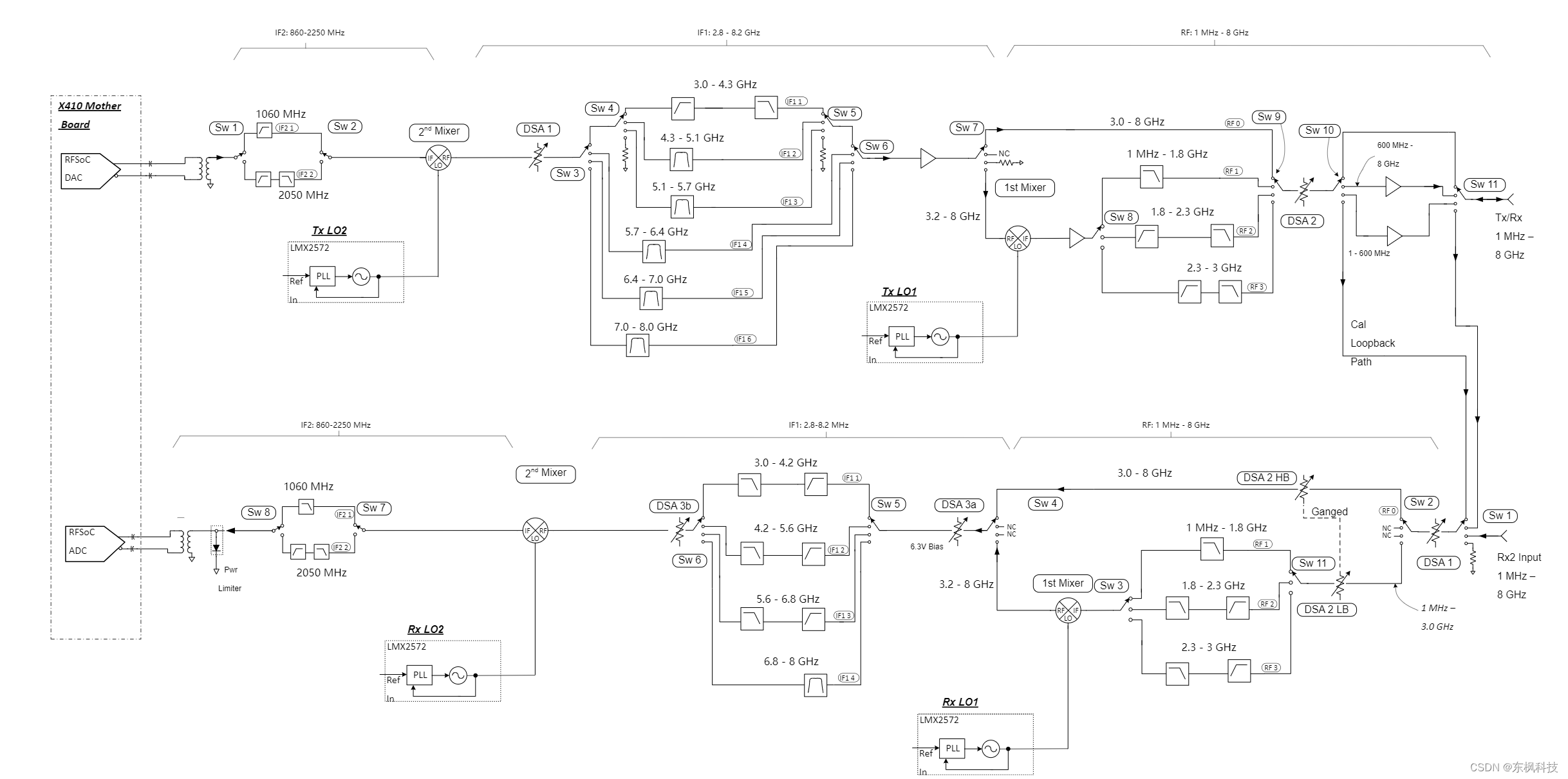

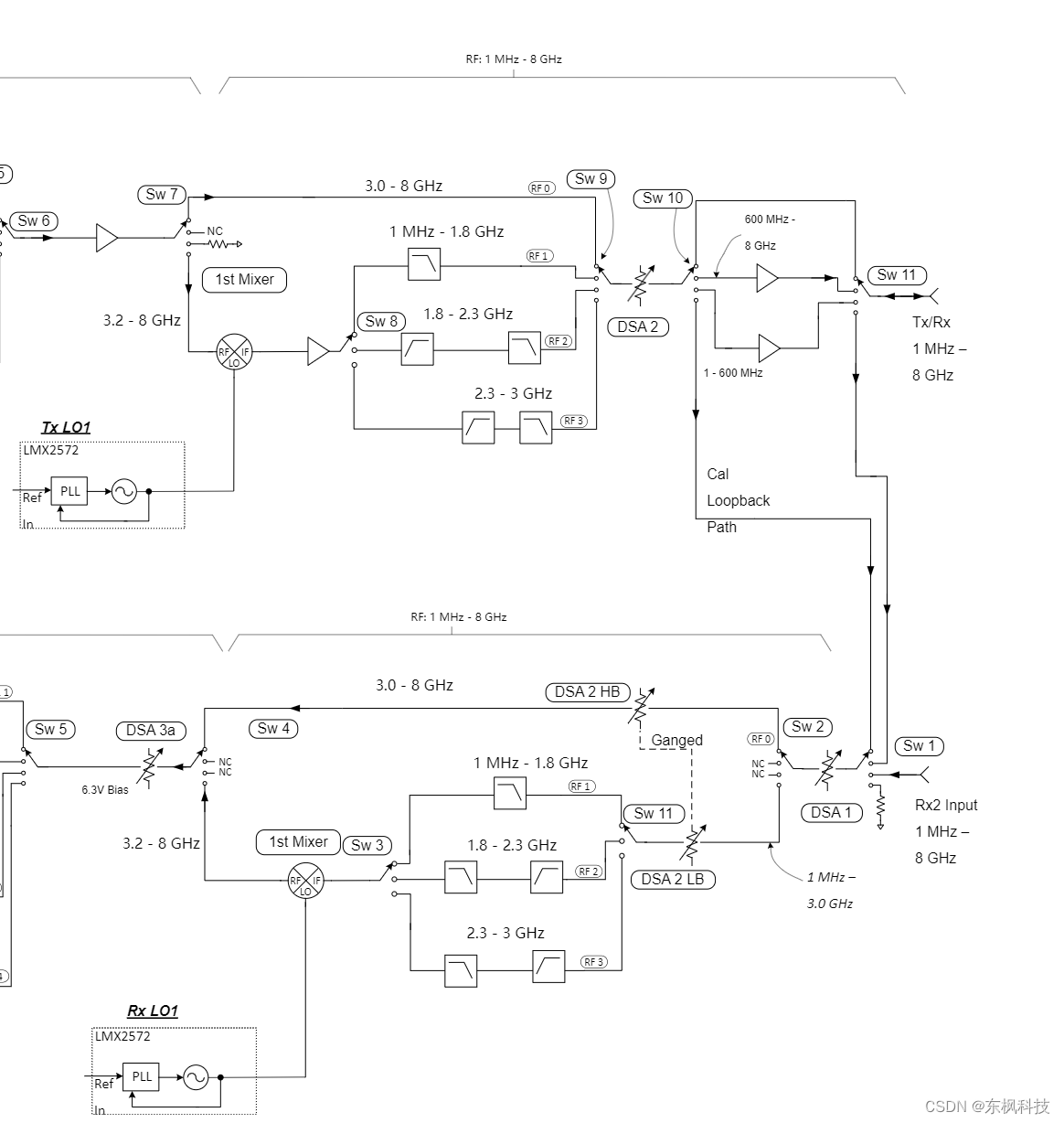

ZBX 子板有两个收发器链。 下面的简化框图显示了它们的结构:

它是一款超外差收发器,最多具有两个 IF 级。 第二个 IF 级仅用于中心频率低于 3 GHz 的情况。 高于该频率,所需的中心频率变为第一中频 (IF1)。 第二个 LO 级始终启用,并将 IF 移至 1 至 2 GHz 之间的值。 USRP ADC/DAC(以大约 3 GHz 的采样率运行)将直接对 IF 进行采样,并以数字方式下变频至 DC 或从 DC 进行下变频。

TX 和 RX 路径几乎对称,不同频段略有不同。 各个增益级沿着 TX 和 RX 路径分布(另请参阅增益控制;请注意,TX 路径包括可选放大器以及 DSA)。 所有 LO 合成器都是相同的 (LMX2572)。

数字控制

对于数字控制,ZBX 包括一个 CPLD(其源代码是 UHD 存储库的一部分,可以在 fpga/usrp3/top/x400/dboards/zbx/cpld/ 下找到)。 CPLD 通过寄存器进行控制。 其寄存器空间作为 Radio RFNoC 块寄存器空间的子集公开(从地址 0x80000 开始)。

CPLD 用于控制所有开关、DSA、放大器、LED、LO 合成器和电源轨。 CPLD 还控制 ZBX 的状态相关行为(即取决于 RX/TX 状态的行为)。 为此,来自 FPGA 的 ATR 信号被路由到 CPLD。 增益控制中还描述了部分 CPLD 功能集。

本振控制

ZBX 子板的正常操作是将其调整到所需的中心频率,UHD 将在内部计算各个 LO 以及 NCO 的频率。 UHD 在计算 LO 和 NCO 频率时使用一些规则:

- 为了简化算法,LO 频率被量化为 LO 参考频率的倍数(其本身取决于主时钟速率)。

- 为了减少 LO 杂散,LO 合成器输出使用最小频率为 3.2 GHz 的模拟带通滤波器进行滤波。

- 为了避免注入锁定(附近合成器相互影响的效应),UHD 被编程为不同合成器选择不同的频率。 当将两个通道编程为相同频率时,LO 将有意以不同频率运行。 各种 LO 和 NCO 频率的组合仍然会产生相同的中心频率。

各个LO的状态可以独立查询和配置。 使用以下 API 调用来执行此操作:

multi_usrp API:

- uhd::usrp::multi_usrp::get_rx_lo_freq()

- uhd::usrp::multi_usrp::get_rx_lo_freq_range()

- uhd::usrp::multi_usrp::set_rx_lo_freq()

- uhd::usrp::multi_usrp::get_tx_lo_freq()

- uhd::usrp::multi_usrp::get_tx_lo_freq_range()

- uhd::usrp::multi_usrp::set_tx_lo_freq()

RFNoC API:

- uhd::rfnoc::radio_control::get_rx_lo_freq()

- uhd::rfnoc::radio_control::get_rx_lo_freq_range()

- uhd::rfnoc::radio_control::set_rx_lo_freq()

- uhd::rfnoc::radio_control::get_tx_lo_freq()

- uhd::rfnoc::radio_control::get_tx_lo_freq_range()

- uhd::rfnoc::radio_control::set_tx_lo_freq()

请注意,手动修改 LO 被视为高级行为,并且可能会导致设备状态不佳。 要撤消手动更改,请使用常规 API 调用来设置中心频率。

天线端口

ZBX 每个通道有两个 SMA 端口,称为“TX/RX0”和“RX1”。 此外,天线值可以设置为“CAL_LOOPBACK”,以将 Tx 路径环回到 Rx 路径(有时出于校准目的需要这样做)。 Rx 天线值也可以设置为“TERMINATION”以终止 Rx 路径。

使用 uhd::usrp::multi_usrp::get_rx_antennas() 或 uhd::usrp::multi_usrp::get_tx_antennas() API 调用来枚举有效的天线名称。 使用 RFNoC API 时,分别使用 uhd::rfnoc::radio_control::get_rx_antennas() 和 uhd::rfnoc::radio_control::get_tx_antennas() 调用。

状态 LED

ZBX 子板每个通道配备两个 LED,一个用于“TX/RX0”,一个用于“RX1”。 这些 LED 的行为如下:

| LED 状态 | TX/RX0 | RX1 |

|---|---|---|

| 关闭 | 端口处于非活动状态 | 端口处于非活动状态 |

| 绿色 | 端口正在接收 | 端口正在接收 |

| 红色 | 端口正在传输 | N/A |

功率校准

ZBX 支持 UHD 功率 API(另请参阅功率级别控制)。 UHD 附带标称校准数据,允许设置参考功率电平,而无需事先手动校准设备。

传感器

每个通道都有三个用于 LO 级的“锁定”传感器(lo1_locked、lo2_locked 和 nco_locked)。 名为 lo_locked 的“虚拟”传感器确认当前使用的所有 LO 均已锁定。 “NCO 锁定”传感器是一种特殊情况:NCO 不在子板上(它是 RFSoC FPGA 的一部分),但为了简化 API,它与 LO 锁定传感器放置在一起。 与子板上的(模拟)合成器不同,NCO“解锁”并不用于表示参考锁定丢失,而是表示 NCO 仍处于复位状态。

此外,ZBX还有一个温度传感器:温度。 虽然 UHD API 允许根据方向 (RX/TX) 和通道 (0/1) 对传感器进行寻址,但只有一个物理温度传感器,并且无论选择哪个通道或方向,它都会返回相同的值。

以下 API 调用可用于枚举可用传感器并查询其值:

multi_usrp API:

- uhd::usrp::multi_usrp::get_rx_sensor_names()

- uhd::usrp::multi_usrp::get_rx_sensor()

- uhd::usrp::multi_usrp::get_tx_sensor_names()

- uhd::usrp::multi_usrp::get_tx_sensor()

RFNoC API:

- uhd::rfnoc::radio_control::get_rx_sensor_names()

- uhd::rfnoc::radio_control::get_rx_sensor()

- uhd::rfnoc::radio_control::get_tx_sensor_names()

- uhd::rfnoc::radio_control::get_tx_sensor()

增益控制

ZBX 具有复杂的增益控制,能够控制总体增益或手动控制其各个增益级。 此外,板载 CPLD 还可以存储增益表,可以通过 RFNoC 命令从其他 RFNoC 模块访问该增益表。

TX 路径具有三个与增益相关的组件:两个 DSA 以及一个放大器路径。 前者的单独增益范围为 31 dB。 放大器路径允许选择两个放大器之一,一个对于较低频率具有 14 dB 的标称增益,另一个对于较高频率具有 21 dB 的标称增益。 它们的实际放大值取决于具体频率,并且也可能因设备而异。 放大器可以被旁路。

RX 路径由四个 DSA 组成,每个 DSA 的增益范围为 15 dB。

ZBX 子板的不同增益行为由增益配置文件控制,增益配置文件可以为 TX 和 RX 独立设置。 不同的增益配置文件具有不同的 API 行为,如本节其余部分所述。

要在增益配置文件之间切换,请使用 uhd::usrp::multi_usrp::set_tx_gain_profile() 或 uhd::usrp::multi_usrp::set_rx_gain_profile() API 调用。 使用 RFNoC API 时,请使用 uhd::rfnoc::radio_control::set_tx_gain_profile() 或 uhd::rfnoc::radio_control::set_rx_gain_profile() API 调用。 这些 API 之间的主要区别在于 multi_usrp API 调用允许默认通道值,而 RFNoC API 调用则不允许。

与所有其他设备一样,以下 API 调用可设置或查询增益值:

Multi USRP:

- uhd::usrp::multi_usrp::set_tx_gain()

- uhd::usrp::multi_usrp::get_tx_gain()

- uhd::usrp::multi_usrp::set_rx_gain()

- uhd::usrp::multi_usrp::get_rx_gain()

RFNoC

- uhd::rfnoc::radio_control::set_tx_gain()

- uhd::rfnoc::radio_control::get_tx_gain()

- uhd::rfnoc::radio_control::set_rx_gain()

- uhd::rfnoc::radio_control::get_rx_gain()

这些 API 调用有不同的风格,并带有可选的“增益名称”参数。 请注意,multi_usrp API 调用默认设置总体增益值,这在所有增益配置文件中都是不允许的。 所有API调用都有相应的API调用来查询允许的增益范围。

注意:ZBX 上的 RX 增益范围不一致。 低于 500 MHz,增益范围减小至 0-38 dB。 建议使用 get_rx_gain_range() 查询当前有效的增益范围。

注意:某些增益配置文件需要同时更改 TX 和 RX。 例如,从默认值更改为 table_noatr 必须同时在 TX 和 RX 上发生。 UHD 将自动相应地更改增益配置文件。 因此,建议在有疑问时调用 get_rx_gain_profile() 或 get_tx_gain_profile() 来验证正确的增益配置文件。

默认增益配置文件

该增益配置文件默认处于活动状态。 它允许设置单个标量增益值。 UHD 将在内部使用增益表来线性化整体增益(意味着增益增加 1 dB 也会使发射或接收功率增加 1 dB)。 但是,UHD 内部增益表并未针对每个设备进行校准,也未考虑温度或其他变化。

在此增益模式下,无法直接设置各个增益级,但可以将它们读回。 当尝试微调软件中的增益设置时,这可能会有所帮助。

// Assumption: 'usrp' is a multi_usrp object

usrp->set_tx_gain_profile("default"); // Only necessary if the gain profile was set to something else before

usrp->set_tx_gain(30); // Will set the gain to 30 dB on all associated daughterboards

std::cout << usrp->get_tx_gain() << std::endl; // Should print "30"

usrp->set_tx_gain(0, "DSA1"); // Will cause an exception

// Individual DSAs may still be queried. Note that even though this is an

// attenuator, the return value is a gain (higher values mean more TX power):

auto dsa1_gain = usrp->get_tx_gain("DSA1");

ATR 行为:增益将应用于各自的 ATR 状态,即 RX 增益将应用于 RX 和全双工状态,TX 增益将应用于 TX 和全双工状态。 在空闲状态下,增益设置为最小增益。

RFNoC 命令:对于给定的 ATR 状态,所有 DSA 值都位于一个寄存器中,并且 TX 放大器与天线控制共享一个寄存器。 这意味着更改此增益配置文件中的 DSA 值将导致两次寄存器写入(一次用于 RX/TX,另一次用于全双工)。 更改 TX 放大器增益值将导致另外两次写入。

手动增益配置文件

当需要更多控制时,可以应用手动增益配置文件。 在这里,不再可能请求总体增益值。 不过,现在可以直接设置 DSA 和放大器值。

usrp->set_tx_gain_profile("manual");

usrp->set_tx_gain(30); // ERROR: Now, we have to specify a name

usrp->set_tx_gain(5, "DSA1"); // Set DSA1 to 5 dB gain (equals 26 dB attenuation)

// The following line will return an undefined value and print a warning, but

// will not throw. That's because calling the overall gain is a common API call

// done by many utilities, and this behaviour is considered most backward compatible.

std::cout << usrp->get_tx_gain() << std::endl;

std::cout << usrp->get_tx_gain("DSA1") << std::endl; // Should print '5'

带 ATR 控制的 CPLD 表增益曲线

在此配置文件中,UHD 公开了对 CPLD 上存储的增益表的访问。 默认情况下,CPLD 使用与 UHD 内部使用的增益表相同的增益表进行初始化,即,使用此配置文件时,行为没有差异,除非增益表被修改。

在此配置文件中无法直接从 UHD 设置 DSA 值,也无法设置总体增益值。 不过,现在可以从 CPLD 增益表加载条目并将其应用于当前的 DSA 设置。 在此配置文件中,DSA 的 ATR 行为与“默认”或“手动”配置文件中的相同。 这意味着加载 DSA 表条目需要对 CPLD 进行两次写入,一次用于 TX/RX,一次用于全双工。

增益“值”不再解释为 dB 值,而是参考 DSA 表索引。

此增益曲线的一个重要用例是测试 CPLD 增益表,但不更改软件控制的其他方面。 通常,这是开发使用 RFNoC 命令控制增益的应用程序时的中间调试步骤。

此配置文件的另一个用例是运行 RFNoC 应用程序时,其中增益由另一个 RFNoC 模块控制,但 ATR 行为保持默认状态。

usrp->set_tx_gain_profile("table");

usrp->set_tx_gain(30); // ERROR: Now, we have to specify a name

usrp->get_radio_control().set_tx_gain(5); // This works, though. The radio_control

// object is smart enough to infer that

// this is the only action left.

// The previous line and the following have the same effect:

usrp->set_tx_gain(5, "TABLE");

// The CPLD DSA table entry at index 5 is now loaded and applied to the TX and

// full-duplex ATR modes. In other words, the register values TX0_TABLE_DSA*

// are copied to TX0_DSA*.

// The following line will return an undefined value and print a warning, but

// will not throw. That's because calling the overall gain is a common API call

// done by many utilities, and this behaviour is considered most backward compatible.

std::cout << usrp->get_tx_gain() << std::endl;

// The following line will print the actual value of DSA1. Note, however, that

// UHD needs to read back the value from the CPLD, since it can't know what's

// stored on the CPLD. That means the following call will require a read from

// the CPLD, which is not possible if there are timed commands queued up.

std::cout << usrp->get_tx_gain("DSA1") << std::endl; // Should print whatever

// was originally stored

// in TX0_TABLE_DSA1, which

// was copied to TX0_DSA1

无 ATR 控制的 CPLD 表增益曲线

当运行 FPGA 完全控制增益的应用程序并且 ATR 行为也应由寄存器写入替代时,可以使用此配置文件。

与之前的配置文件的主要区别在于,当无线电在 RX、TX、全双工和空闲状态之间切换时,不会自动更新增益值。 相反,当前增益值是通过写入 SW_RF0_DSA_CONFIG 和 SW_RF1_DSA_CONFIG 寄存器来选择的。 更改这些寄存器将从 RX/TX DSA 表中选择一个条目。 与增益表不同,这些表不是预先填充的。

usrp->set_tx_gain_profile("table_noatr");

usrp->set_tx_gain(30); // ERROR: Now, we have to specify a name

usrp->get_radio_control().set_tx_gain(5); // This works, though. The radio_control

// object is smart enough to infer that

// this is the only action left.

// The previous line and the following have the same effect (but it's a different

// effect than when using gain profile 'table'):

usrp->set_tx_gain(5, "TABLE");

// The CPLD SW_RF0_DSA_CONFIG register is now set to 5. That means the DSA values

// stored in TX0_DSA1[5] and TX0_DSA2[5] are now being used, assuming no other

// entity is sending commands to the CPLD via RFNoC.

// Copying CPLD gain table entries into the TX0_DSA* registers is not possible

// from software in this profile. Rather, we are hands-off and let the FPGA take

// control.

//

// Let's assume that an RFNoC block has sent register writes to the radio block

// in order to load new gain table entries, and apply them. We can still read

// back the current DSA values (the ones being currently used on the RF chain)

// by reading back from the CPLD.

// This is not possible if there are timed commands queued up.

std::cout << usrp->get_tx_gain("DSA1") << std::endl; // Should print whatever

// is currently in TX0_DSA1[i],

// where i is the value of

// SW_RF0_DSA_CONFIG.

自动发送接收寄存器 (ATR)

与其他 USRP 一样,X410 为子板提供 GPIO,用于传达 RX/TX 状态。 默认情况下,ZBX 配置为根据当前状态(RX、TX、全双工、空闲)切换设置。 例如,TX/RX天线根据状态在TX和RX信道之间切换。 主板 FPGA 和子板 CPLD 之间总共有 4 个 GPIO 用于此目的,每个通道两个引脚。

ZBX 使用这些引脚在不同的 RF 控制值(例如,前面提到的 TX/RX 天线开关位置;这还包括前面板 LED)以及 DSA 控制(例如,仅进行 RX 时,TX 增益级可以 设置为零以最大限度地减少泄漏)。 在内部,这是通过将 ATR 引脚转换为控制字来实现的。 该控制字用于索引包含 RF 控制/LED 以及 DSA 的不同值的表。

示例:假设设备正在通道 0 上发送但未接收。FPGA 会将通道 0 的 ATR 引脚设置为二进制值 0b10,该值等于十进制值 2。发送增益由 DSA 值控制, 分别存储在名为 TX0_DSA1 和 TX0_DSA2 的表中。 因此,在传输期间,将使用表位置 TX0_DSA1[2] 和 TX0_DSA2[2] 处的 DSA 值。 同样,射频路径控制表和 LED 也用于配置它们。 这种使用 ATR 引脚的模式称为“经典 ATR”模式,并且是默认行为。

ZBX 子板提供了两种使用这些引脚的附加模式:

“软件定义”:在此模式下,ATR 引脚被忽略。 控制字来自另一个寄存器。 在这种情况下,更改表索引需要另一次寄存器写入,而不是在其他模式下几乎瞬时跟踪 ATR 状态。

“FPGA 控制”:这与经典的 ATR 模式类似,但它结合了通道 0 和 1 的引脚。缺点是通道 0 和 1 不再独立,但它允许使用表中的 16 个条目,而不是 4 个 与经典 ATR 模式一样。

ATR 引脚模式可以为通道 0 和 1 以及 DSA 表与 RF 控制/LED 表单独设置。 请注意,将一个通道上的“FPGA 控制”模式与另一通道上的“经典”模式组合可能会产生冲突的配置。

这些模式的使用被认为是 ZBX 的高度高级使用。 如果没有自定义修改,UHD 不支持“FPGA 控制”模式(但是,可以手动写入适当的寄存器以使用此模式)。 使用此模式还需要修改 FPGA 映像,以向 ATR GPIO 引脚添加自定义控件。

可以使用 table_noatr 增益配置文件为 DSA 表启用“软件定义”模式(请参阅上一节)。

更新ZBX CPLD

注意:更新文件系统后,您可能需要更新 ZBX CPLD。 如果需要更新,MPM 将无法初始化,并提供相应的错误消息。

如果需要更新ZBX CPLD,可以通过在设备上运行以下命令来完成:

zbx_update_cpld

默认情况下,此命令将使用默认路径中的映像更新两个子板上的 CPLD。 要指定要编程的映像或子板,请使用以下选项:

- –dboards=0,1

- –file=<cpld_image 路径>

默认情况下,cpld-zbx.rpd 文件将在 /lib/firmware/ni/cpld-zbx.rpd 中提供。 请注意,下载 ZBX CPLD 后,您需要完全关闭并重新启动设备。

如果您在文件系统更新期间更新映像,即在使用 Mender 安装新文件系统后但在重新启动之前,您需要先挂载新文件系统并将映像复制到:

mkdir /mnt/other

mount /dev/mmcblk0p3 /mnt/other

cp /mnt/other/lib/firmware/ni/cpld-zbx.rpd ~

umount /mnt/other

请注意,其他文件系统可能是 /dev/mmcblk0p2 或 /dev/mmcblk0p3。 您现在可以更新到新的 CPLD 映像:

zbx_update_cpld --file=~/cpld-zbx.rpd

CPLD 编程:详细信息

如果您想创建自己的 ZBX CPLD 映像,或者需要有关如何更新 CPLD 映像的更多信息,请阅读本节。

ZBX CPLD 的源代码在 UHD 代码存储库中提供,地址为 fpga/usrp3/top/x400/dboards/zbx/cpld。 阅读 Makefile 以获取有关如何构建映像的更多说明。

构建过程将生成两个 CPLD 位文件:一个 .rpd 文件和一个 .svf 文件。 不同的编程方法需要两者。 有两种编程方法:

Flash 模式:这需要 .rpd 文件。 它使用主板CPLD作为编程设备。 这是默认模式。

传统模式:直接调用 openocd 来刷新 ZBX CPLD。 它需要 .svf 文件。

在运行更新程序之前,请确保您的设备上安装了 MPM,因为使用了 MPM 代码中的一些资源。

您还应该确保子板的电源轨已启动,并且 MPM 在运行时可以成功与子板通信(成功运行 uhd_usrp_probe 就足够了)。

执行更新程序脚本时,MPM 不需要运行,但在尝试执行此操作之前,您应该启动它一次,以确保加载有效的 FPGA 映像并且与子板的通信正常。

要指定编程模式,请使用 --updater 参数。 例如,要强制使用传统模式,请使用以下命令:

zbx_update_cpld --updater=legacy --file=/lib/firmware/ni/cpld-zbx.svf

这将使用“传统”方法将图像从默认位置编程到 CPLD 上。

闪存和EEPROM

每个 ZBX 子板都有 2 MB 的非易失性闪存,可用于存储子板特定信息等数据。 当登录到 X410 Linux 系统时,闪存将分别挂载到 /mnt/db0_flash 和 /mnt/db1_flash 下的文件系统中。 子板还使用单独的 EEPROM 来存储子板的版本号、序列号和产品 ID。

全系列 检索列表

【USRP】产品型号、参数、架构全解析系列 1:B200 / B210 / B200mini / B205mini

【USRP】产品型号、参数、架构全解析系列 2:E310 / E312 / E313

【USRP】产品型号、参数、架构全解析系列 3:E320

【USRP】产品型号、参数、架构全解析系列 4:N200 / N210

【USRP】产品型号、参数、架构全解析系列 5:N300 / N310

【USRP】产品型号、参数、架构全解析系列 6:N320 / N321

【USRP】产品型号、参数、架构全解析系列 7:X300 / X310

【USRP】产品型号、参数、架构全解析系列 8:USRP-2974

【USRP】产品型号、参数、架构全解析系列 9:X410

【USRP】产品型号、参数、架构全解析系列 10:X440

USRP 调制解调系列连载

【USRP】调制解调系列1:AM、FM解调

【USRP】调制解调系列2:2ASK、4ASK,基于labview的实现

【USRP】调制解调系列3:2FSK、4FSK、8FSK,基于labview的实现

【USRP】调制解调系列4:BPSK、QPSK、8PSK、OQPSK、Pi/4DQPSK,基于labview的实现

【USRP】调制解调系列5:16QAM、32QAM、64QAM、256QAM、1024QAM、基于labview的实现

【USRP】调制解调系列6:16APSK、32APSK 、基于labview的实现

【USRP】调制解调系列7:GMSK、MSK、基于labview的实现

USRP 仪器 连载系列

【USRP】集成化仪器系列1 :信号源,基于labview实现

【USRP】集成化仪器系列2 :示波器,基于labview实现

【USRP】集成化仪器系列3 :频谱仪,基于labview实现

849

849

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?