| 第一节:存储系统——基本概念 |

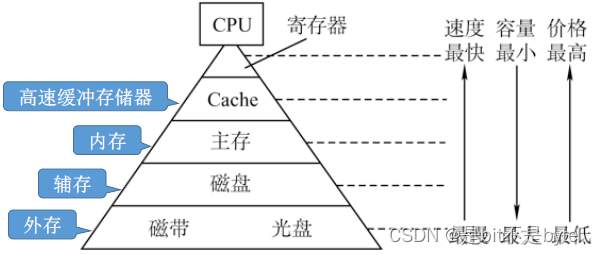

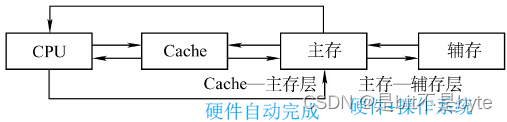

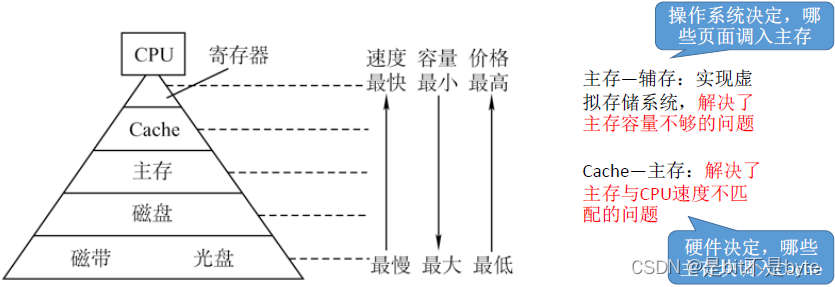

| 存储器的层次结构 |

| ||||||||||||||||||||||||||||||||||

| 存储器的分类 |

| ||||||||||||||||||||||||||||||||||

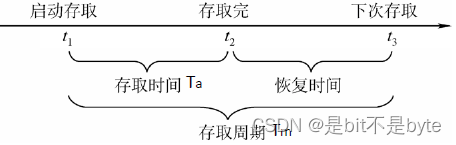

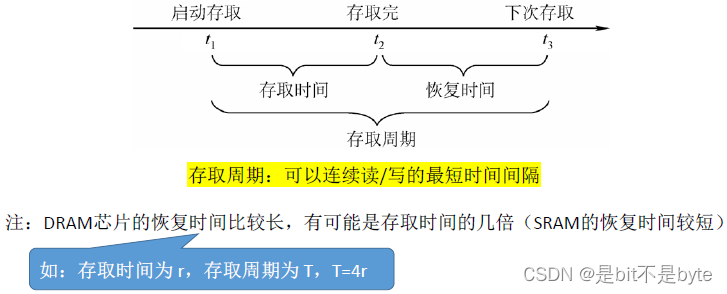

| 存储器的性能指标 |

|

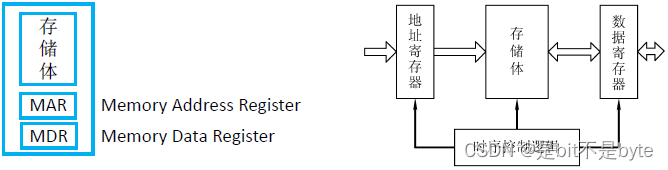

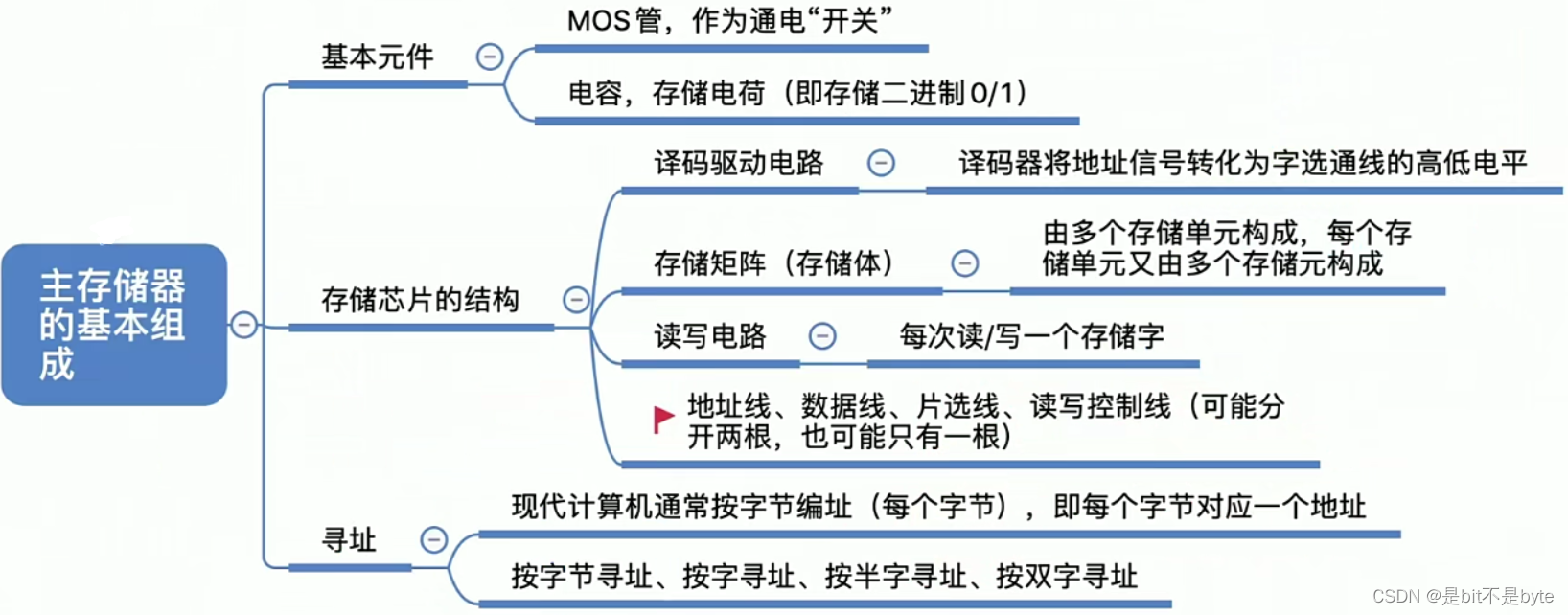

| 第二节:主存储器的基本组成 |

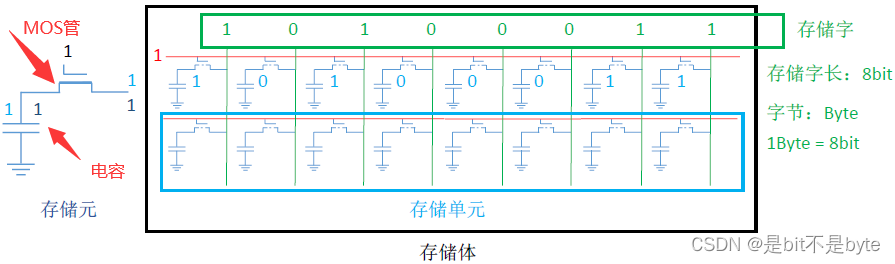

| 半导体元件的原理 |

| |||||||||||||||||||||||||||||||||

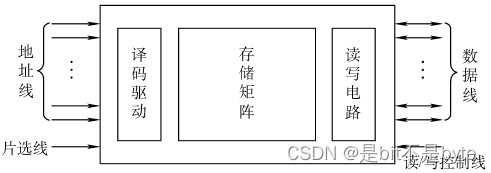

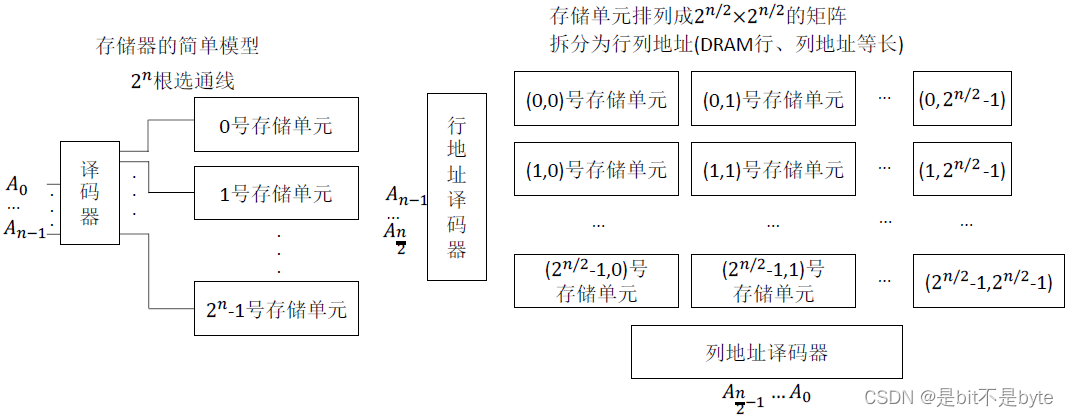

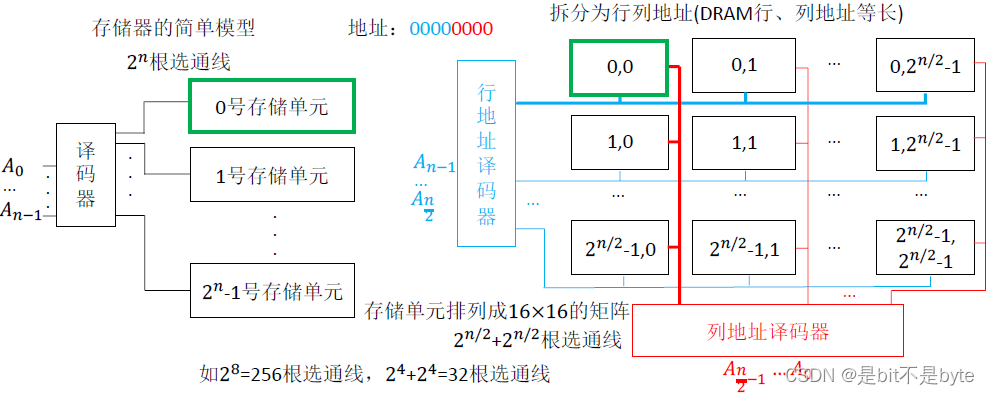

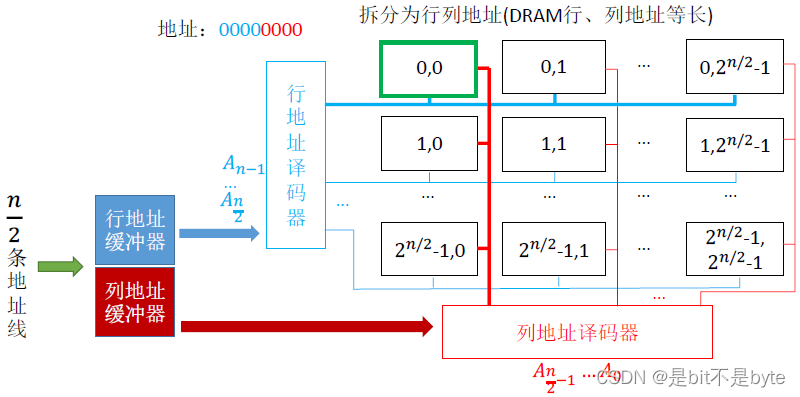

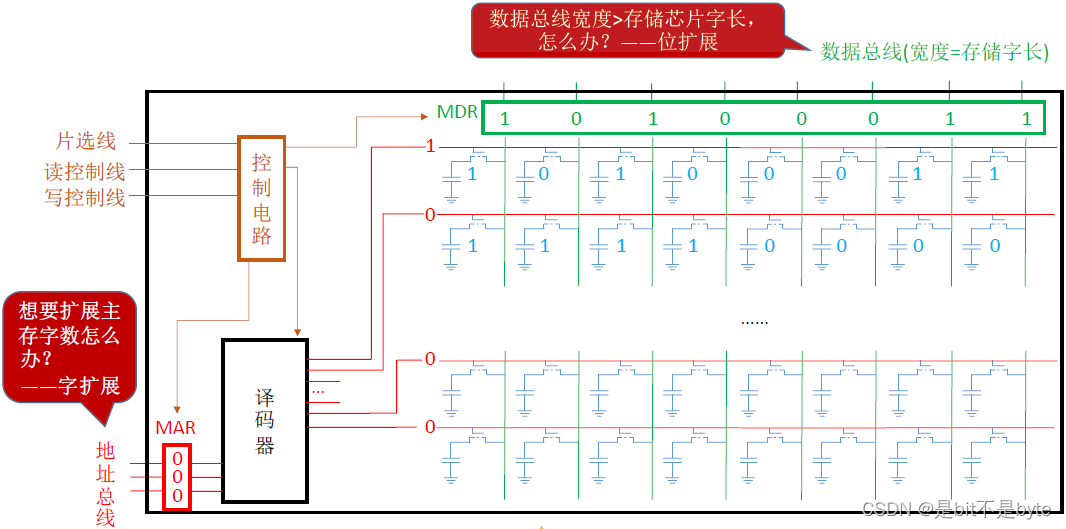

| 存储芯片的基本原理 |

| |||||||||||||||||||||||||||||||||

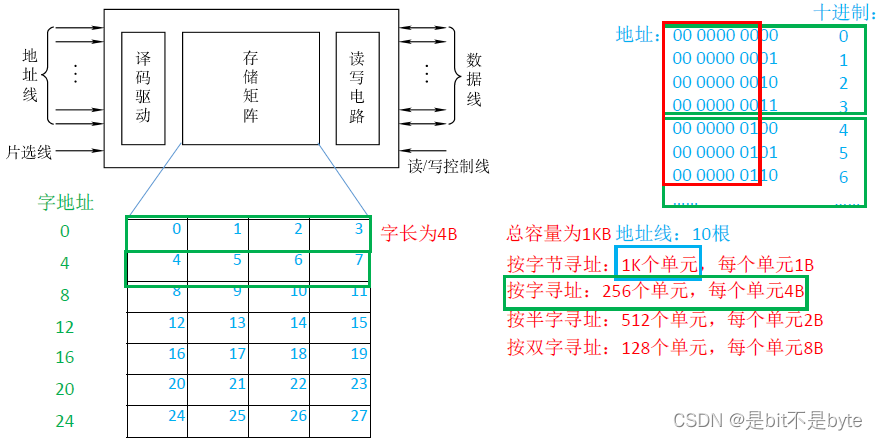

| 如何实现不同的寻址方式 |

如果按字寻址,因为一个字占4个字节,那么只要把字地址算数左移两位就把字地址转换为与之对应的字节地址,假如要访问1号字,那算数左移两位即100即为十进制的4,也就是对应的字节地址 |

|

|

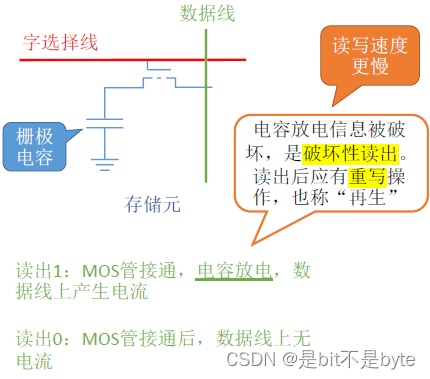

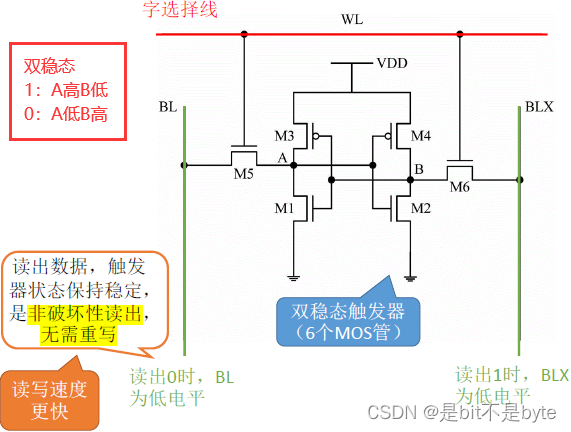

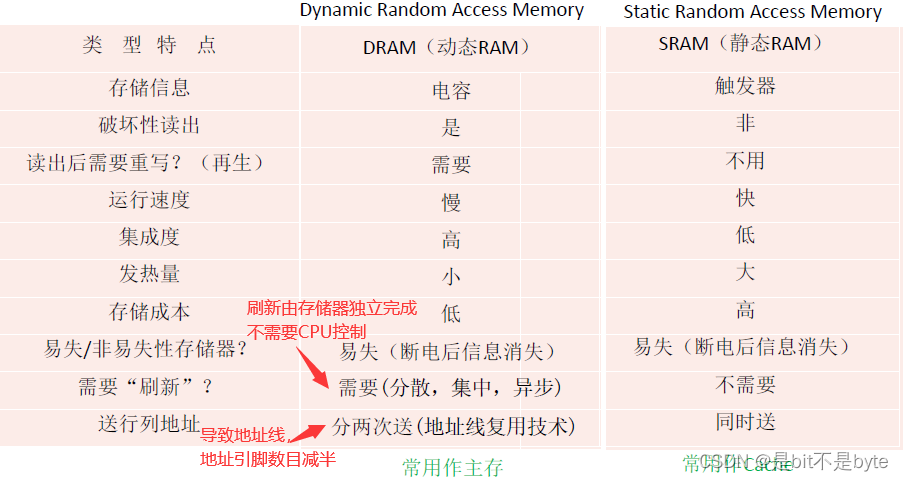

| 第三节:DRAM和SRAM |

| Dynamic Random Access Memory,即动态RAM Static Random Access Memory,即静态RAM | DRAM用于主存、SRAM用于Cache 高频考点:DRAM和SRAM的对比 |

| DRAM也已经过时,现在采用SDRAM芯片,如DDR3,DDR4,它们都属于SDRAM芯片 |

| 存储元件不同导致的特性差异 |

| ||||||||||||||||||||||||||

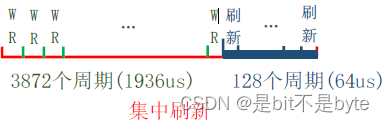

| DRAM的刷新 |

| ||||||||||||||||||||||||||

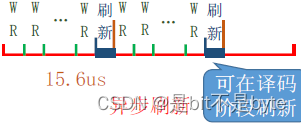

| DRAM的地址线复用技术 | DRAM分两次送行,列地址,可使地址线更少,芯片引脚更少【地址线,地址引脚数量减半】

|

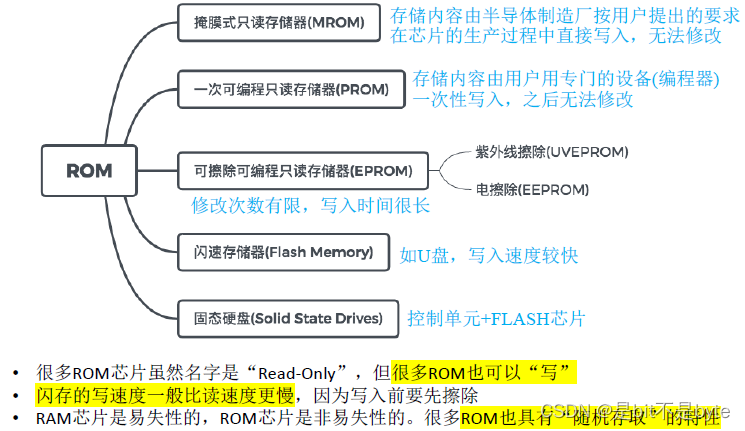

| 第四节:只读存储器ROM |

| RAM芯片 | 易失性,断电后数据消失 |

| ROM芯片 | 非易失性,断电后数据不会丢失 |

| 了解各种ROM |

| ||||||||||||||

| 计算机内的重要ROM |

|

|

|

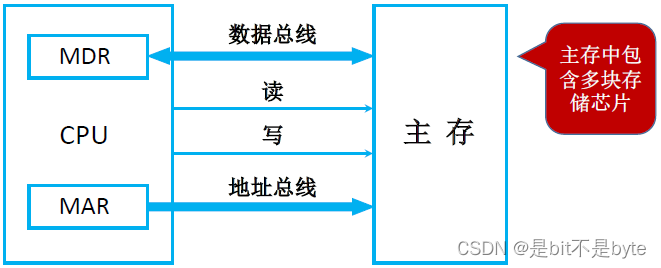

| 第五节:主存储器与CPU的连接 |

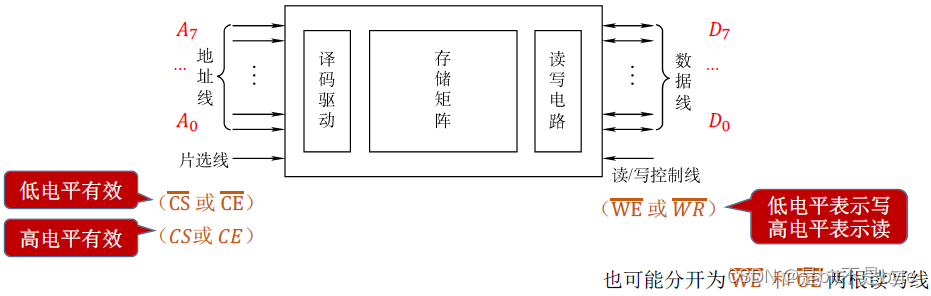

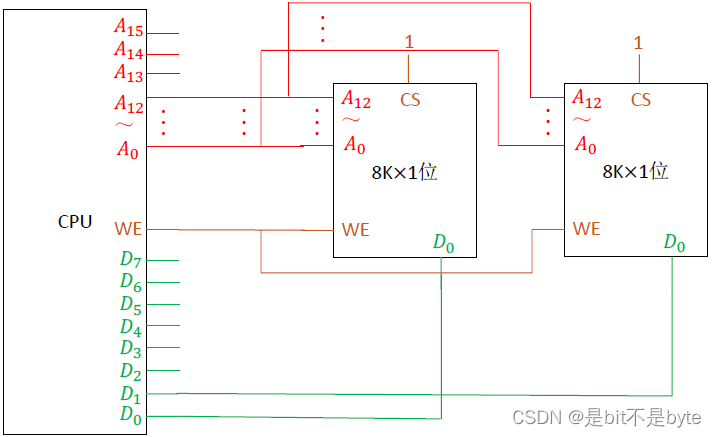

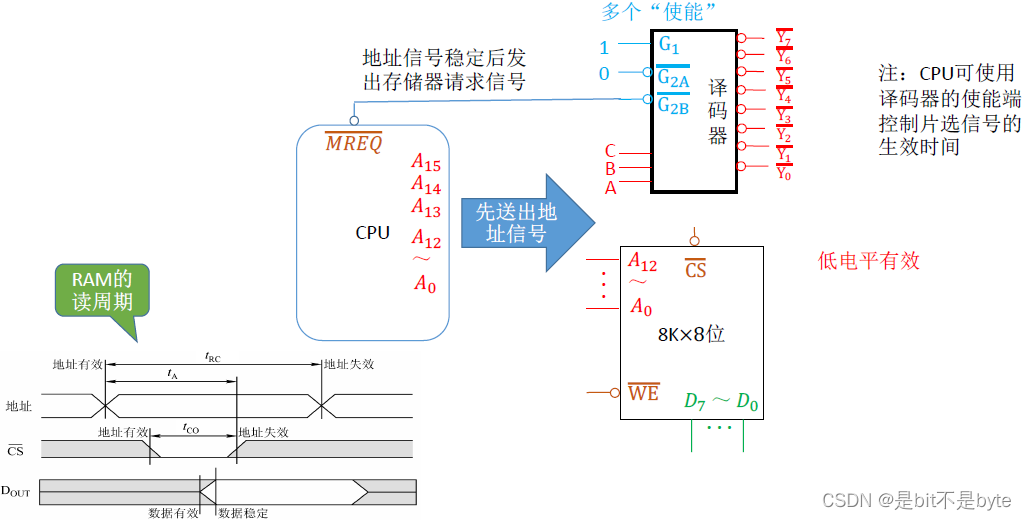

| 单块存储芯片与CPU的连接 |

| |||||||||||||||||||||||||||||

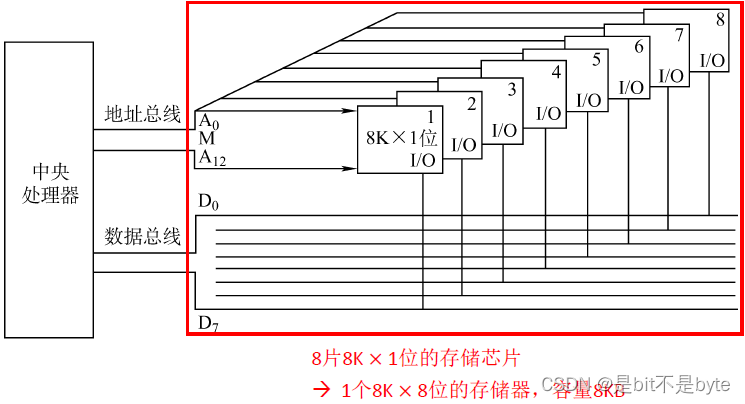

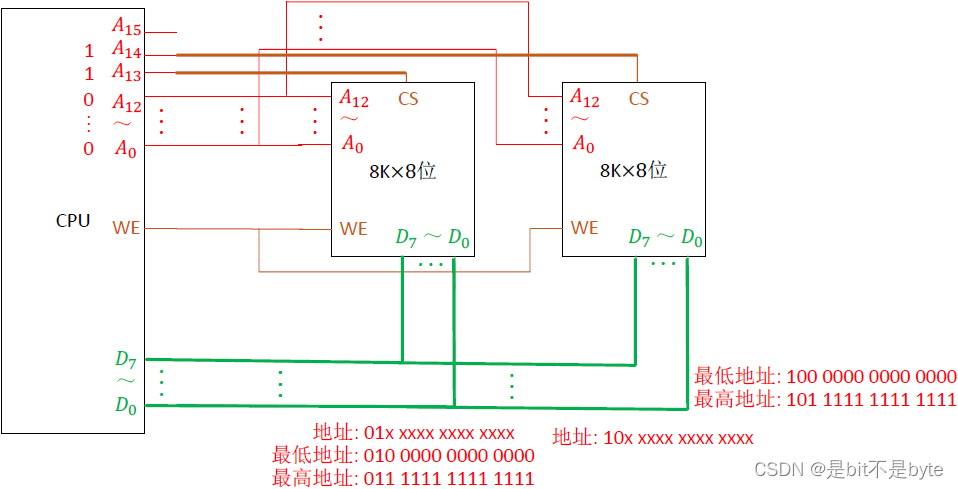

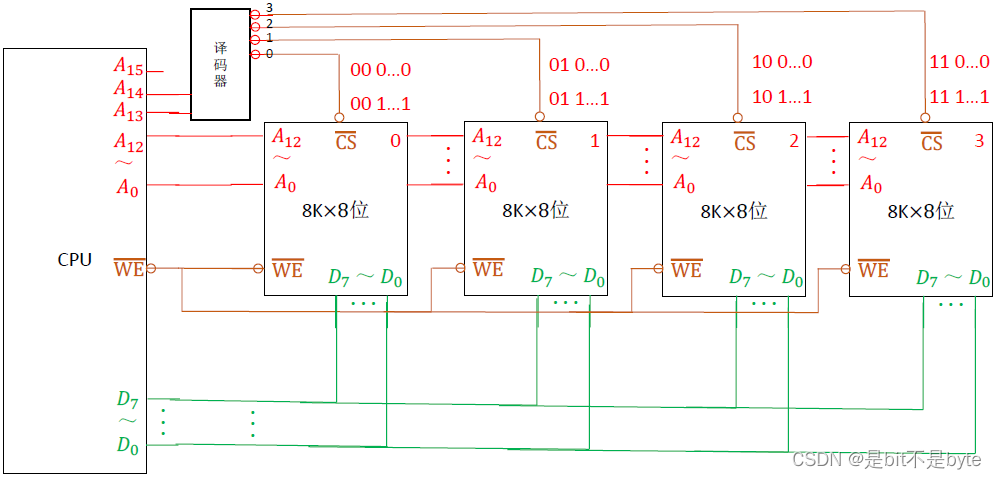

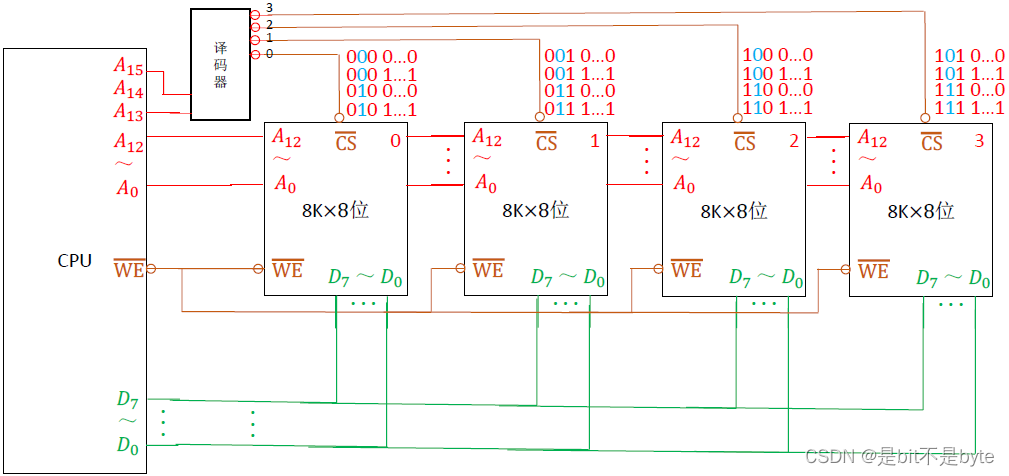

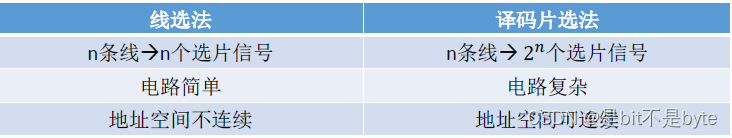

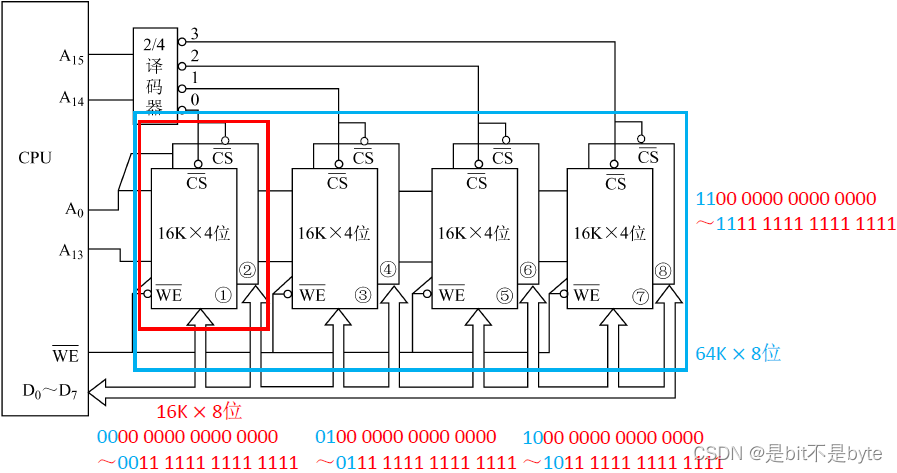

| 多块存储芯片与CPU的连接 |

| |||||||||||||||||||||||||||||

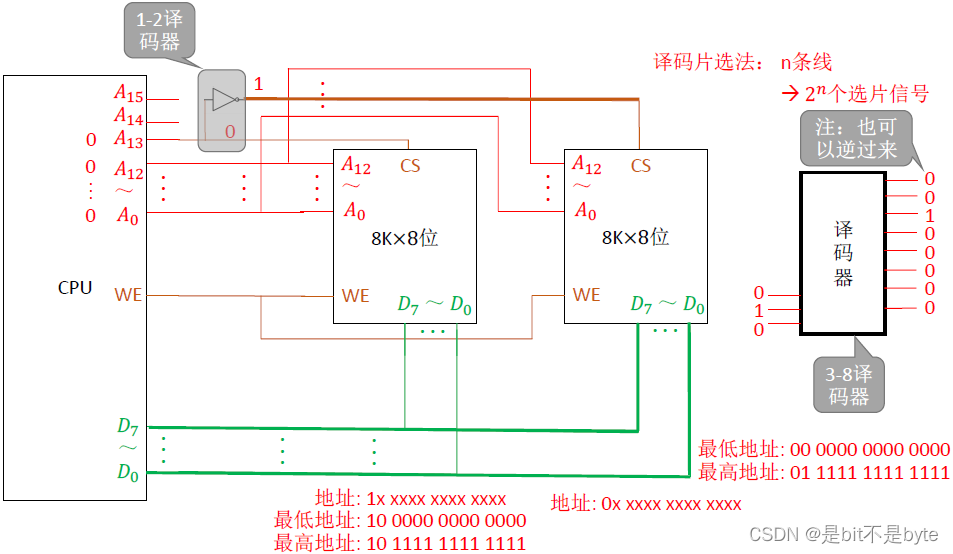

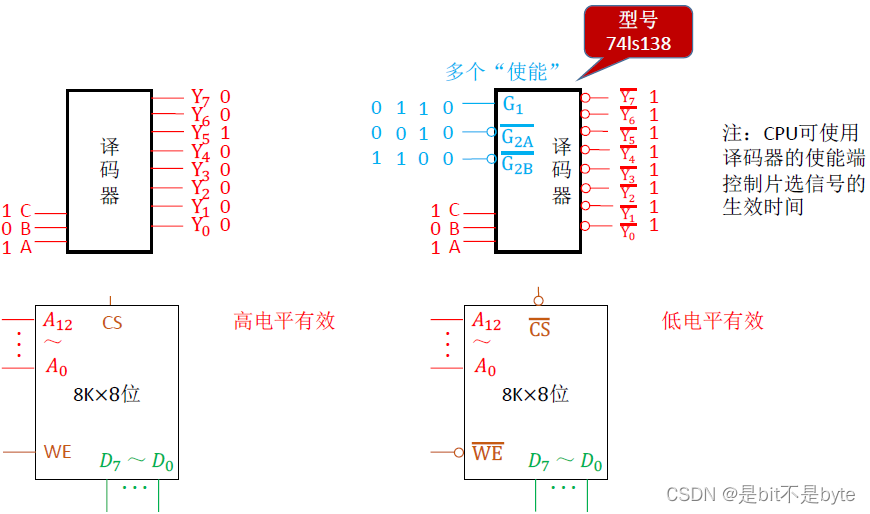

| 关于译码器知识的补充 |

|

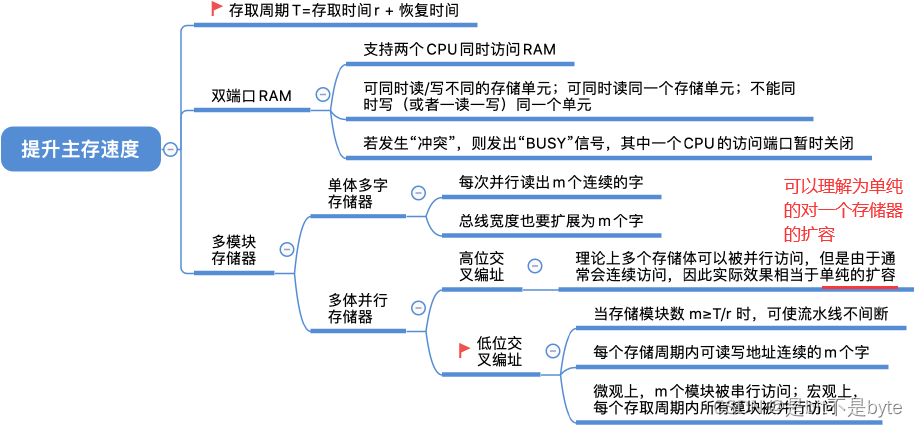

| 第六节:双端口RAM&多模块存储器——对于主存提升CPU访问主存速度的方法 |

| 问题 |

| ||||||||||||||||||||||||||||||

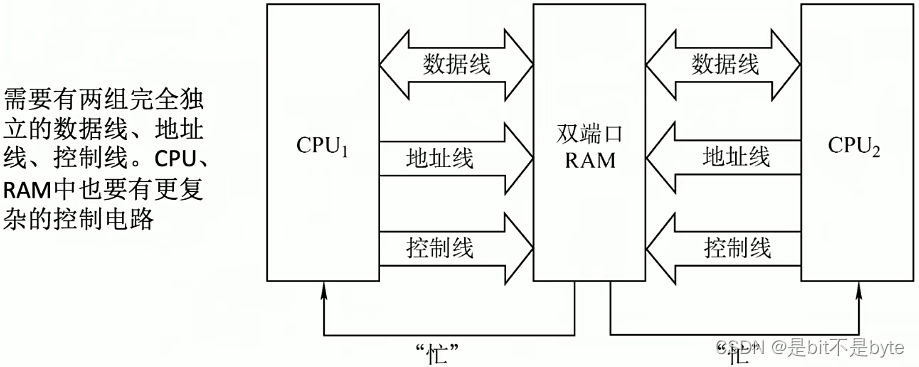

| 双端口RAM |

| ||||||||||||||||||||||||||||||

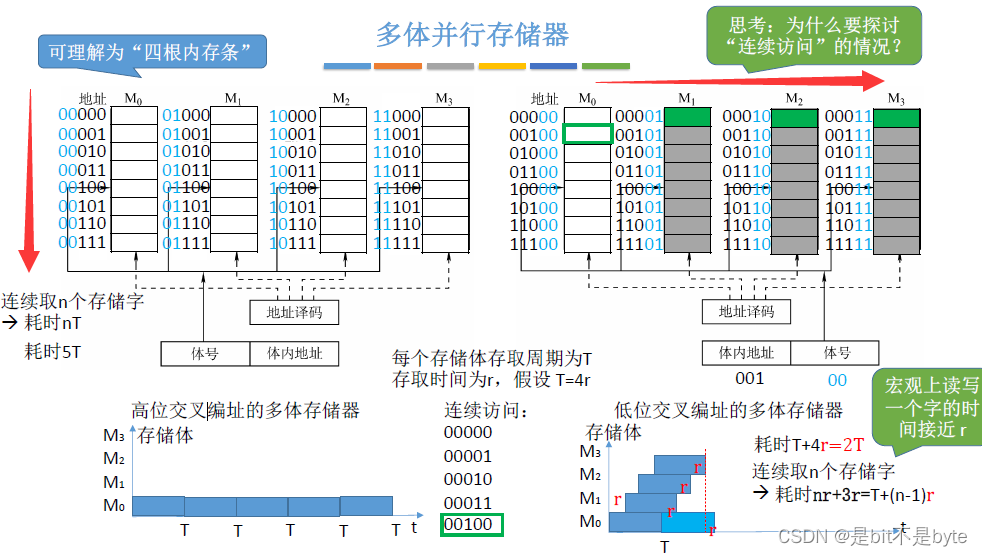

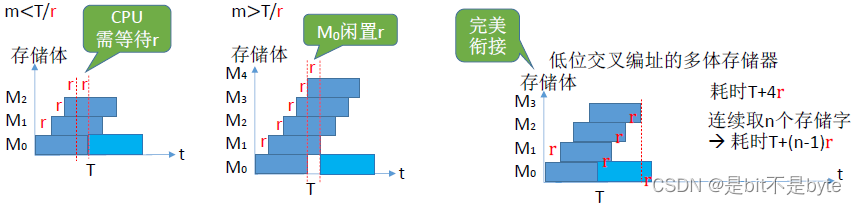

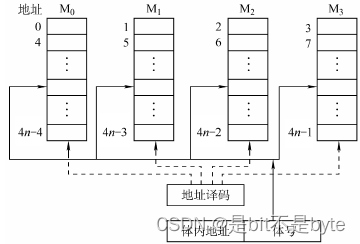

| 多模块存储器 多体并行存储器 |

|

|

如何插入内存条,实现高位交叉的多体存储器(相当于单纯的扩容)? 如何插入内存条,实现低位交叉的多体存储器(俗称“双通道”)? Tips:买内存条时,可挑选相同主频(1/读写周期T)、相同容量的两根来组成双通道 ①如果两根主频不一样的内存条,其中高主频的内存条会进行降频处理,发挥不出功效 ②如果不同容量的两根内存条,低地址部分构成双通道,高地址部分依然是单通道,会造成性能不太稳定 |

| ⭐第七节:高速缓冲器Cache |

| Cache基本原理基本概念 |

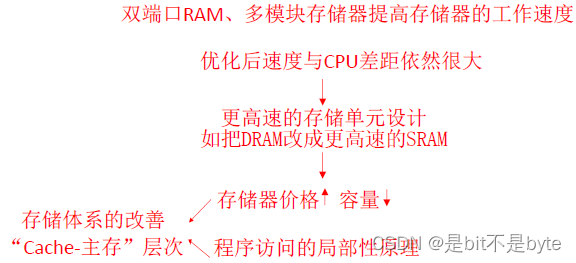

| 存储系统存在的问题 |

| ||||||||

| 局部性原理 |

| ||||||||

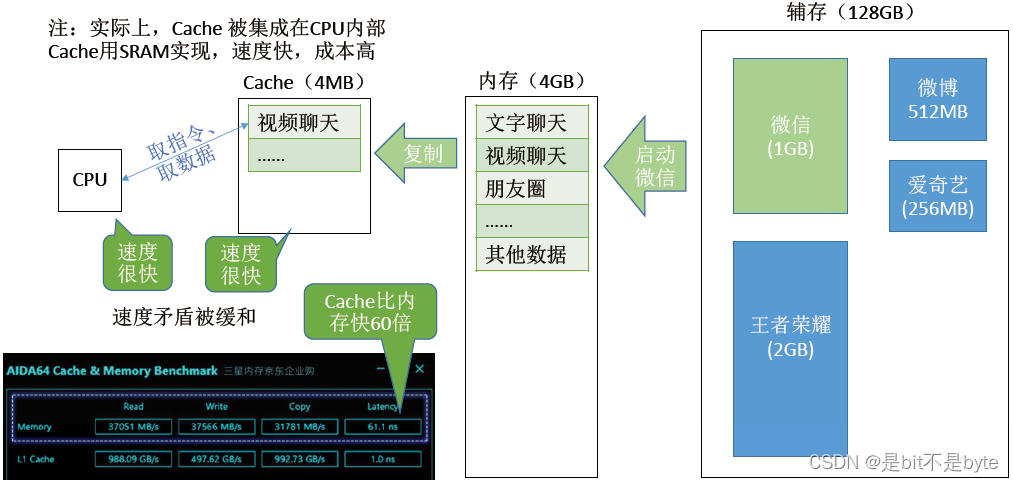

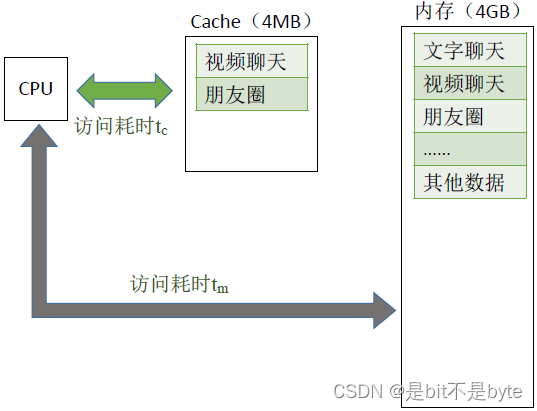

| Cache的工作原理 |

| ||||||||

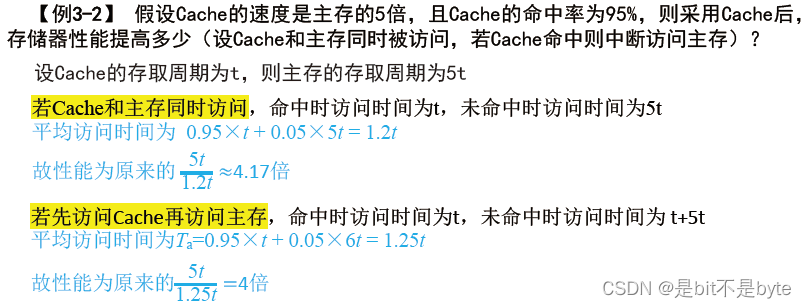

| 性能 分析 |

| ||||||||

| 存在的问题 |

|

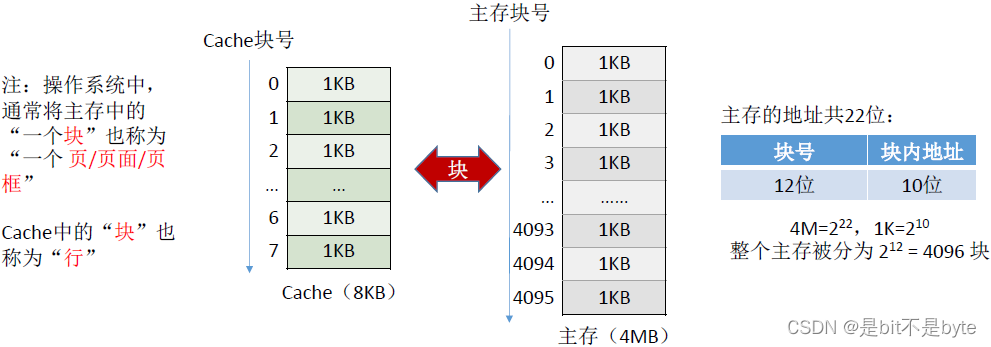

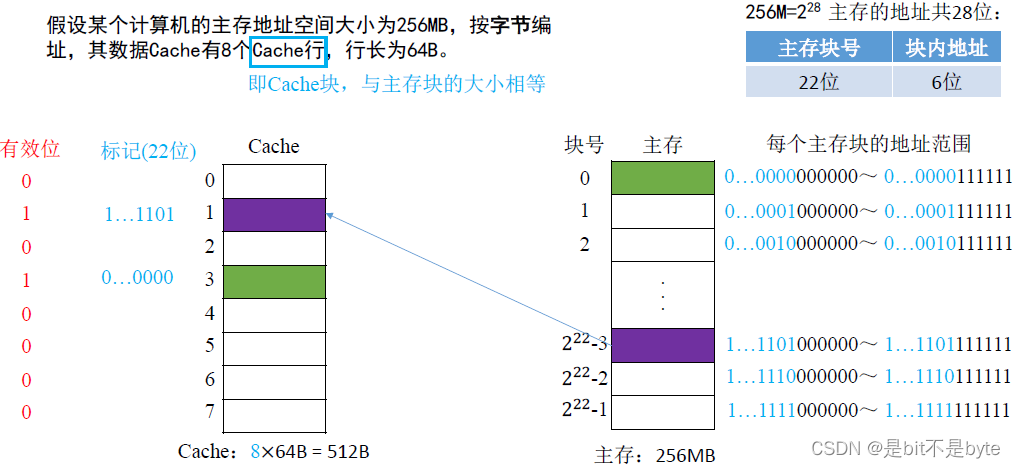

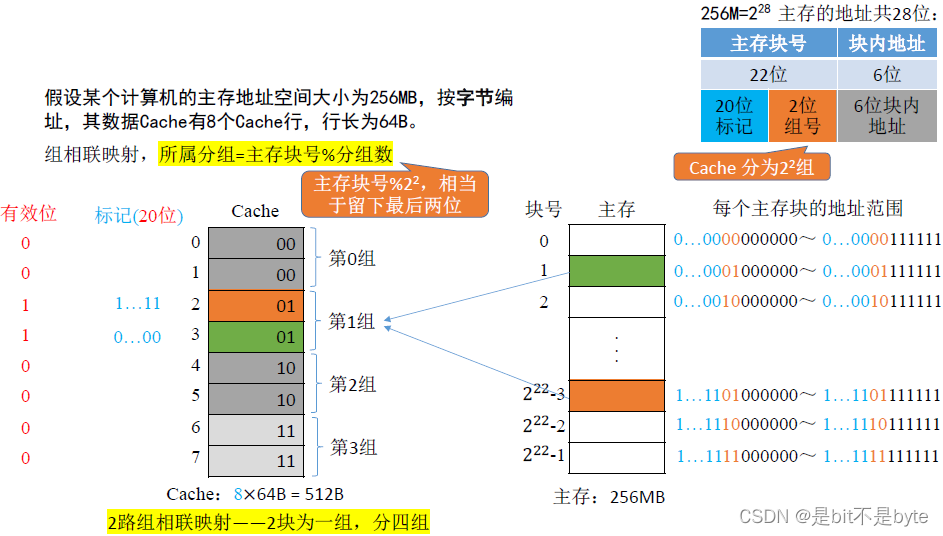

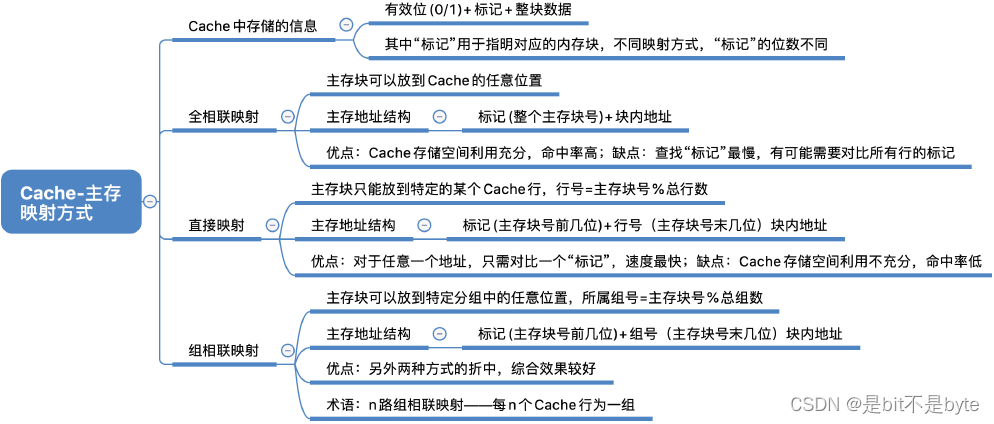

| Cache和主存的映射方式(重点) |

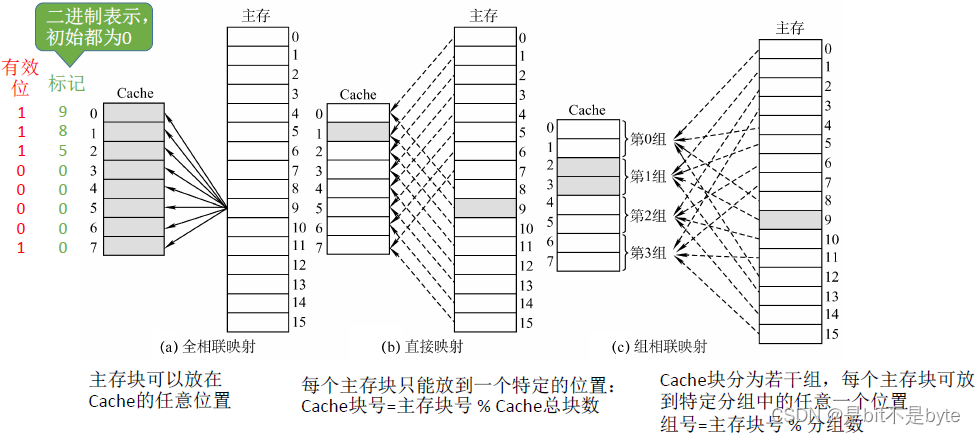

| 三种映射方式 |

|

| 全相联映射 |

| ||||||||||||||||

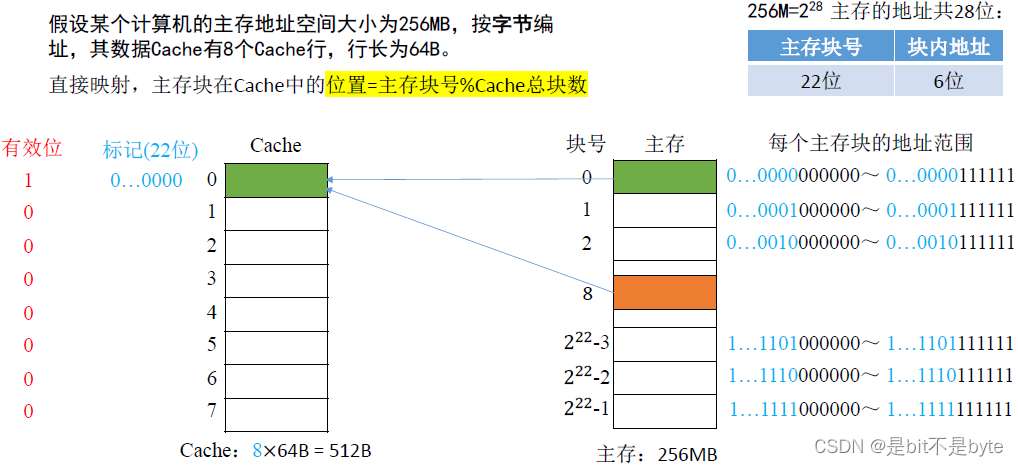

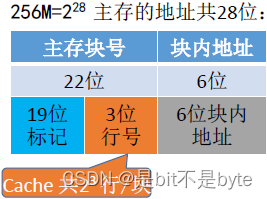

| 直接相联映射 |

| ||||||||||||||||

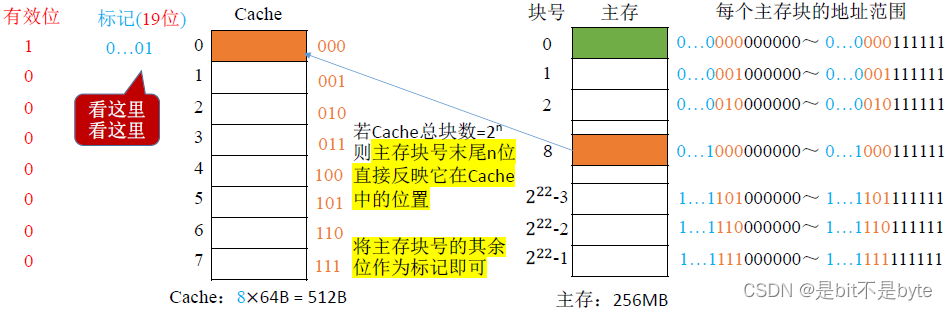

| 组相联映射 |

|

|

结合每种地址映射方式的地址结构思考:给定一个主存地址,如何拆分地址,并查找Cache、访存? |

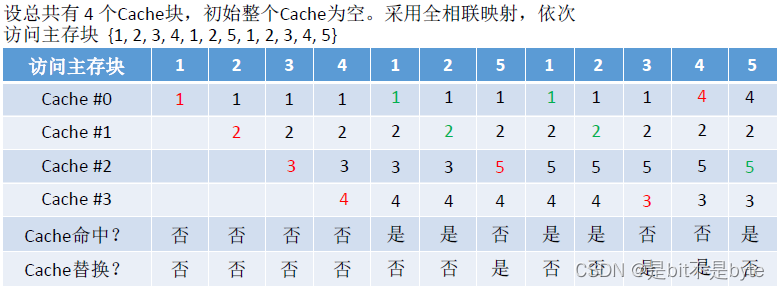

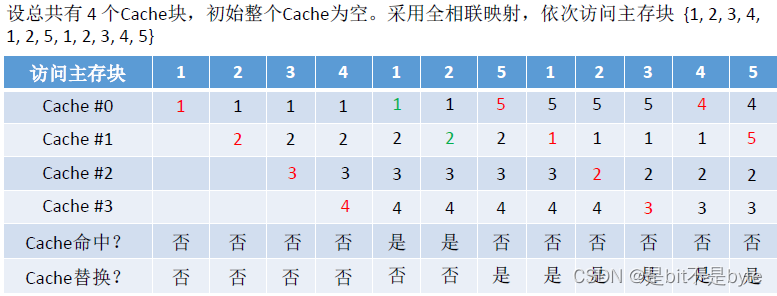

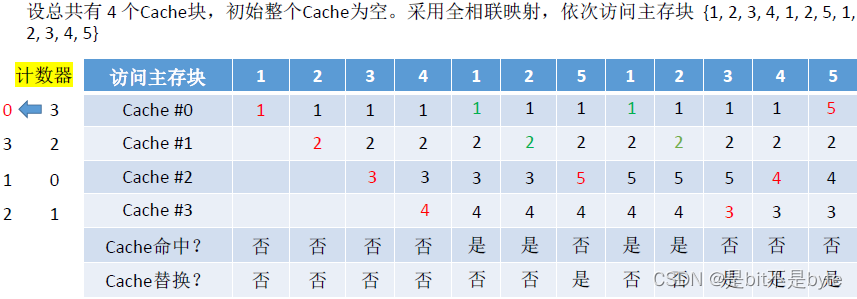

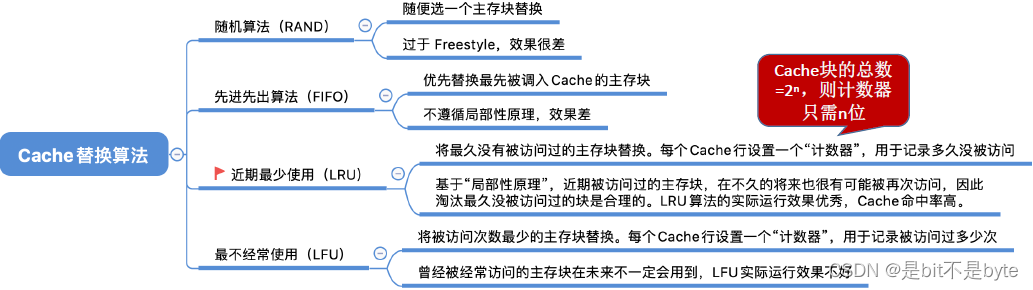

| 替换算法 |

| 三种 情况 |

| ||||||

| 注意 | 每次被访问的主存块,一定会被调入Cache,所以我们需要Cache替换算法 |

| Cache替换 算法 |

|

|

|

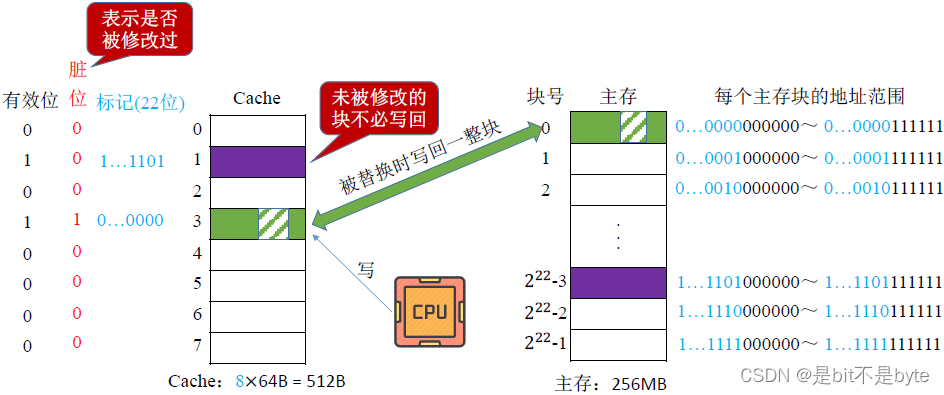

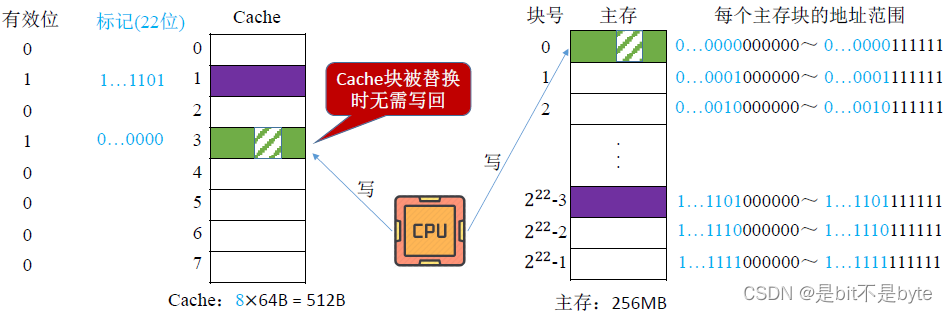

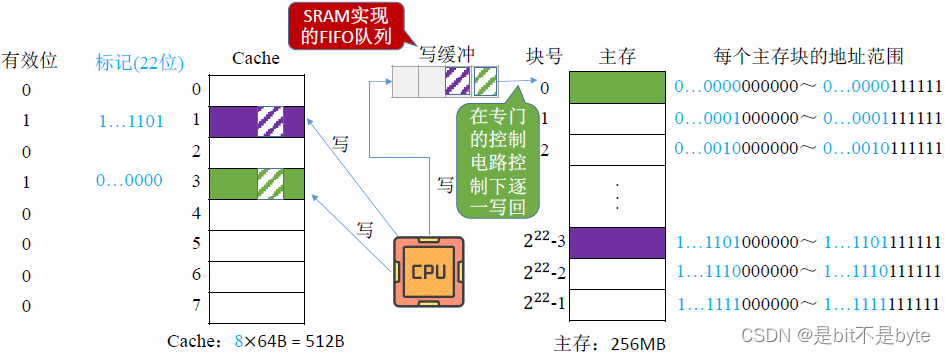

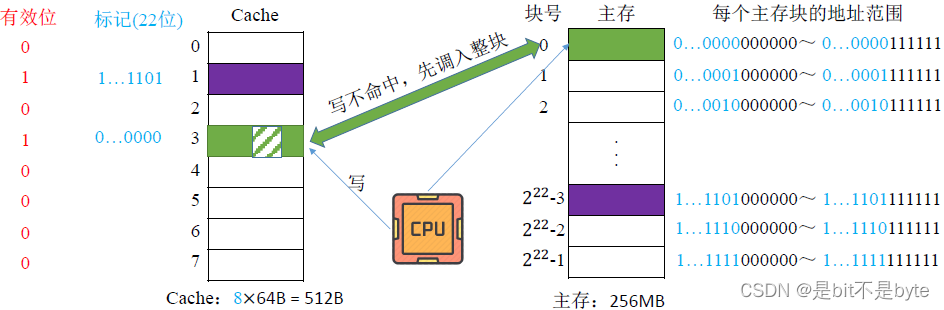

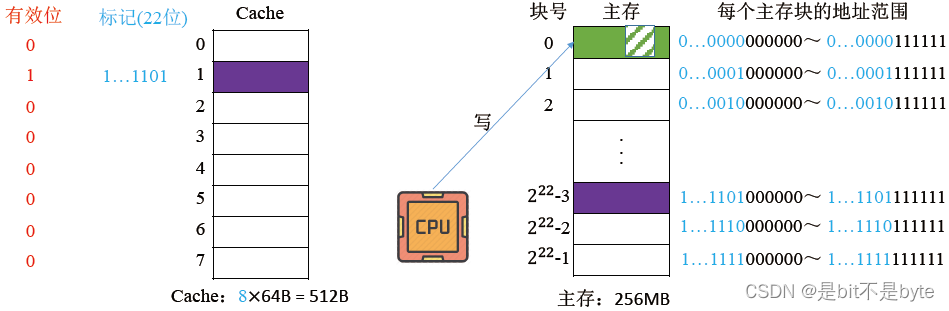

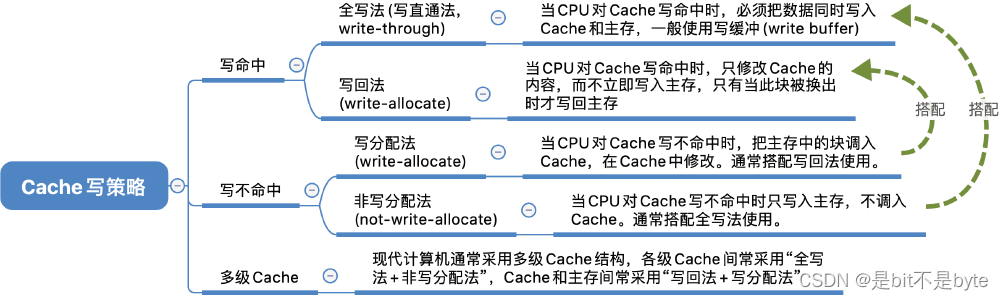

| Cache写策略 |

| 写命中 |

| |||||||||||||||||||||||

| 写不 命中 |

| |||||||||||||||||||||||

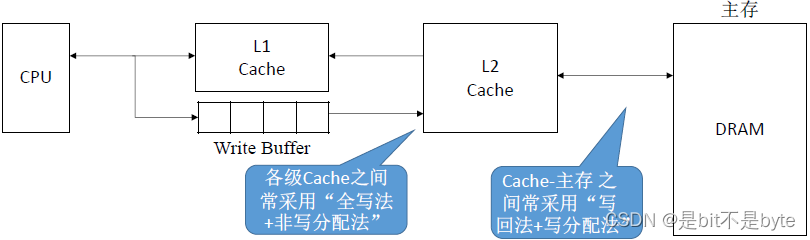

| 多级Cache |

|

|

|

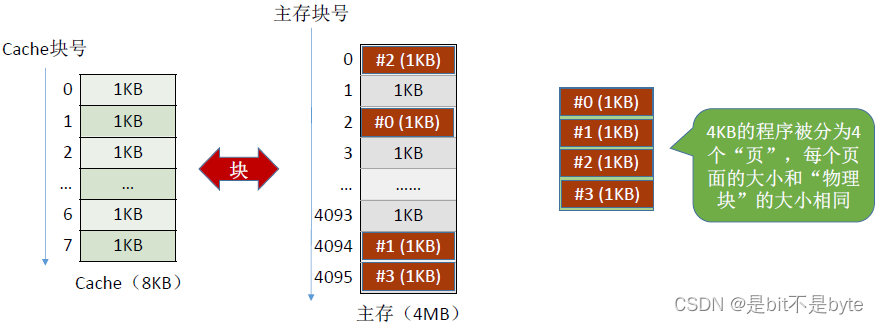

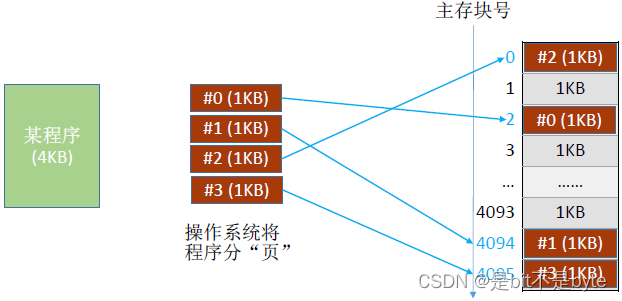

| 第八节:页式存储器 |

| 页式 存储 |

| |||||||||||||||||||||||

| 页式存储系统 | 一个程序(进程)在逻辑上被分为若干个大小相等的“页面”,“页面”大小与“块”的大小相同。每个页面可以离散地放入不同的主存块中 | |||||||||||||||||||||||

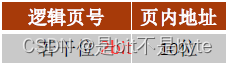

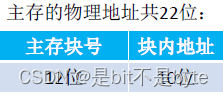

| 虚地址 |

| |||||||||||||||||||||||

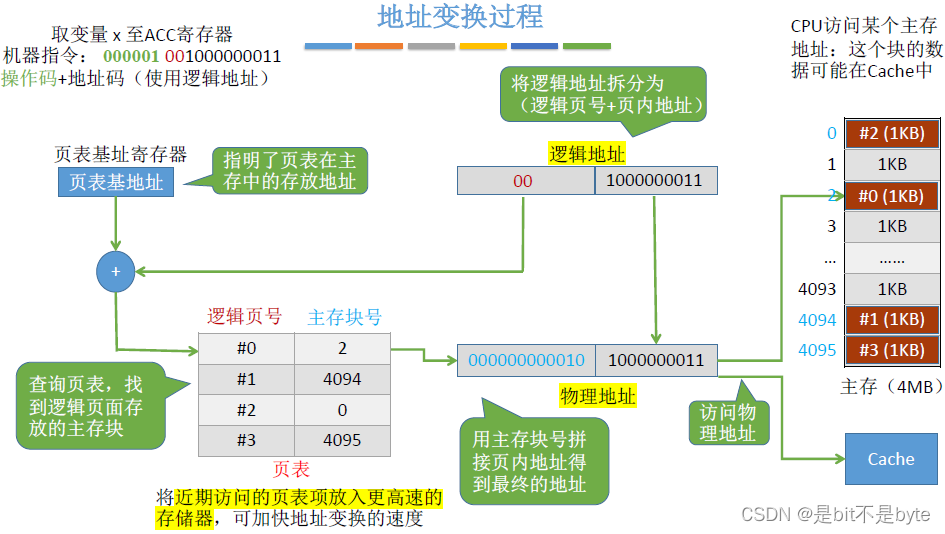

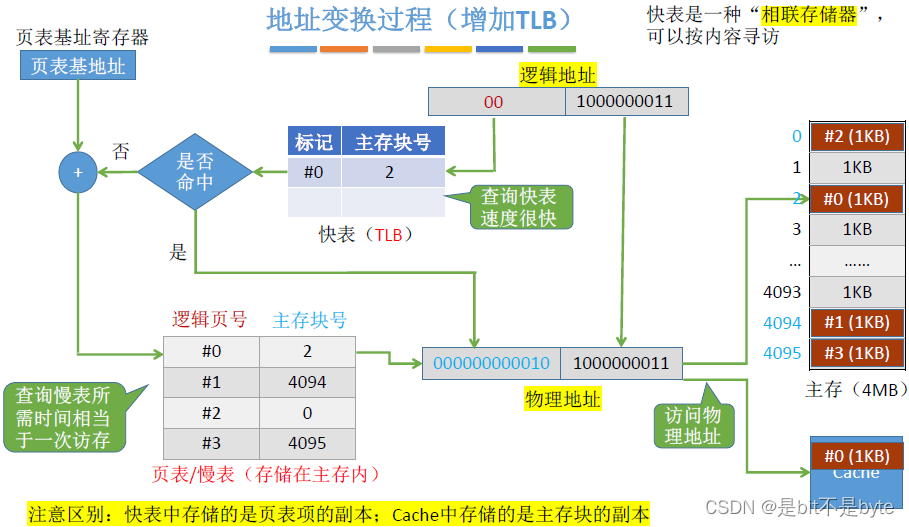

| 访问一个逻辑地址的整个过程 |

|

| 第九节:虚拟存储器 |

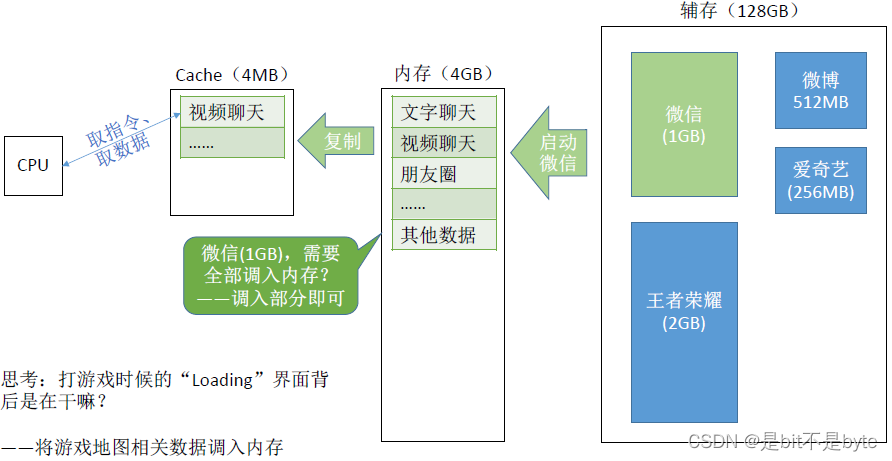

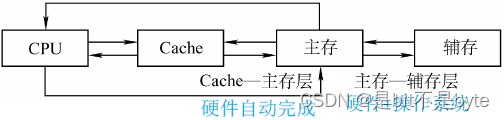

| 虚拟存储器 | 虚拟存储器是辅存→内存。和内存→Cache原理基本相同,都是根据局部性原理

| ||||||||||

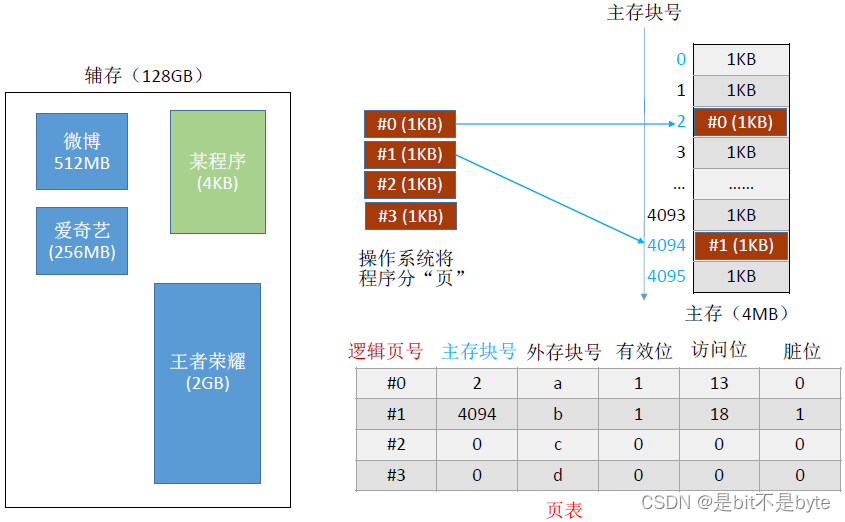

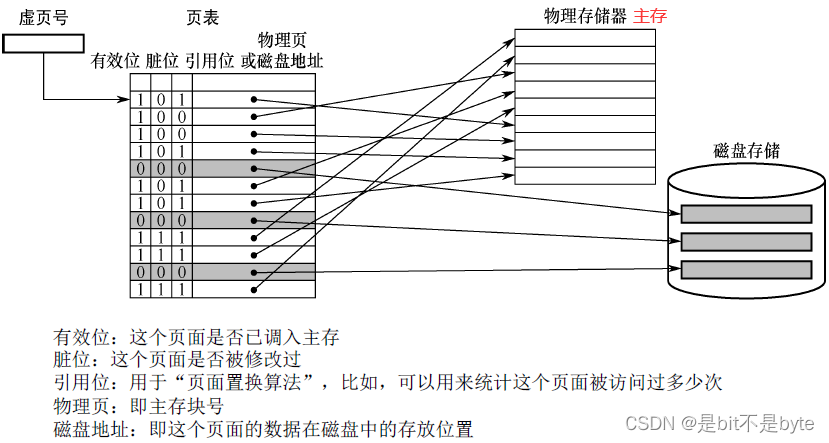

| 页式虚拟存储器 |

| ||||||||||

| 存储器的层次化结构 |

| ||||||||||

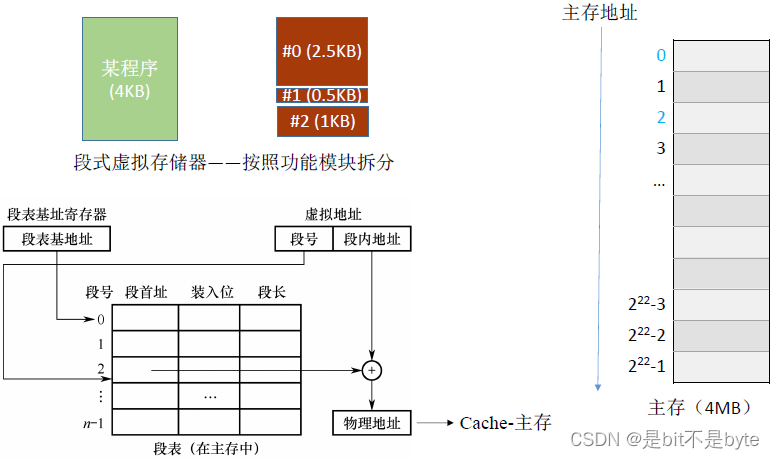

| 段式虚拟存储器 |

| ||||||||||

| 段页式虚拟存储器 |

|

本文详细介绍了计算机组成原理中存储系统的关键概念,包括内存层次结构、RAM、ROM、高速缓存(Cache)的工作原理及其优化技术,适合考研及学习开发语言的读者参考。

本文详细介绍了计算机组成原理中存储系统的关键概念,包括内存层次结构、RAM、ROM、高速缓存(Cache)的工作原理及其优化技术,适合考研及学习开发语言的读者参考。

113

113

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?