1、MMU基本功能

MMU全称Memory Management Unit,负责虚拟地址到物理地址的映射,并且提供硬件机制的内存访问权限检查。

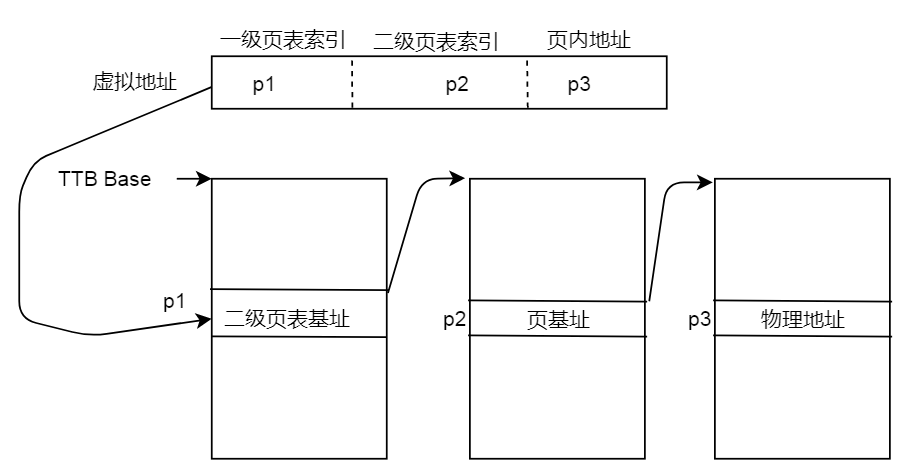

下图只是简化过的MMU寻址的通用转换过程,是使用二级页表的转换过程,具体在转换过程中会更加复杂,在转换过程中内存通过CP15寄存器C3(域访问控制)、描述符的域(domain)、CP15寄存器的C1的R/S/A位、描述符的AP位等联合作用决定是否可读写。

2、TTB与TLB

2.1、TTB

TTB是一个地址, 是一级页表的基地址,这个过程称为Translation Table Walk,Walk这个词用得非常形象。从TTB走到一级页表,又走到二级页表,又走到物理页面,一次寻址其实是三次访问物理内存。注意这个“走”的过程完全是硬件做的,每次CPU寻址时MMU就自动完成以上四步,不需要编写指令指示MMU去做,前提是操作系统要维护页表项的正确性,每次分配内存时填写相应的页表项,每次释放内存时清除相应的页表项,在必要的时候分配或释放整个页表。

下图就是描述Translation Table Walk的这一过程

TTB存储于CP15的TTB寄存器当中,以供MMU使用。

2.2、TLB

TLB全称translation lookaside buffer,用于快速的寻找物理地址, 使用页表进行虚拟地址转换时,需要访问多次内存,然后才能够找到真正的物理地址,这就造成了性能的下降,故采用了TLB进行页表的缓存。

原理就是CPU在访问虚拟地址时,首先会到TLB中进行查找,看有没有对应的表项,如果有,则直接通过TLB获取物理地址。如果没有则直接通过页表进行一步一步的查找,查找到之后,再将物理地址存于TLB。

以上信息充分说明TLB的信息依赖于页表信息,当MMU的TTB发生变化之后,就必须要将TLB失效,否则CPU在读取虚拟地址时,会调用到TLB当中的物理地址,然而TLB指向的地址并不是新的页表中的地址,就会产生异常。

/* Invalidate TLB */

static void v7_inval_tlb(void)

{

/* Invalidate entire unified TLB */

asm volatile ("mcr p15, 0, %0, c8, c7, 0" : : "r" (0));

/* Invalidate entire data TLB */

asm volatile ("mcr p15, 0, %0, c8, c6, 0" : : "r" (0));

/* Invalidate entire instruction TLB */

asm volatile ("mcr p15, 0, %0, c8, c5, 0" : : "r" (0));

/* Full system DSB - make sure that the invalidation is complete */

CP15DSB;

/* Full system ISB - make sure the instruction stream sees it */

CP15ISB;

}

以上代码就是uboot在使能MMU之前所做的关于TLB失效的操作,目的就是为了保证在MMU使能之前TLB失效,使新的TLB与TTB上的页表相对应。

3、Cache

Cache分为ICaches和DCaches,

ICache一般是在MMU开启之后被使用的,MMU开启之后页表中是由关于该指令是否可以放到cache之中的标志位的,如果不开启MMU则无法标志,则全部认为允许Cache。

DCache必须在MMU开启之后使用,因为只有在开启MMU之后,才能使用页表中的描述符来定义一块内存如何使用Dcaches和Write buffer。

1261

1261

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?