PoE/PoE+模块-PD模块PCB布局布线设计指南

很多网友对于POE模块的PCB设计还是存在很多误区,今天我们来和大家一起学习关于这一块的内容。

什么是POE模块?

一个完整的POE系统包括供电端设备(PSE,PowerSourcingEquipment)和受电端设备(PD,PowerDevice)两部分。所以POE模块主要由POE供电端及POE受电端构成。POE供电模块即PSE供电端设备在以太网RJ45端口输出很小的电压,直到其检测到线缆终端的连接为一个支持IEEE802.3af标准的受电端设备,根据受电设备输出相应的电压。当多块POE供电模块集成到一个供电模组箱内,就构成POE供电箱,POE交换机(集成了多个PSE供电端设备)也具备POE供电箱的功能。

PCB设计指南

A.范围

本文档可应用于所有Befact PoE PD模块。目前的Befact PoE PD模块型号是TPD模块(TPD-12,TPD-50,TPD-33),SPD模块(SPD-12,SPD-50),THPD模块(THPD-12,THPD-50,THPD-33) )。

B.走线宽度计算和走线/电源平面

B1.“Power Trace”的PCB通用设计规范:

-

走线应尽可能短。

-

走线宽度应满足电流额定值。

-

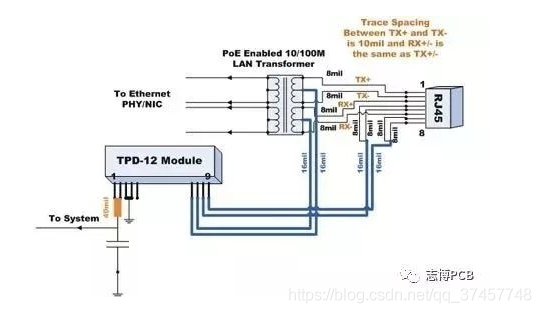

减少更换电源线图层的可能性。这意味着使用相同的层来实现电源跟踪布局。例如,如果PCB是4层,则层1和层4是信号走线层,层2用于电源层,层3是接地平面。PoE电源来自RJ45,通过TX + / TX-和RX + / RX-(模式A)以10 / 100M以太网连接传送到PD模块的输入。TX + / TX-对应在同一层(第1层/第4层)中实现。可以在RX + / RX-上应用相同的规则。

-

“电源接地”应采用一些“通孔”来连接“接地平面层”。基本上,这些“接地平面层”应作为阻抗计算的信号参考平面。

-

应采用3W规则以避免信号干扰。不同共模信号之间的间距应保持适当的间隙,约为信号走线宽度的3倍。例如,如果走线宽度为8mil,则最小间隙应为24mil(3 x 8mil)。

B2.走线宽度计算:

通常,对于直流电流1A,需要~40mil的走线宽度(@铜走线的厚度为1.4mil= 10z)。例如,TPD-12模块的最大输入电流为420mA,走线宽度为16.8mil(40 mil x 0.42 = 16.8mil)。直流电源由一个差分对(两条迹线)提供。因此,每条走线的最小走线宽度为8mil。TPD-12的最大输出电流为1A,走线宽度需要40 mil。

应用相同的规则,THPD-50每个输入走线需要12mil的走线宽度,输出电流需要150 mil的走线宽度(40mil x 3.8 = 152 mil)。

B-3.使用走线连接:

图1.

B-4.使用电源平面连接(用于高电流应用):

图2.

C.阻抗计算和PCB叠层

1.阻抗计算:

以太网信号的差分阻抗为每对100欧姆(两根线)。如图1所示,TX +/-和RX +/-的走线需要8mil宽度的走线用于PoE功率输送。应采用两种阻抗计算规则,即微带和差分微带。

请按以下步骤处理步骤:

1.FR4的介电常数(Er)信息应为已知信息。

2.应用Micro-strip模型计算共模阻抗。

3.使用步骤2的结果并应用差分微带来计算差模阻抗。

实际例一--TPD-12(图1的案例研究):

假设PCB的厚度为1.6mm / 4层(63mil,1mil= 1/1000英寸),介电常数(Er)为4.0。

PCB叠层

实际例2-THPD-50(图2的案例研究):

假设PCB的厚度为1.6mm / 4层(63mil,1mil= 1/1000英寸),介电常数(Er)为4.0。

PCB叠层

2.完成布局示例:

a.图一案例研究

b.案例研究图2

9392

9392

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?