ShiDianNao: Shifting Vision Processing Closer to the Sensor

一、介绍

本文提出了一个边缘端的视觉处理器Shidiannao,与传统的视觉处理装置不同。本文将处理单元Processor放在Sensor感知器附近,从而省略了DRAM的访存过程,能够满足图片信息实时处理的需求。我们先对比一下传统的和本文的视觉处理过程。

传统视觉处理过程:Sensor采集->DRAM->Processor(SRAM)

本文视觉处理过程:Sensor采集->Processor(SRAM)

原有的DRAM可以理解为一个缓冲区,解决了采集和处理速度不匹配的问题(此时采集速度>处理速度)。但只要处理速度足够快,就能使得采集到的图片可以被及时处理,就可以实现流式处理过程,放弃缓冲区这一设置。注意,放弃DRAM还有一个限制,就是CNN网络需要足够小,可以全部放入到SRAM中。综上,现在最关键的问题是如何设计一个处理速度足够快的视觉处理器。

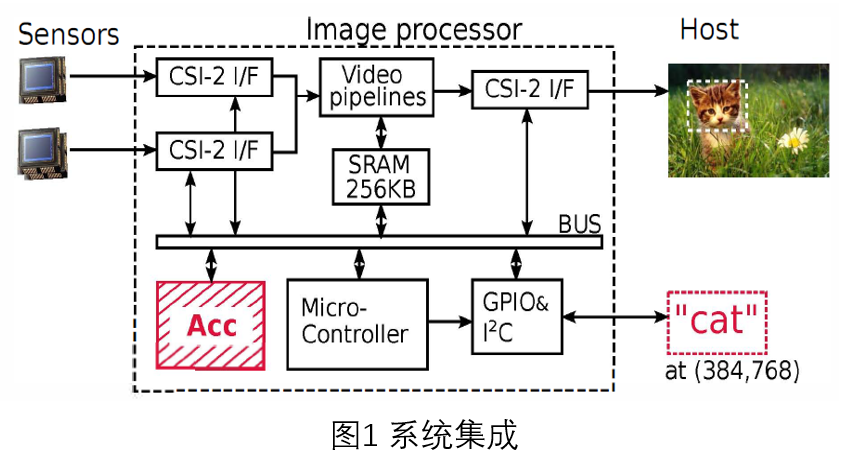

二、系统集成

系统集成如图1所示,其中CSIs(Camera Serial Interjaces)是接口;Video pipelines是处理器,用于实现基本图像处理功能和人脸识别等高级功能;Micro-Controller是控制器。本文主要讨论的是如何在Video pipelines中实现快速执行图像处理的CNN网络。

三、映射方法

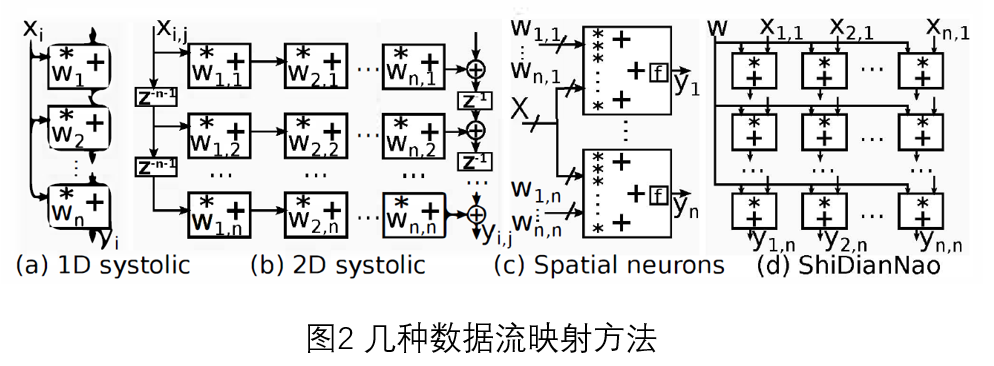

图2是几种常见的数据流映射方法,我们主要看两种。(b)是二维的脉动阵列,其特点是权值固定(WS)在PE中,输入数据统一从左侧进入,输出统一从下面出去,数据传输模式简单。(d)是本文采取的架构,属于输出固定(OS)架构:一个PE计算一个输出神经元,直到该神经元计算完成,PE才会计算下一个输出神经元。权值数据是以广播形式发送给每个PE单元,输入数据一部分来自于存储单元,一部分来自于临近PE单元,后面会详细分析该架构。

四、处理器架构

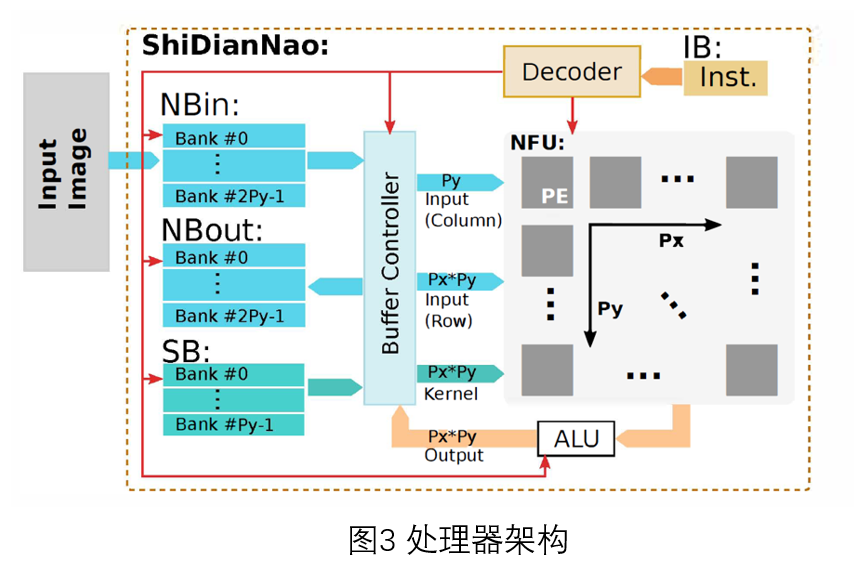

1.整体架构

如图3所示,整体架构包含存储、计算和控制三部分。存储单元和Dianano一样,将NBin、NBout和SB分别实现。计算单元是Px*Py大小的二维PE阵列。控制部分负责整体的协调。

2.计算架构

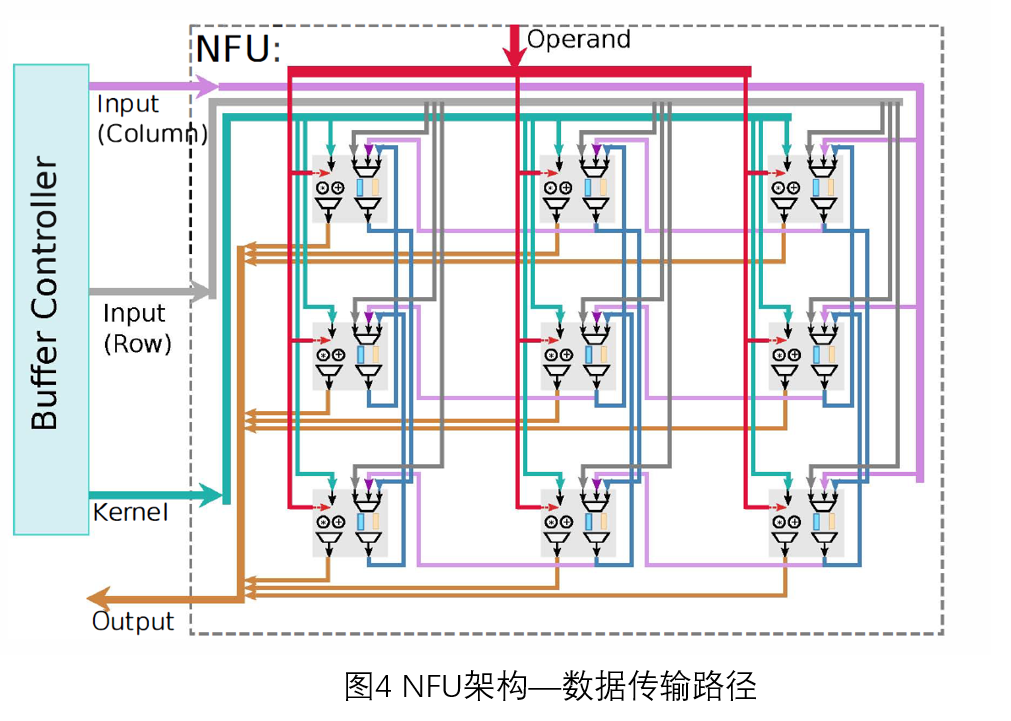

NFU计算单元是Px*Py的二维PE阵列,如图4所示。我们主要说一下数据传输路径。

红色线:控制信号。

粉色线:每次从输入单元传输Py个数据到最右列的PE单元中,最右列的PE继续将数据传输给其左邻居,按此模式依次传输。

灰色线:每次传输Px*Py个输入数据到PE单元中,也就是向每个PE单元传输一个输入数据。

蓝色线:负责kernel数据数据的传输,以广播形式发送到每个PE单元中。(PS:以卷积为例,kernel在每个feature map是共享的,因此其传播方式为广播。)

棕色线:传输输出数据。

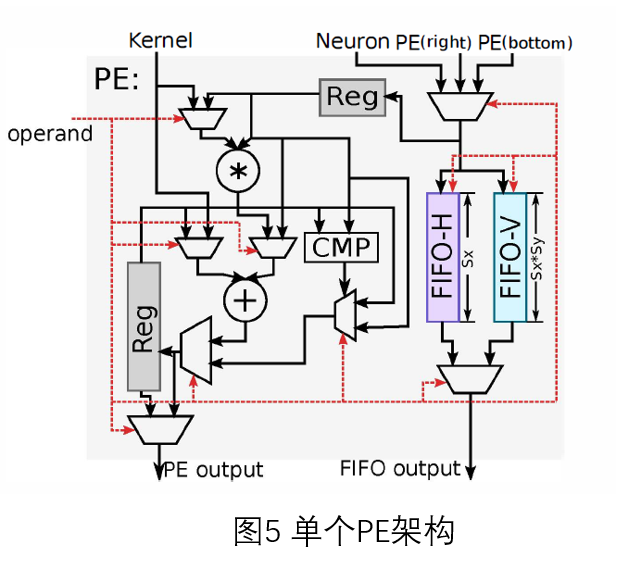

单个PE单元架构,如图5所示:FIFO-H用于存储水平方向数据,FIFO-V用于存储竖直方向数据。

支持的运算类型:mul,add,cmp,avg;

输入:kernel,input从左向右依次来自于缓存单元、右邻居、下邻居;

输出:output计算结果,传输给邻居PE的值。

3.存储架构

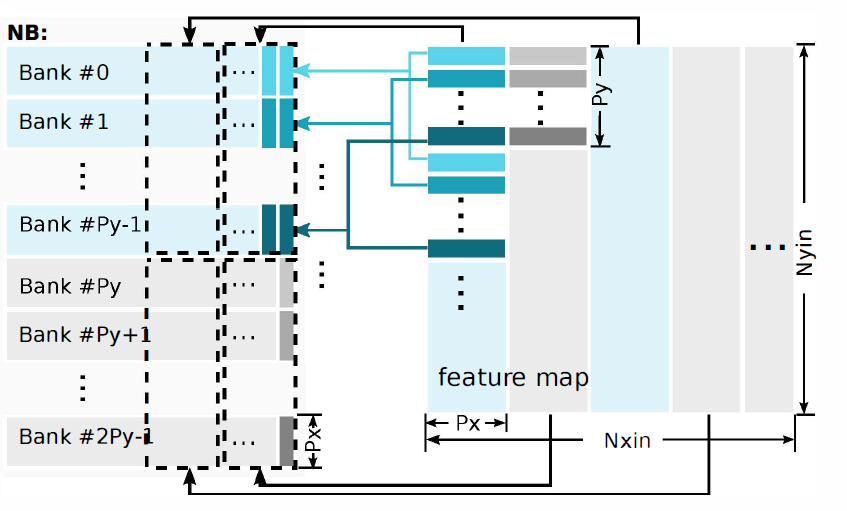

NBin、NBout:共有2 * Py个bank,每个宽为Px * 2。下面图是NB缓存区上数据的排列形式。其中Nxin和Nyin是待计算数据总规模,总数据的蓝色第一列Px * Py大小的数据块依次映射到NB缓存区0~Py-1的bank上,灰色第二列的数据块映射到NB缓存区Py-P2y-1的数据块上。

SB:Py个bank。

ALU单元:实现一些额外操作:激活函数,除法(用于平均池化)。

存储单元读取模式:

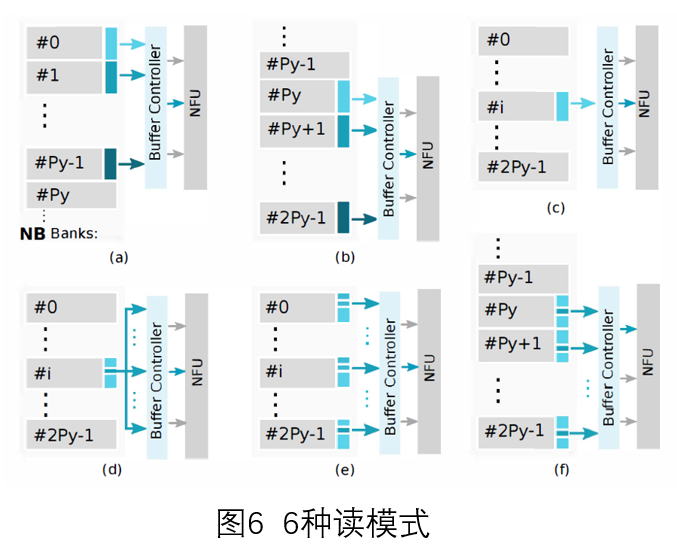

6种读模式

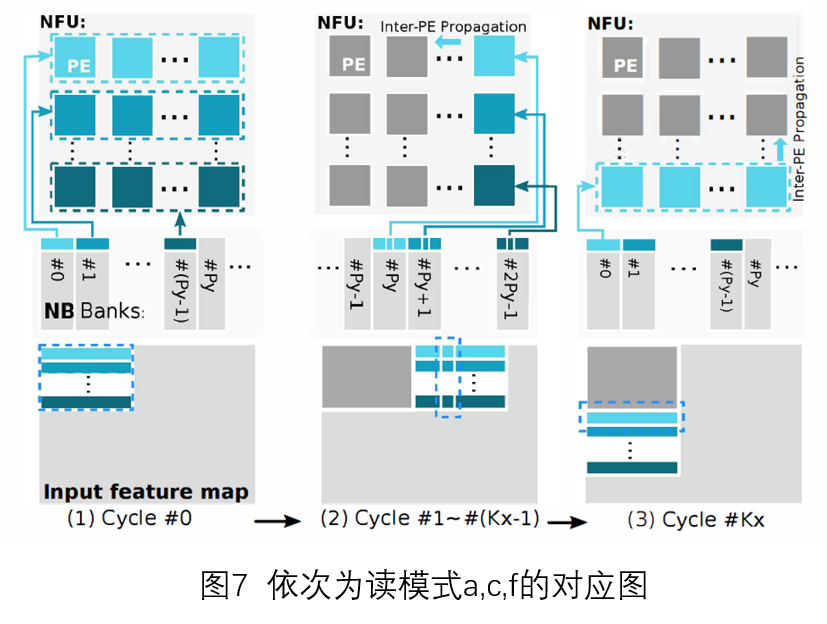

a 读取多个bank(0-Py-1)——(读取Px*Py个数据 对应图7-(1) )

b 读取多个bank(Py-2Py-1)——(同上,下标不同而已)

c 读取一个bank——(读取Px个数据 对应图7-(2) )

d 读取单个神经元

e 按给定步长读取单神经元

f 按照bank读取单神经元(0-Py-1或Py~2Py-1)—(读取Py个数据 对应图7-(3) )

1种写模式:计算出某输出神经元,先写入到临时寄存器中。等到Px * Py个PE单元都计算完成后,一起写入NBout(Py行,每行宽为Px*2)。

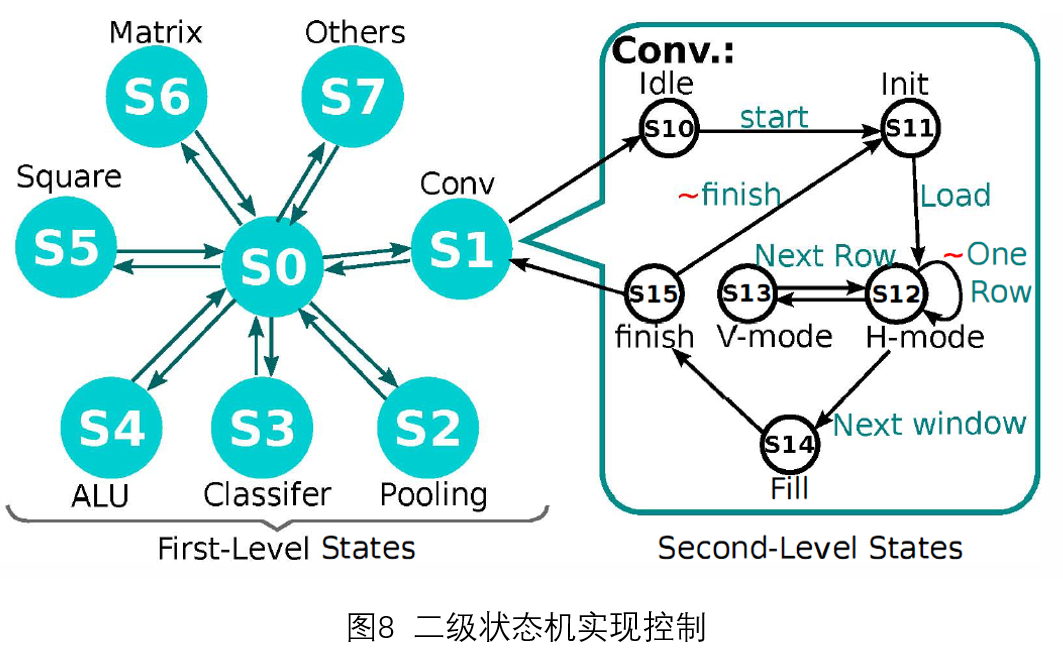

3.控制实现

控制部分是采用二级状态机(FSM)实现的。第一级分类是各种运算类型;第二级分类是运算的具体操作。以卷积层为例,计算一个输出神经元值的过程为:Load加载数据—水平方向传播一行数据并计算(H-mode)—竖直方向传播切换到下一行(V-mode)—继续水平方向传播计算(H-mode)……该输出神经元计算完成(Next Window)—finish。采用状态机形式,可以减少指令条数,节省内存。

五、网络层映射实例

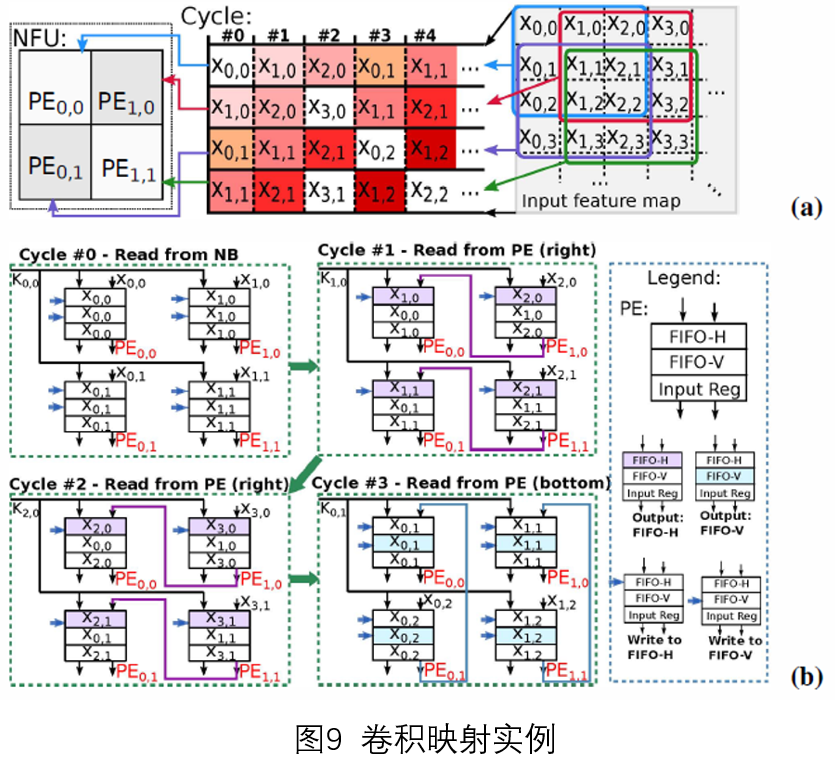

卷积层:这里的数据复用本质上是因为相邻卷积窗口中的输入数据会有很多覆盖。

参数

NFU单元:Px * Py=2 * 2

Kernel size:3 * 3

step size:1*1

具体实现:每个周期内Kernel数据都是以广播形式传送到每个PE单元中的。

Cycle0:读模式a,读取Px * Py个数据

Cycle1:读模式f,读取Py个数据

Cycle2:读模式f,读取Py个数据,到此第一行处理完成

Cycle3:读模式c,读取Px个数据,开启第二行执行

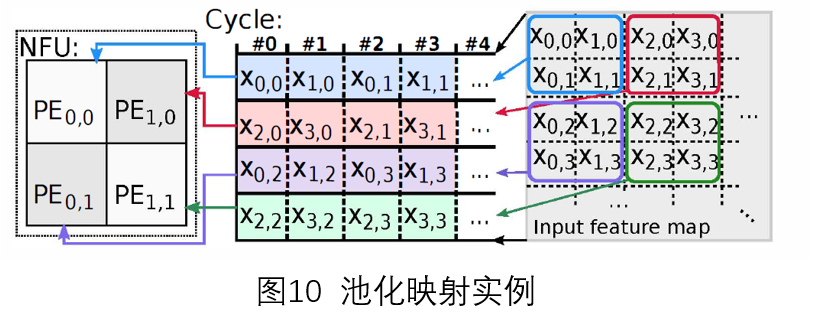

池化层:一般情况下,池化层数据没有覆盖,不需要传播,读模式e读取数据。如果数据存在覆盖情况,按卷积方式计算。

分类层:每周期读取Px*Py的权值到PE中,再读取单个input到每个PE中。计算完一个输出神经元才切换。

正则化层:LRN和LCN层被分解为前面基本网络层的组合实现。

六、实验结果

运算单元:8*8=64个PE

| 对比 | Shidiannao | Diannao |

|---|---|---|

| 工艺 | 65nm | 65nm |

| 频率 | 1GHz | 0.98 |

| 面积 | 4.86mm2 | 3.02mm2 |

| 性能 | 194Gop/s | 482Gop/s |

| 能耗 | 320.10mW | 485mW |

| 存储单元 | 288KB | 44KB |

| 位数 | 16bit | 16bit |

分析:相比Diannao处理器,能耗少了。但是性能下降了,存储单元也多了很多。

Finished.

PS:感觉学的是个思路,如果想要实现一个,细节会很多。

923

923

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?