PS端控制PL端(GPIO IP核)

Vivado端:不需要锁管脚。Board栏的所有外设,Xilinx自家的板子都有的,从这一栏选的外设引脚约束已经自动添加好了。

1.Create block design

2.添加Zynq IP核,Zynq的配置可参考该文章

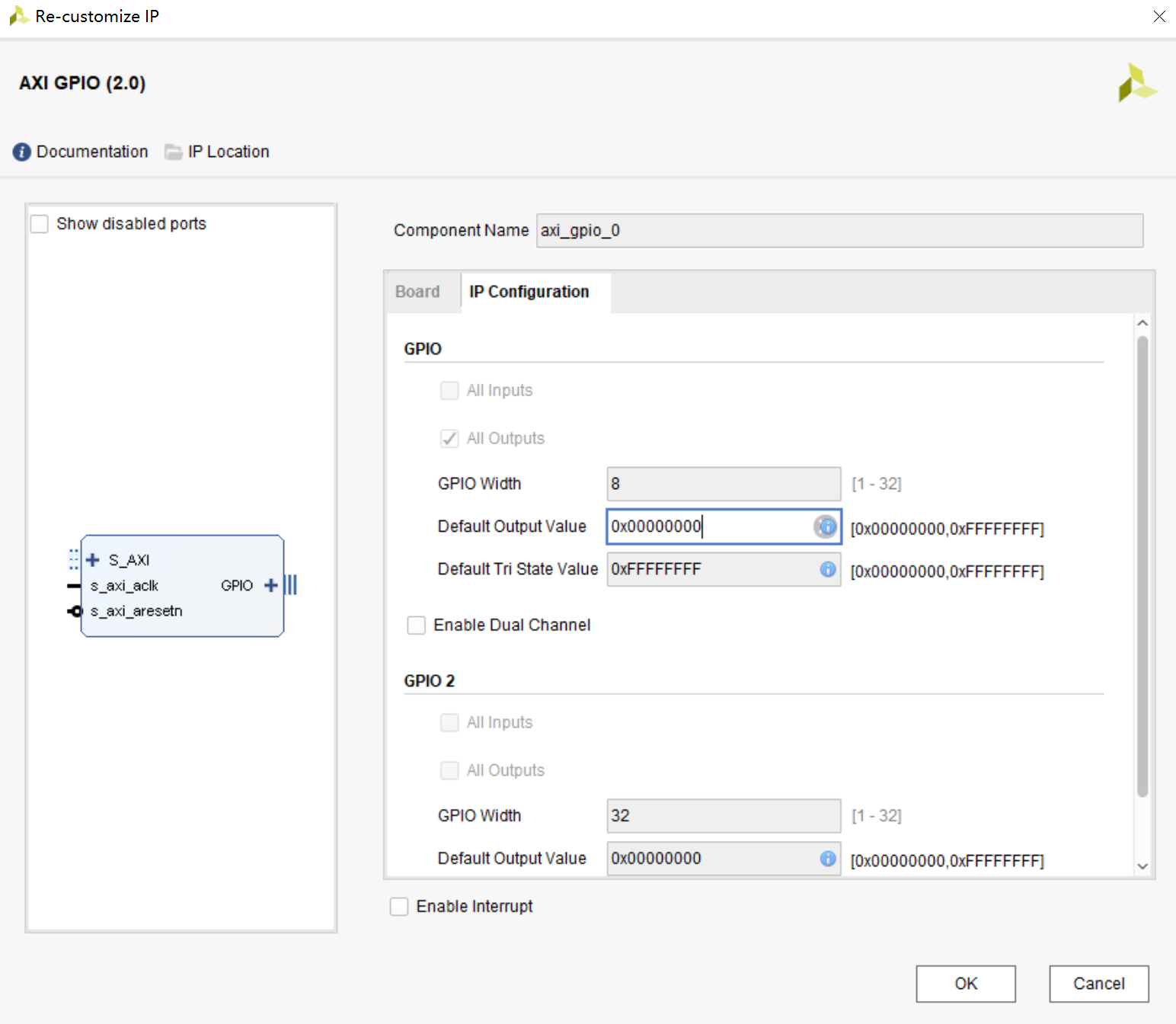

3. 添加自带的GPIO IP核。配置如下:第一组width设置为8(对应8个灯)

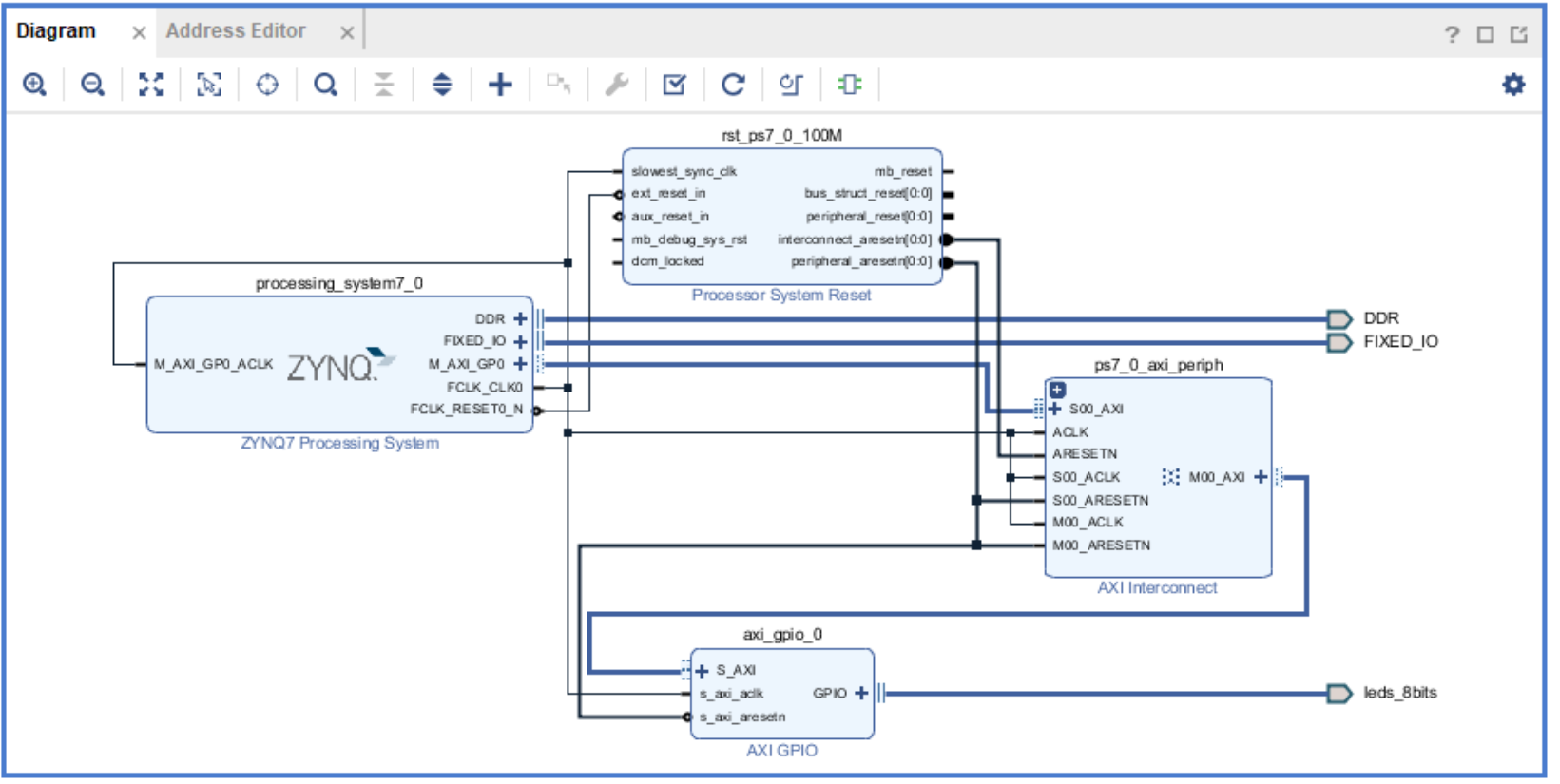

4.点击自动连线,GPIO设置为led_8bit模式

5.点击自动连接外设

最终Vivado中的bd图如下所示:

验证,生成bit流,导出为硬件平台即可。

SDK端:GPIO IP的封装函数在bsp中的libsrc/文件夹下。

直接将主函数代码替换为如下代码即可。

/*

* ledflow

*/

#include"xparameters.h"

#include"xgpio.h"

#include"xil_printf.h"

#include"xil_cache.h"

#define GPIO_BITWIDTH 8 // 8个灯

#define GPIO_DEVICE_ID XPAR_AXI_GPIO_0_DEVICE_ID // 灯设备

#define LED_DELAY 100000000 // 延迟时间

#define LED_CHANNEL 1 // GPIO第一组,只有这一组灯

#define printf xil_printf

XGpio Gpio;

XGpio GpioOutput;

int GpioMarquee(u16 DeviceId,u32 GpioWidth)

{

volatile int Delay;

u32 LedBit;

u32 LedLoop;

int Status;

// GPIO Init.

Status=XGpio_Initialize(&GpioOutput,DeviceId);

if(Status!=XST_SUCCESS)

{

return XST_FAILURE;

}

// 配置GPIO:LED_CHANNEL-第一组还是第二组 0x0:输入 or输出

XGpio_SetDataDirection(&GpioOutput,LED_CHANNEL,0x0);

// 0x0,写入寄存器的值

XGpio_DiscreteWrite(&GpioOutput,LED_CHANNEL,0x0);

for(LedBit=0x0;LedBit<GpioWidth;LedBit++)

{

XGpio_DiscreteWrite(&GpioOutput,LED_CHANNEL,1<<LedBit); // 写入

for(Delay=0;Delay<LED_DELAY;Delay++); // 等待

XGpio_DiscreteClear(&GpioOutput,LED_CHANNEL,1<<LedBit); // 清除该位为0

for(Delay=0;Delay<LED_DELAY;Delay++); // 等待

}

return XST_SUCCESS;

};

int main(void)

{

while(1)

{

u32 status;

// 8个灯依次亮

status=GpioMarquee(GPIO_DEVICE_ID,GPIO_BITWIDTH);

if(status==0)

printf("SUCCESS!.\r\n");

else

printf("FAILED.\r\n");

}

return XST_SUCCESS;

}

下载bitstream,运行后即可观察到流水灯情况。

2508

2508

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?