本笔记使用的Vitis HLS版本为2022.2,在windows11下运行,仿真part为xcku15p_CIV-ffva1156-2LV-e,主要根据教程:跟Xilinx SAE 学HLS系列视频讲座-高亚军进行学习

学习笔记:《FPGA学习笔记》索引

FPGA学习笔记#1 HLS简介及相关概念

FPGA学习笔记#2 基本组件——CLB、SLICE、LUT、MUX、进位链、DRAM、存储单元、BRAM

FPGA学习笔记#3 Vitis HLS编程规范、数据类型、基本运算

FPGA学习笔记#4 Vitis HLS 入门的第一个工程

FPGA学习笔记#5 Vitis HLS For循环的优化(1)

FPGA学习笔记#6 Vitis HLS For循环的优化(2)

FPGA学习笔记#7 Vitis HLS 数组优化和函数优化

FPGA学习笔记#8 Vitis HLS优化总结和案例程序的优化

目录

1.HLS优化总结

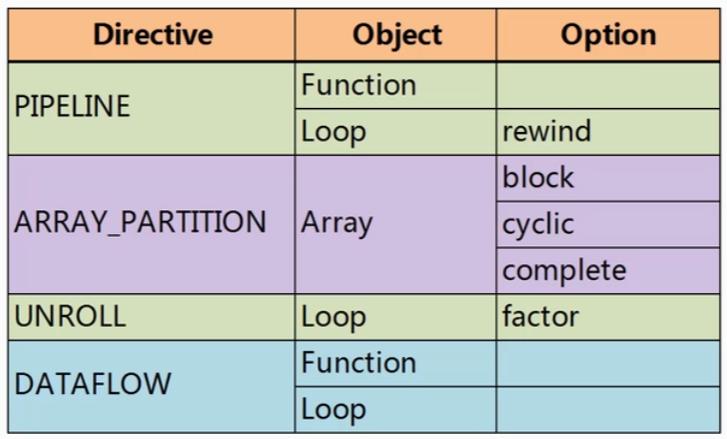

对于函数,可以使用PIPELINE或DATAFLOW。

对于循环,可以使用PIPELINE(可选rewind)、UNROLL(可选factor)或DATAFLOW。

对于数组,可以使用ARRAY_PARTITION,有block、cyclic、complete三种优化方式。

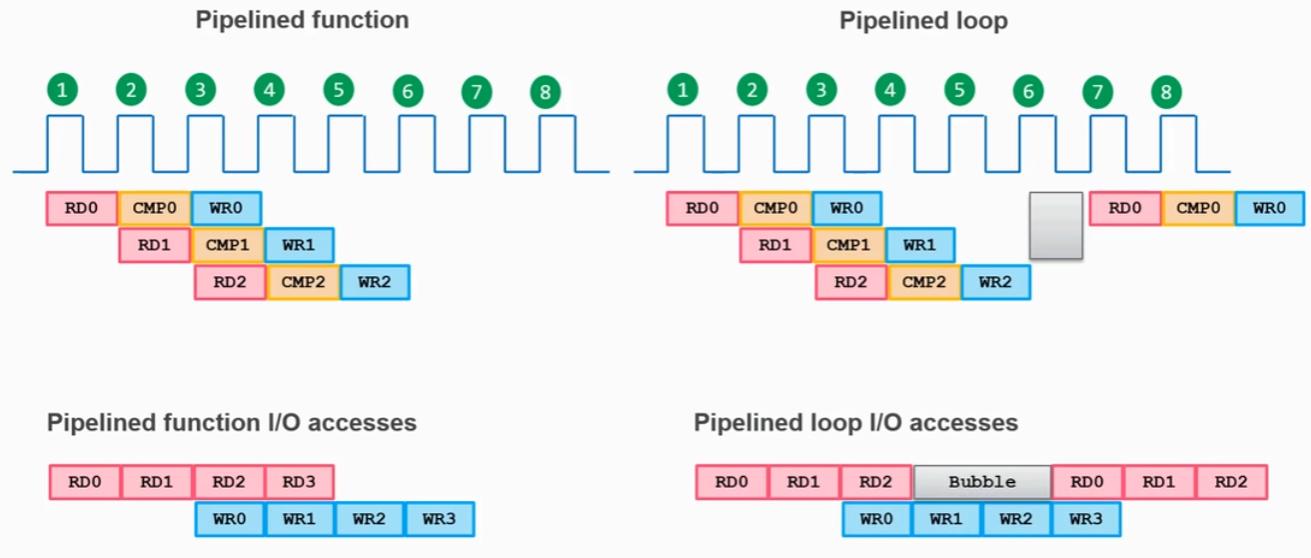

PIPELINE作用于函数和循环的情况如下,作用于循环时,两次循环之间会存在空档,被称为bubble,rewind可以解决这个问题。

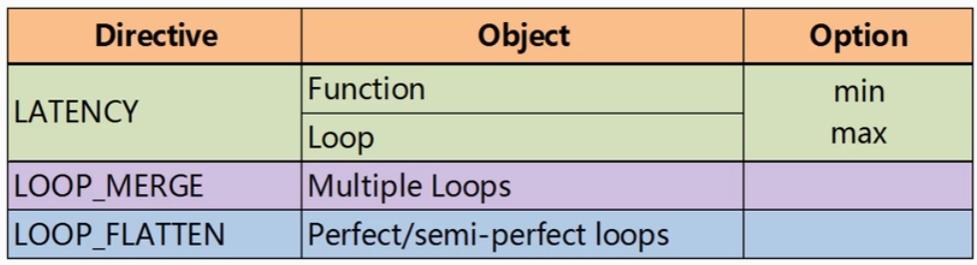

对于latency,有专门的LATENCY约束用于函数和循环,可以指定min和max。

LOOP_MERGE用于合并多个循环

LOOP_FLATTEN用于perfect/semi-perfect循环

在区域中:

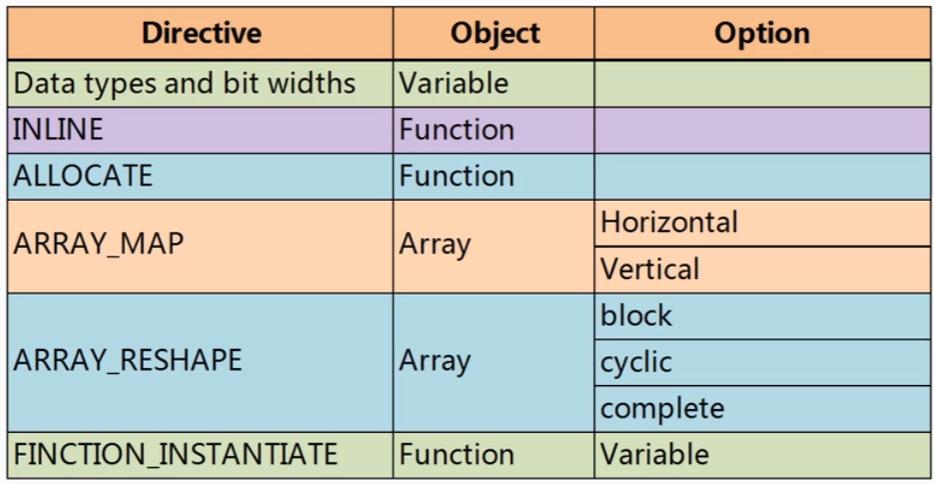

数据类型和位宽也是影响硬件效率和资源使用的原因

INLINE用于函数

ALLOCATION用于函数的实例化

ARRAY_MAP和ARRAY_RESHAPE用于数组

FUNCTION_INSTANTIATE用于函数

2.优化案例

2.1.案例程序

案例程序如下,请根据第四篇笔记进行项目的构建和仿真、综合、联合仿真。

Top.h:

#include <ap_int.h>

#include <ap_fixed.h>

#define WA 17

#define FA 14

#define WS 16

#define FS 14

typedef ap_fixed<WA,WA-FA> di_t;

typedef ap_fixed<WS,WS-FS> do_t;

typedef ap_uint<2> flag_t;

const do_t Kn = 0.607252935;

const di_t PI = 3.1415926;

void cir_cordic (di_t full_alpha, do_t &out_sin, do_t &out_cos);

Top.cpp:

#include "top.h"

void pre_cir_cordic (di_t full_alpha, di_t &alpha, flag_t &flag)

{

if (full_alpha > PI/2)

{

alpha = PI - full_alpha;

flag = 2;

}

else if (full_alpha < -PI/2)

{

alpha = -PI - full_alpha;

flag = 3;

}

else

{

alpha = full_alpha;

flag = 0;

}

}

void cir_cordic_calculate (di_t alpha, flag_t flag, do_t &mysin, do_t &mycos, flag_t &flag_delay)

{

const int N = 16;

do_t xi[N];

do_t yi

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?