看前提醒:作者入门尚浅,本文基本是找到的教程的简略版笔记,本文主要为学习作者:Jasper兰的FPGA教程系列,并结合部分学习中查找的其他资料整理而成。

学习笔记:《FPGA学习笔记》索引

FPGA学习笔记#1 HLS简介及相关概念

FPGA学习笔记#2 基本组件——CLB、SLICE、LUT、MUX、进位链、DRAM、存储单元、BRAM

FPGA学习笔记#3 Vitis HLS编程规范、数据类型、基本运算

FPGA学习笔记#4 Vitis HLS 入门的第一个工程

FPGA学习笔记#5 Vitis HLS For循环的优化(1)

FPGA学习笔记#6 Vitis HLS For循环的优化(2)

FPGA学习笔记#7 Vitis HLS 数组优化和函数优化

FPGA学习笔记#8 Vitis HLS优化总结和案例程序的优化

目录

1.可配置逻辑块

可配置逻辑块(Configurable Logic Block,CLB) 是FPGA芯片的底层元件之一,如果将FPGA比作人体,那么CLB就是组成人体的细胞。

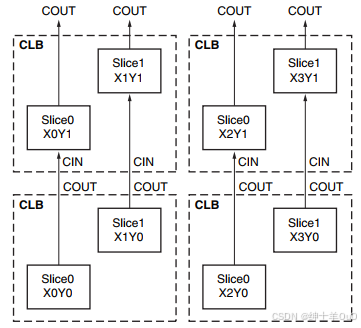

CLB由SLICE组成,不同架构的SLICE种类不一样,Xilinx7系中就有两种SLICE:SLICEL、SLICEM,SLICEM比SLICEL多了写存储数据功能。

2.SLICE组成简介

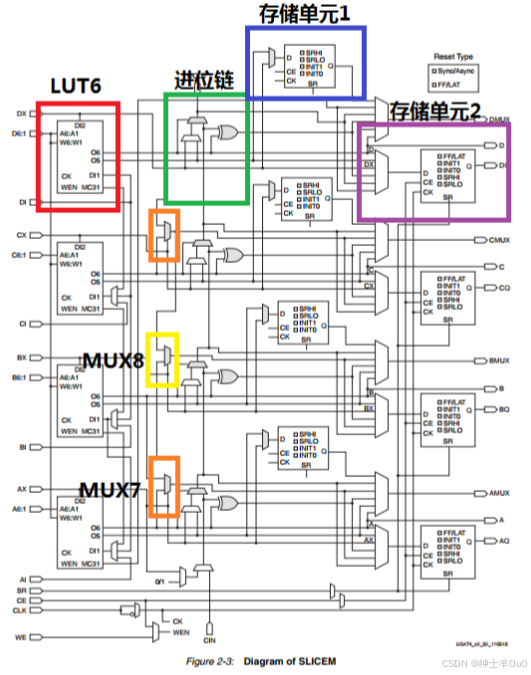

FPGA每个SLICE基本都由LUT、MUX、进位链、寄存器组成:

- LUT(look up table):查找表

- MUX(Multiplexer):多路选择器

- 进位链:用于实现全加器

- 寄存器:同步数据,常用于打拍

下图为SLICEM的组成结构,SLICEL与SLICEM的差别仅在于SLICEM的4个LUT6具有存储功能,而SLICEL没有。

对于整体结构在本小节仅做了解,在本文做完各组件介绍后会对整体结构进一步分析。

3.LUT

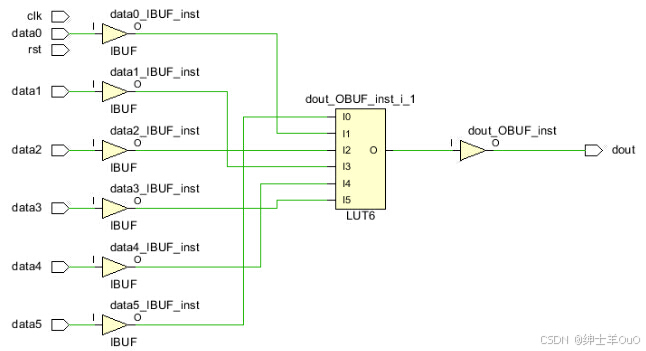

查找表(Look Up Table, LUT),FPGA以LUT代替门电路,任意一个 6位输入1位输出(6IN-1OUT) 的门电路,都可以用LUT6来表示。LUT6本质是64*1的ROM(Read Only Memory),深度为64,位宽为1,将6位输入当做6位地址线,则输出就是当前地址存储位。

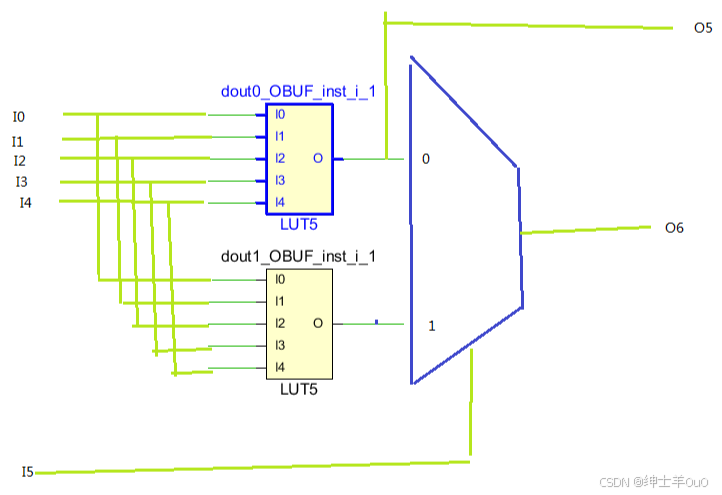

LUT6本质由2个LUT5(5IN-1OUT)组成,首先两个LUT5分别对I[4:0]指定真值表,此时对于l[4:0]会分别有2位输出,这2位输出再经过由I5控制的选择器(MUX)输出为O6,即可实现LUT6。此时O5会输出上方LUT5的结果,但一般只在LUT6用作5位输入2位输出时使用。

LUT6可以用作5位输入2位输出(5IN-2OUT),使用此功能时I5将强制置1,使O6的输出为下方LUT5的输出。

在实际情况中:

- 输出是1位,并且输入小于等于6位时,仅需无视高位填LUT6真值表,再写入LUT6即可

- 输入大于1位,或输入比6位多时,则用多个LUT6并行处理,这会使多个输入途径多条路径,而路径之间延迟难以一致,此时需要使用寄存器来进行同步。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1840

1840

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?