FPGA STA(静态时序分析)

今天给大侠带来FPGA STA(静态时序分析),话不多说,上货。

一、概述

1.1 概述

在快速系统中FPGA时序约束不止包含内部时钟约束,还应包含完整的IO时序约束和时序例外约束才能实现PCB板级的时序收敛。因此。FPGA时序约束中IO口时序约束也是一个重点。仅仅有约束正确才能在快速情况下保证FPGA和外部器件通信正确。

1.2 FPGA总体概念

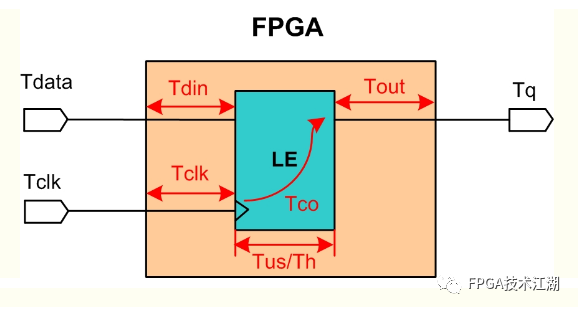

因为IO口时序约束分析是针对于电路板整个系统进行时序分析,所以FPGA需要作为一个总体分析,当中包含FPGA的建立时间、保持时间以及传输延时。传统的建立时间、保持时间以及传输延时都是针对寄存器形式的分析。针对整个系统FPGA的建立时间保持时间能够简化。下图为FPGA总体时序图:

如图上图所示,分解的FPGA内部寄存器的性能參数:

(1) Tdin为从FPGA的IO口到FPGA内部寄存器输入端的延时;

(2) Tclk为从FPGA的IO口到FPGA内部寄存器时钟端的延时;

(3) Tus/Th为FPGA内部寄存器的建立时间和保持时间&

订阅专栏 解锁全文

订阅专栏 解锁全文

6629

6629

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?