一、工程目标和实验平台

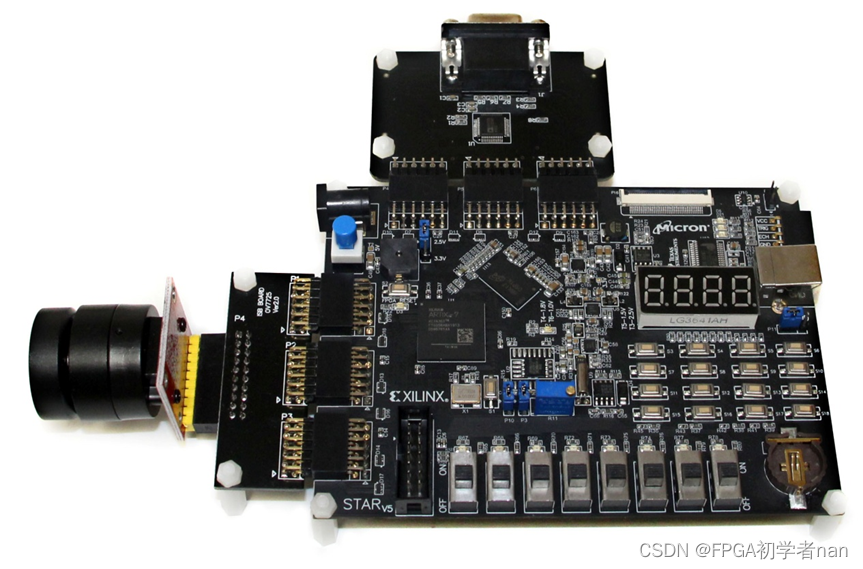

本系列视频基于Xilinx Artix-7系列的FPGA器件,对工业视觉级数字图像传感器MT9V034进行图像的采集、图像的DDR3读写缓存、图像的VGA显示驱动控制。视频中包括详细的基本原理的理论讲解、整个工程的设计架构、外部和内部之间的接口定义、每个设计细节的基本思路、外设芯片的控制原理、每一个设计模块的具体编码(代码逐行输入和讲解)和仿真验证(结合Modelsim和Matlab协同验证)、中间过程的在线调试和最终的板级调试。

二、介绍CCD与CMOS图像传感器

图像传感器介绍:

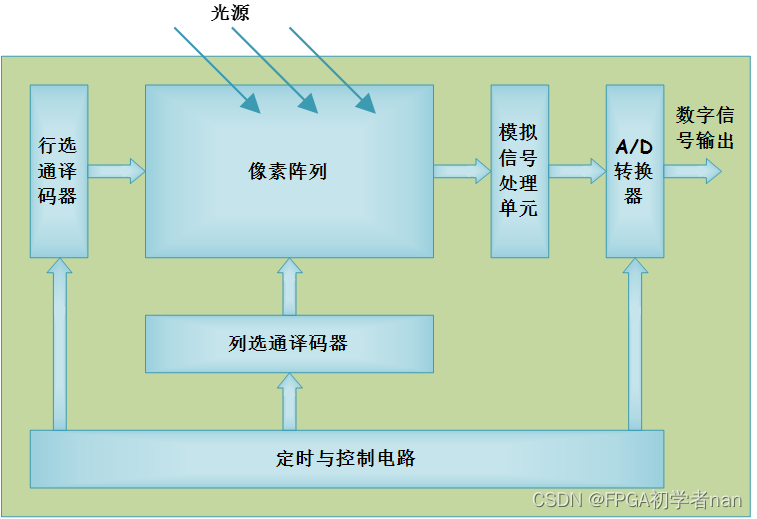

这是CMOS图像传感器的基本功能框图。外界光源照射像素阵列,发生光电效应,在像素单元内产生相应的电荷。行选通译码器在定时与控制电路的控制下,定时选通相应的行像素单元,行像素单元内的图像信号通过各自所在列的信号总线传输到对应的模拟信号处理单元以及A/D转换器,转换成数字图像信号输出。行选通译码器可以对像素阵列逐行扫描或隔行扫描。行选通译码器与列选通译码器配合使用可以实现图像的窗口提取功能。模拟信号处理单元的主要功能是对信号进行放大处理,并且提高信噪比。

三、图像传感器内部工作的基本原理

图2 CMOS图像传感器的基本功能框图

CMOS图像传感器的像素阵列是由大量相同的感光单元组成的,这些感光单元是图像传感器的关键部分。在图像传感器触发工作时,首先将所有像素阵列中的感光单元复位,清除所有电荷,然后开始感光积分到设定的曝光时间结束。接着行选通译码器和列选通译码器 开始工作,将每个感光单元的电荷逐个送出并最终转换为数字信号。

图3 CMOS图像传感器的感光阵列

三、图像传感器内部工作的基本原理

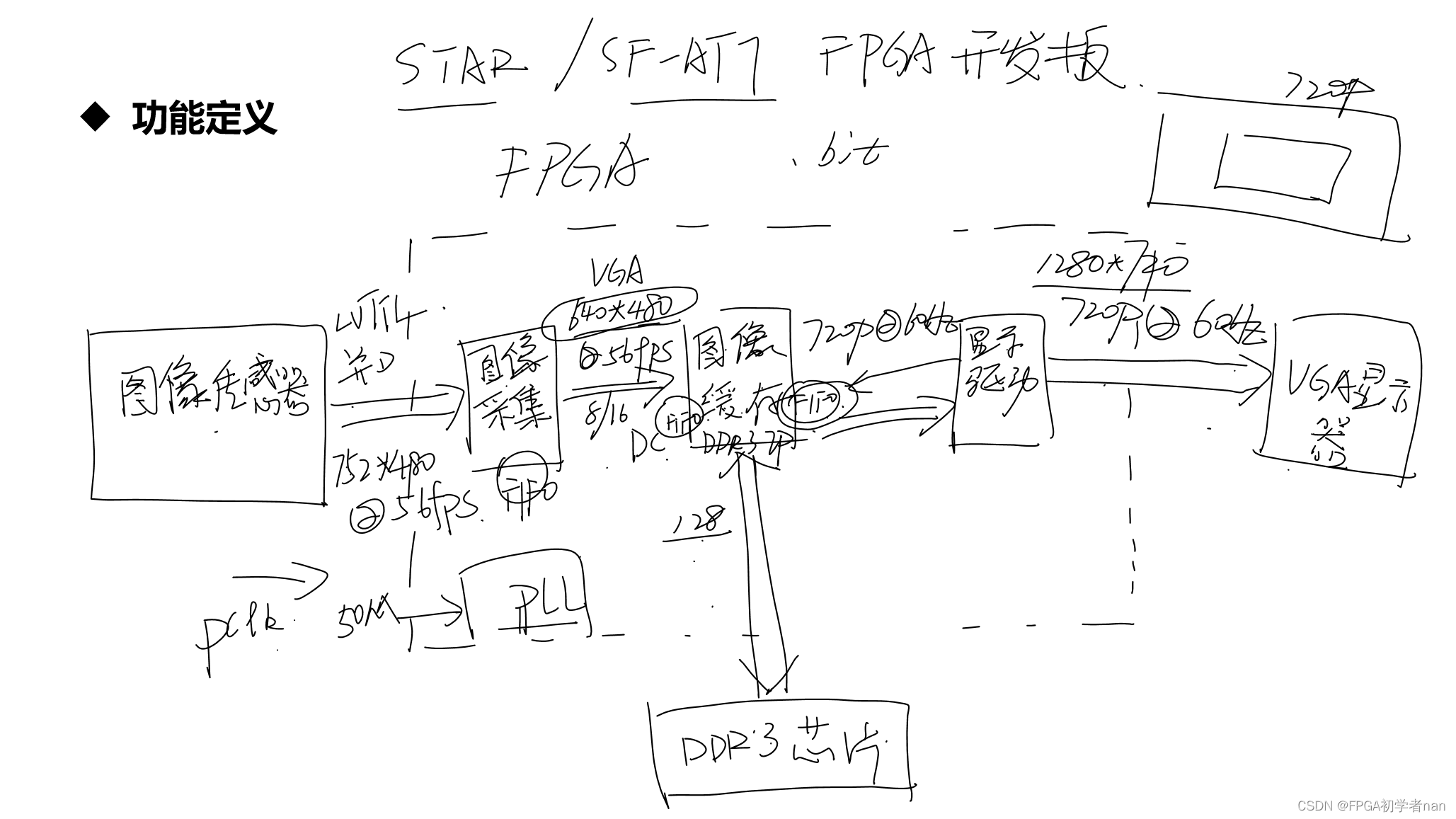

1、图像传感器 LVTTL 接口 752×480 @56fps 。FPGA端的图像采集模块要有个FIFO缓存,目的为了把单个信号整合,方便一行行输出。图像传感器的时钟是 pclk ,它与FPGA内部的时钟也不一样,FPGA的时钟频率高一些。FIFO可以进行时钟域切换。

2、FPGA

PLL是时钟控制单元,它可以让FPGA外部的晶振产生的50MHZ时钟输出好几个时钟。FIFO适合跨时钟域处理。

图像采集模块(FIFO)→

进行裁剪成标准的VGA分辨率 640×480 后再进行

图像缓存(例化DDR3控制器的IP,并且有两个 FIFO,通过FIFO让模块接口位宽匹配,且可以让时钟同步 ),与 DDR3 芯片相接。

显示驱动发送读请求到图像缓存,然后图像缓存通过读FIFO输出数据到显示驱动模块。(它也是根据VGA显示器的要求,发出1280×720 @60HZ的读数据请求到图像缓存模块)

3、

VGA显示器。根据显示器的需求,显示驱动输出 1280×720 @60HZ的图像数据到VGA显示驱动。

总结:由于每个模块之间的接口位宽以及时钟频率不一样,故需要FIFO缓存。而VGA显示器的分辨率是 1280×720 ,但是图像传感器只能采集 752×480 分辨率,解决办法就是,让图像数据在VGA显示器上居中显示。

四、图像采集显示设计的功能架构

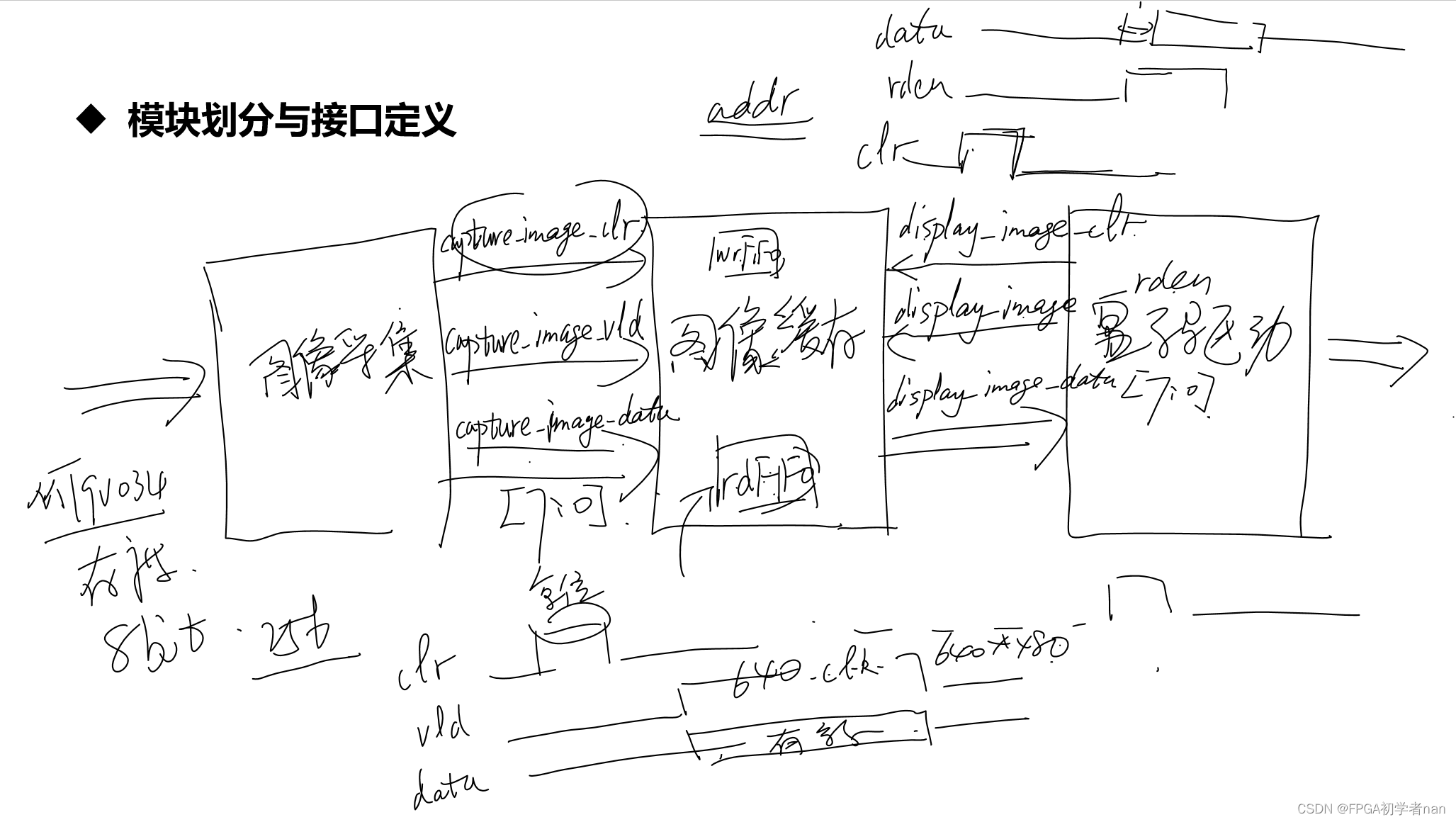

五、图像采集显示设计的接口定义

MT9V034灰度传感器 256级,所以 8bit

1、图像采集

capture_image_clr 复位清除信号,每一帧就让写数据FIFO地址清零,FIFO数据清空

capture_image_vld 数据有效信号,拉高时,数据才有效

capture_image_data [7:0] 数据总线

时序过程:

①、capture_image_clr 复位清除信号 高脉冲拉低后,

②、capture_image_vld 数据有效信号拉高,在capture_image_vld 的一个高脉冲期间,

③、capture_image_data 数据用很多个时钟传完一帧图像数据。

④、capture_image_clr 复位清除信号 高脉冲拉低后,

⑤、capture_image_vld 数据有效信号拉高,在capture_image_vld 的一个高脉冲期间,

⑥、capture_image_data 数据用很多个时钟传完一帧图像数据。

⑦、。。。。。

2、图像缓存

display_image_clr 复位清除信号,每一帧就让读数据FIFO地址清零,FIFO数据清空

dispaly_image_rden 读数据使能

display_image_data [7:0] 数据总线

①、display_image_clr 复位清除信号 高脉冲拉低后,

②、display_image_rden 读数据有效信号拉高,在display_image_rden 的上升沿的一个时钟周期后,

③、display_image_data 数据用很多个时钟传完一帧图像数据。

④、display_image_clr 复位清除信号 高脉冲拉低后,

⑤、display_image_rden 读数据有效信号拉高,在display_image_rden 的上升沿的一个时钟周期后,

⑥、display_image_data 数据用很多个时钟传完一帧图像数据。

⑦、。。。。。。

3、显示驱动

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?