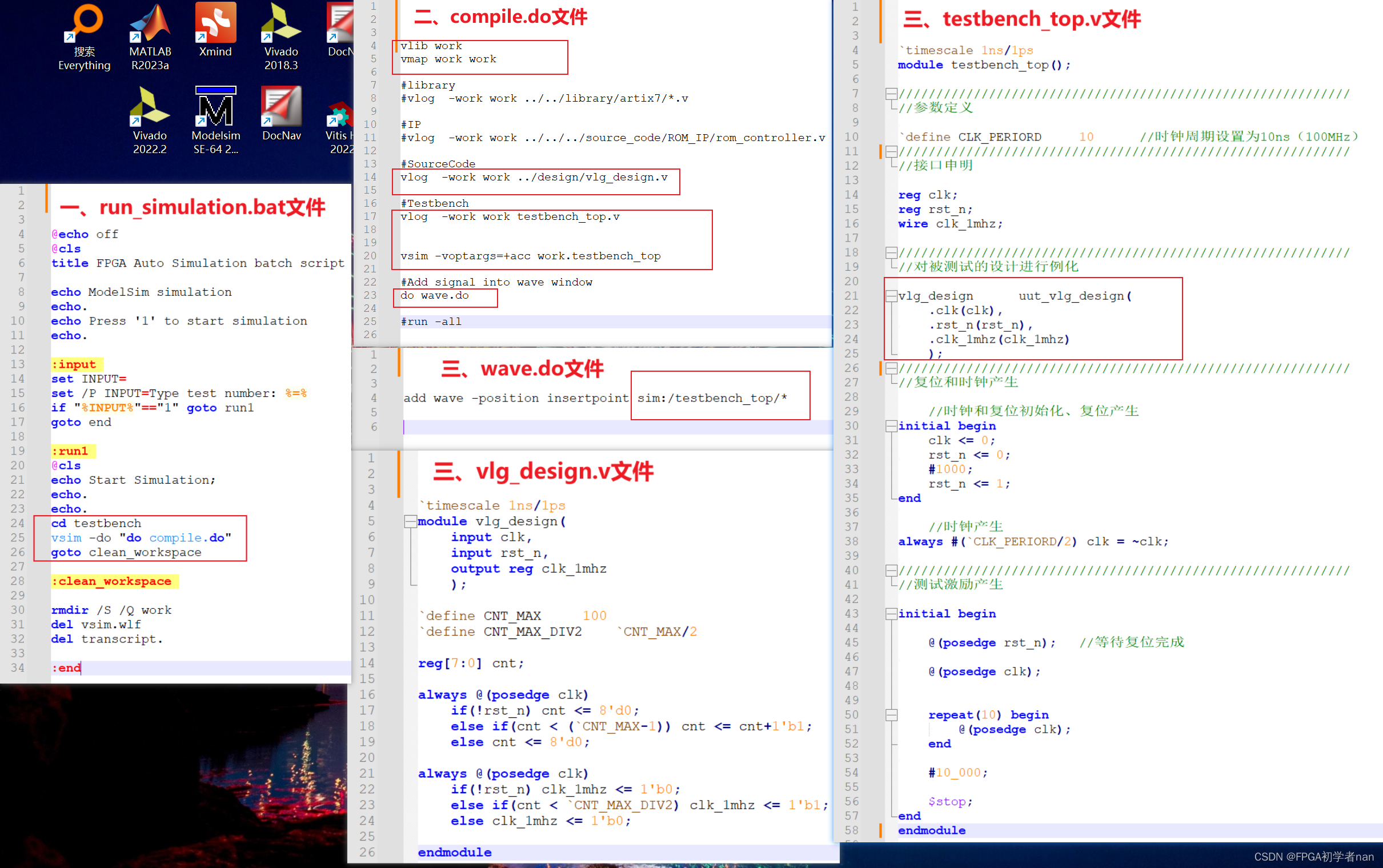

一、文件代码执行原理

一、在 windows 系统下先执行名字叫做 run_simulation.bat 的批处理文件

这个文件的作用是:可以在批处理窗口选择需要仿真哪个模块,然后便调用仿真那个模块的 compile.do 文件

二、compile.do 文件是 modelsim 的自动仿真脚本

它首先会选取 名字叫 work 的仿真库,然后把设计代码文件 vlg_design.v 加入modelsim软件,接着把仿真代码 testbench_top.v 也加进modelsim软件 ,然后再 执行 wave.do文件 。

三、 这里有三个文件。分别是 设计文件 vlg_design.v,仿真文件testbench_top.v,波形显示文件wave.do

二、执行过程

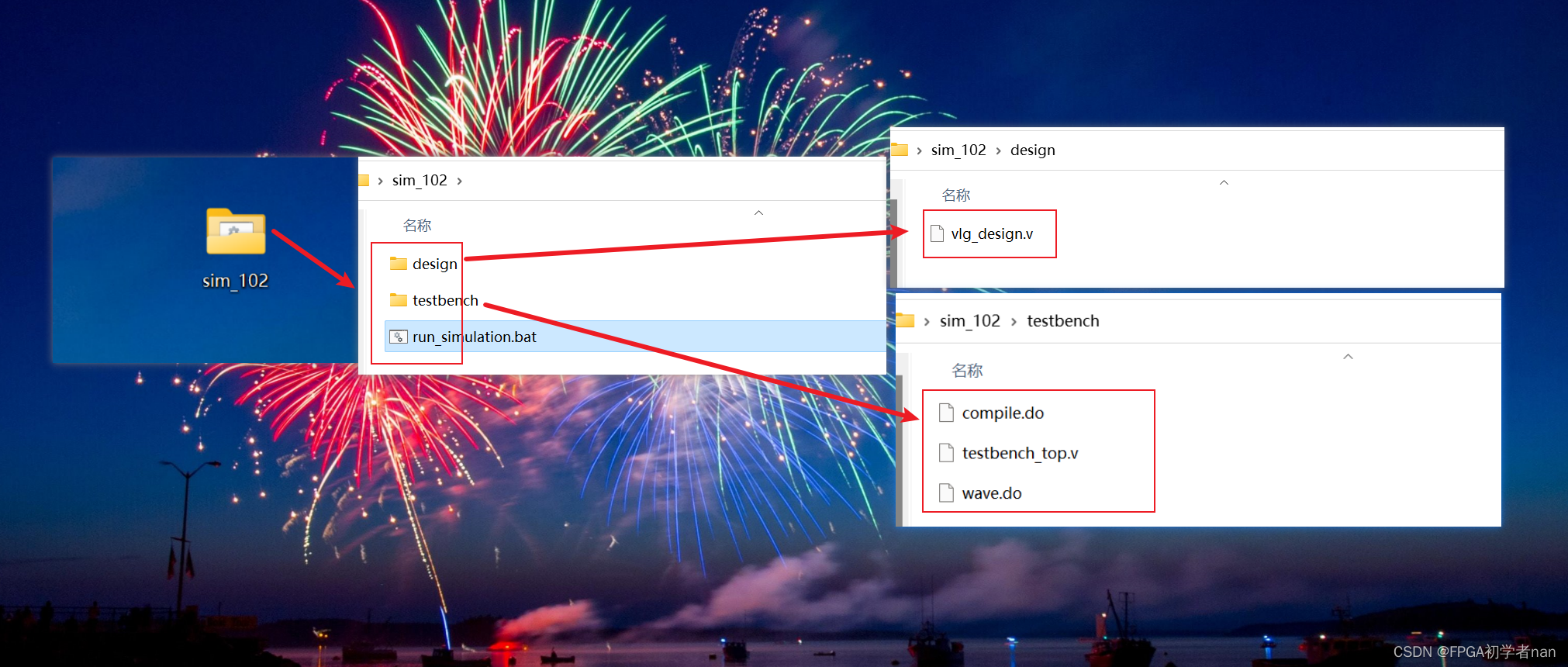

一、文件结构

sim_102是桌面文件夹,打开后如图所示。

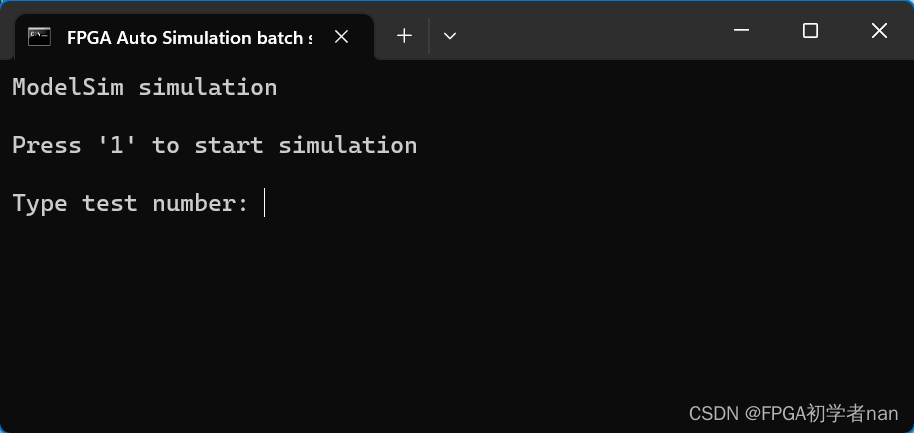

二、双击 run_simulation.bat 文件,弹出批处理窗口

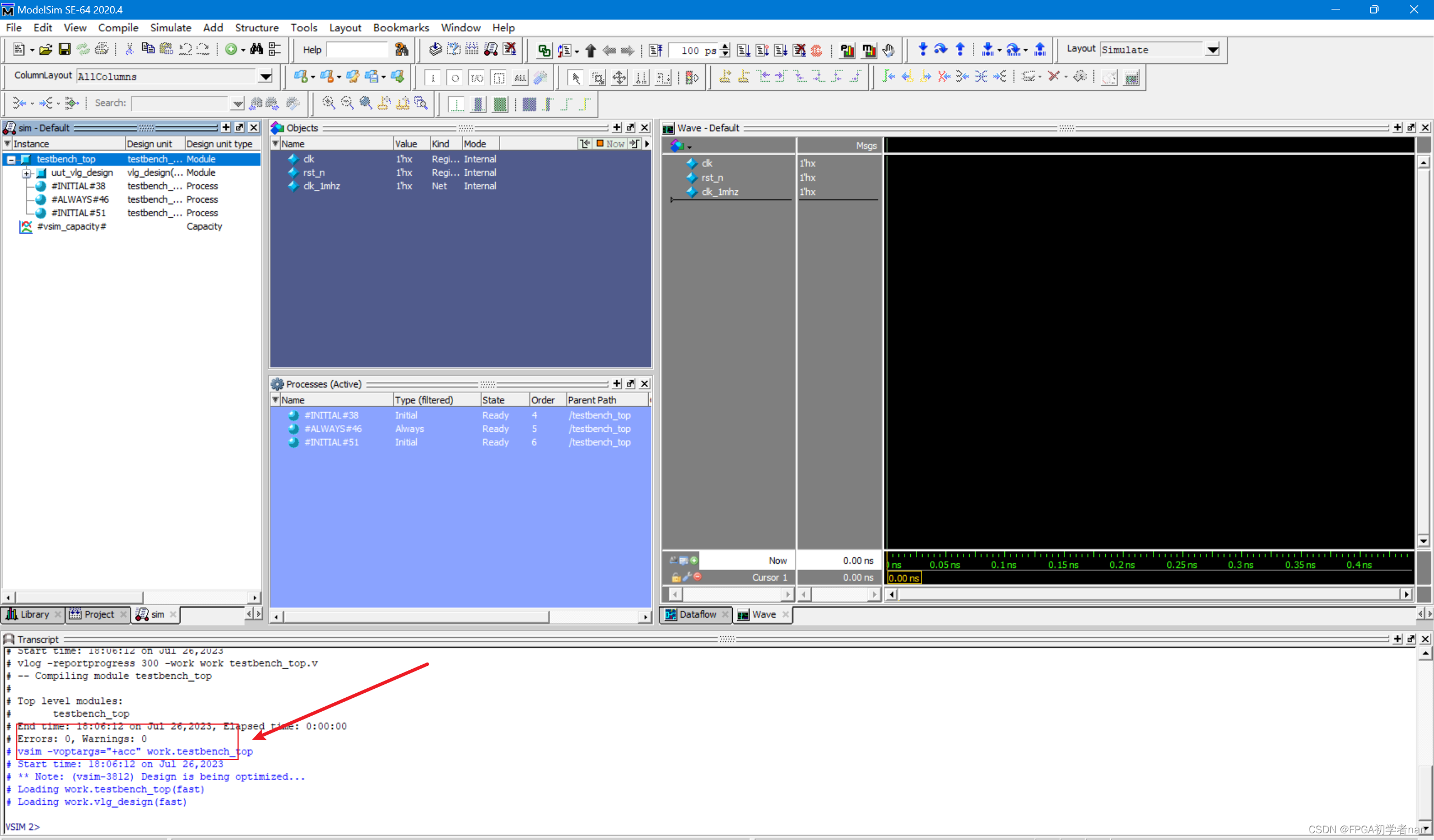

三、输入 “1”,然后回车,便会弹出 modelsim 的窗口。左下角显示没有错误,说明设计代码和测试代码无误。

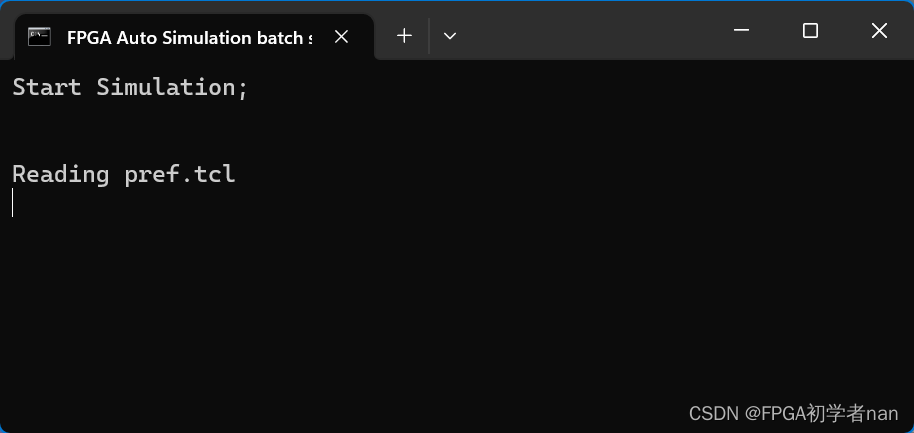

与此同时,这个批处理窗口变成这样

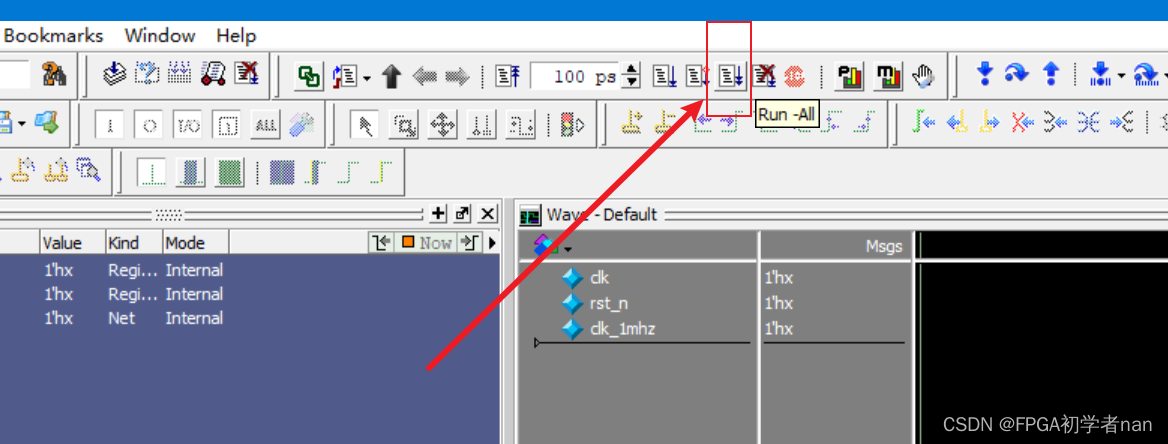

四、点击 点击modelsim软件的 “Run All” 开始仿真波形。

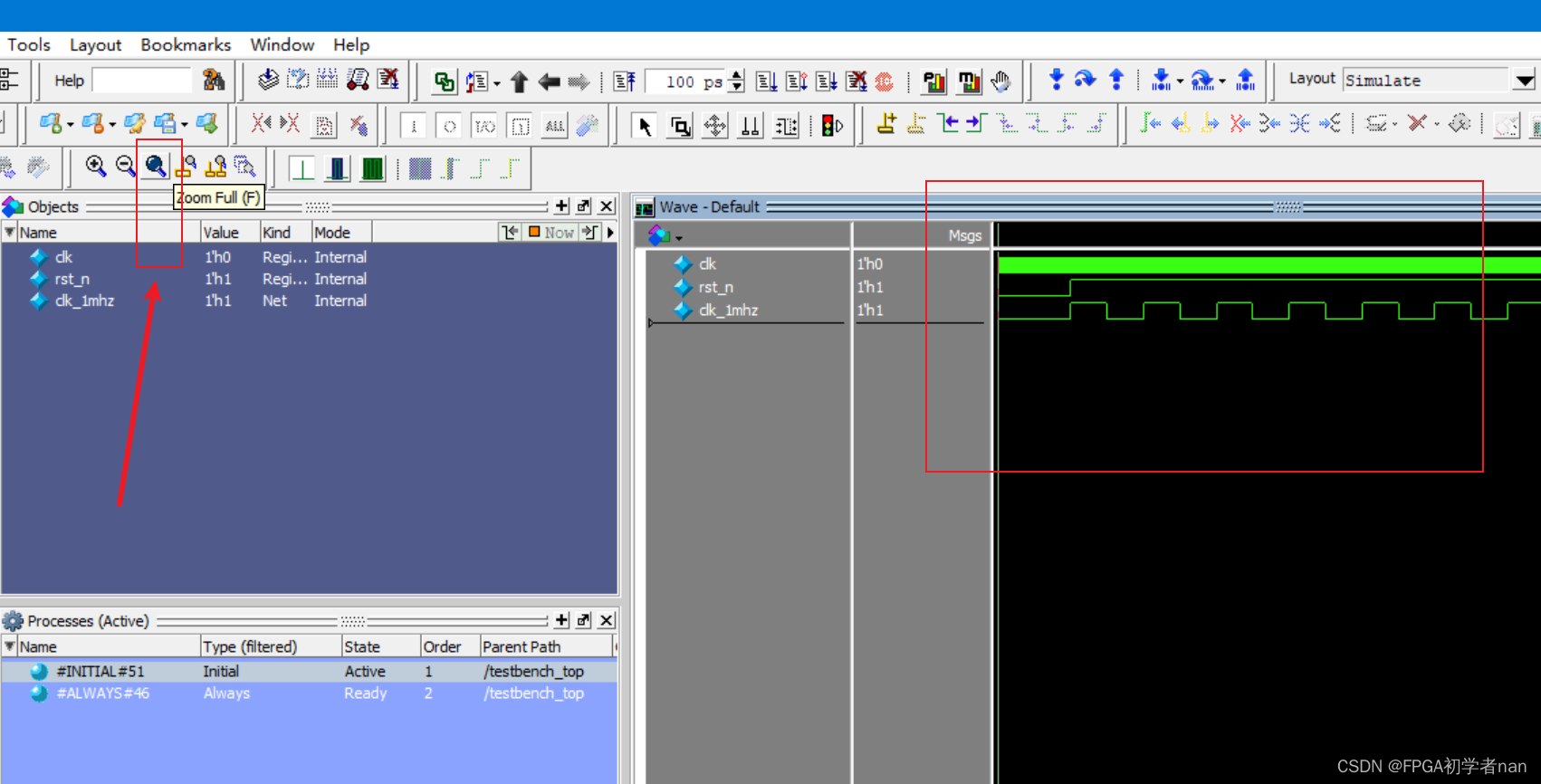

点击 “Zoom Full(F)”便可以看到波形。

三、全部的脚本如下

1、run_simulation.bat 文件

@echo off

@cls

title FPGA Auto Simulation batch script

echo ModelSim simulation

echo.

echo Press '1' to start simulation

echo.

:input

set INPUT=

set /P INPUT=Type test number: %=%

if "%INPUT%"=="1" goto run1

goto end

:run1

@cls

echo Start Simulation;

echo.

echo.

cd testbench

vsim -do "do compile.do"

goto clean_workspace

:clean_workspace

rmdir /S /Q work

del vsim.wlf

del transcript.

:end2、compile.do 文件 。带有“#”号的表示是注释行,是不执行的代码。

vlib work

vmap work work

#library

#vlog -work work ../../library/artix7/*.v

#IP

#vlog -work work ../../../source_code/ROM_IP/rom_controller.v

#SourceCode

vlog -work work ../design/vlg_design.v

#Testbench

vlog -work work testbench_top.v

vsim -voptargs=+acc work.testbench_top

#Add signal into wave window

do wave.do

#run -all3、wave.do 文件

add wave -position insertpoint sim:/testbench_top/*4、vlg_design.v 文件

`timescale 1ns/1ps

module vlg_design(

input clk,

input rst_n,

output reg clk_1mhz

);

`define CNT_MAX 100

`define CNT_MAX_DIV2 `CNT_MAX/2

reg[7:0] cnt;

always @(posedge clk)

if(!rst_n) cnt <= 8'd0;

else if(cnt < (`CNT_MAX-1)) cnt <= cnt+1'b1;

else cnt <= 8'd0;

always @(posedge clk)

if(!rst_n) clk_1mhz <= 1'b0;

else if(cnt < `CNT_MAX_DIV2) clk_1mhz <= 1'b1;

else clk_1mhz <= 1'b0;

endmodule5、testbench_top.v 文件

`timescale 1ns/1ps

module testbench_top();

//参数定义

`define CLK_PERIORD 10 //时钟周期设置为10ns(100MHz)

//接口申明

reg clk;

reg rst_n;

wire clk_1mhz;

//对被测试的设计进行例化

vlg_design uut_vlg_design(

.clk(clk),

.rst_n(rst_n),

.clk_1mhz(clk_1mhz)

);

//复位和时钟产生

//时钟和复位初始化、复位产生

initial begin

clk <= 0;

rst_n <= 0;

#1000;

rst_n <= 1;

end

//时钟产生

always #(`CLK_PERIORD/2) clk = ~clk;

//测试激励产生

initial begin

@(posedge rst_n); //等待复位完成

@(posedge clk);

repeat(10) begin

@(posedge clk);

end

#10_000;

$stop;

end

endmodule

该文介绍了如何在Windows系统下通过run_simulation.bat批处理文件启动Verilog代码的仿真流程。首先,批处理文件调用compile.do,将设计文件vlg_design.v和测试代码testbench_top.v加载到ModelSim中,并执行wave.do来显示波形。整个过程包括设计代码和测试代码的验证以及波形的可视化。

该文介绍了如何在Windows系统下通过run_simulation.bat批处理文件启动Verilog代码的仿真流程。首先,批处理文件调用compile.do,将设计文件vlg_design.v和测试代码testbench_top.v加载到ModelSim中,并执行wave.do来显示波形。整个过程包括设计代码和测试代码的验证以及波形的可视化。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?