硬件排坑笔记

1.MOS管悬空

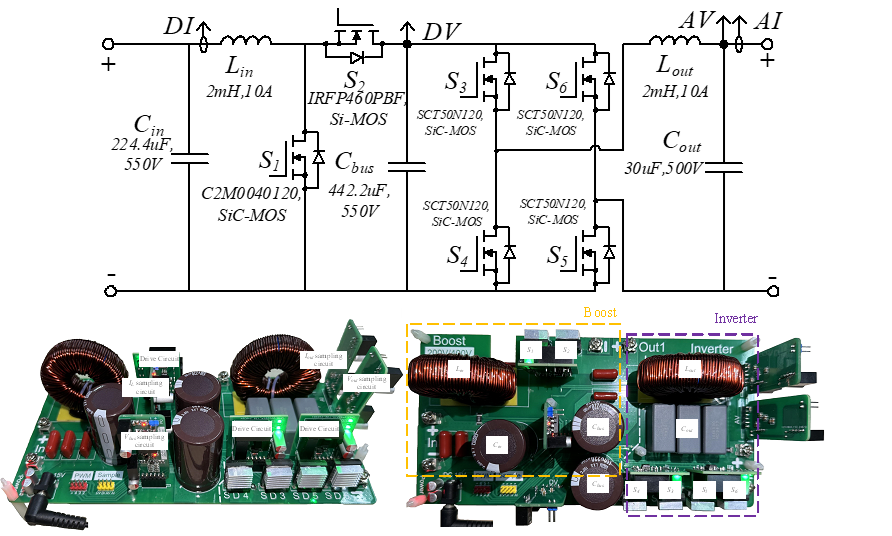

首先给出电路图,如下图所示:

问题:

一开始调试板子时,准备逐级调试Boost和Invert,因此直接把后级的驱动小板拔了,这样的话后级的Mos就悬空了。

上电测试时,发现上电调节输入电压时,后级Mos发热严重。一开始以为是Mos管的问题,因此把逆变器Mos全换了,但是换完后依旧会出现这种问题,后面分析发现是Mos悬空的问题。

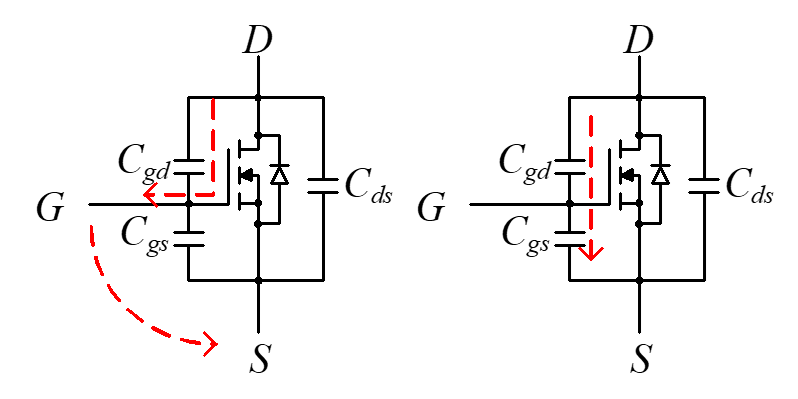

Mos管的寄生电容等效模型如下图:

原因:

假设Mos管正常给驱动,即G、S短路。当Vds发生变化的时候,I=C du/dt,产生感应电流。除了Cds吃了这个电流的大部分外(Cds一般较大),这个电流还将从左图路径走,即从驱动电路走。

当Mos管G悬空时,无法通过驱动电路为这个感应电流提供路径,那么这个电流只能走右图的路径,可以发现,Cgs将被充电,这时极有可能将Mos从关断区拉到放大区,3~4V左右的栅极电压,其Mos工作在放大区,这就导致了逆变器Mos发热严重。

2.电流采样电路的共模影响

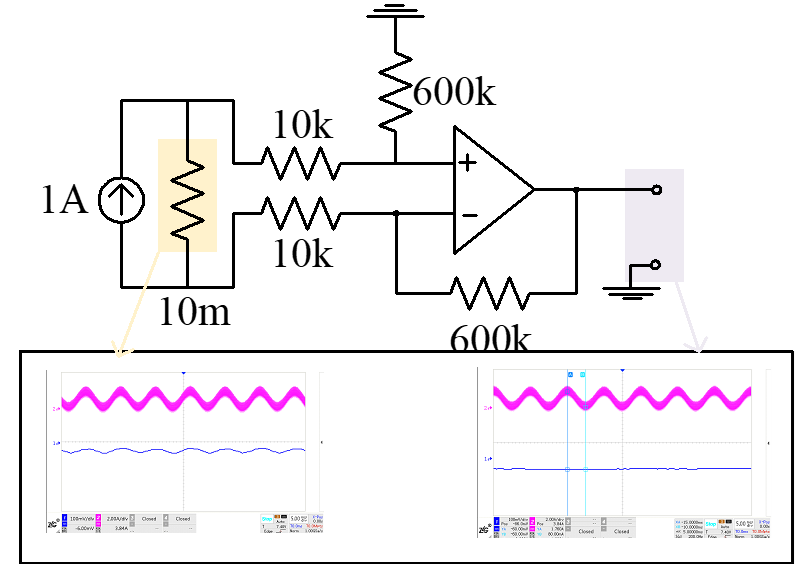

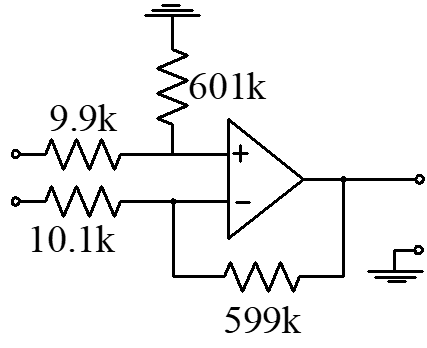

这里采用的电流采样电路为差分放大电路,具体拓扑如下,其中光耦隔离、补偿设计部分的电路就不展开了。

问题:

采样电阻上的电压输入正常,但输出电压反而不见了。并且这个电流采样电路模块单独测试是没问题的,但放在主电路后,随着输入电压升高,其输出电压反而越低,最后消失不见,接近运放的低电压轨。

原因:

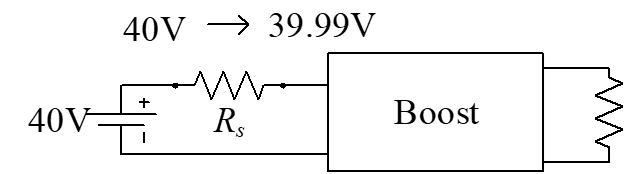

采样示意图如下:

可以看到这个采样的共模电压较高,而我的差分放大电路是用分立器件搭建的,因此元件参数误差偏离是难免的。其实际的电路参数大概率如下:

假设各电阻偏移1%,如上图所示,那么差分放大倍数AVD≈60,共模放大倍数AVC≈-0.0227,假设Vd=10mV,Vc=30V,Vo=0.01*60-30* 0.0227=-0.081V<0V=0V。

符合实验现象:

1、模块单独测试,正常工作;

Vin=30mV Vout =1.5V

2、接上主电路后,输入电压越高, Vout反而越小,直至消失

上面计算式子参考文献如下,不再具体推导。

[1]张华,邱红,宋智.由于电阻精度引起差分放大电路误差的分析[J].现代电子技术,2007(18):181-182.DOI:10.16652/j.issn.1004-373x.2007.18.014.

后面直接使用集成差分放大电路IC-INA240A2DR解决这个问题。

1074

1074

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?