序言

通过导入VEC格式的数字激励给模拟电路是一种Cadence常见的进行数模混合仿真的方法。

其优势在于相比AMS混合仿真更便捷,缺点则在于输入数字激励较为理想化,无法将模拟的反馈提供给数字电路。

Cadence仿真中导入VEC格式激励

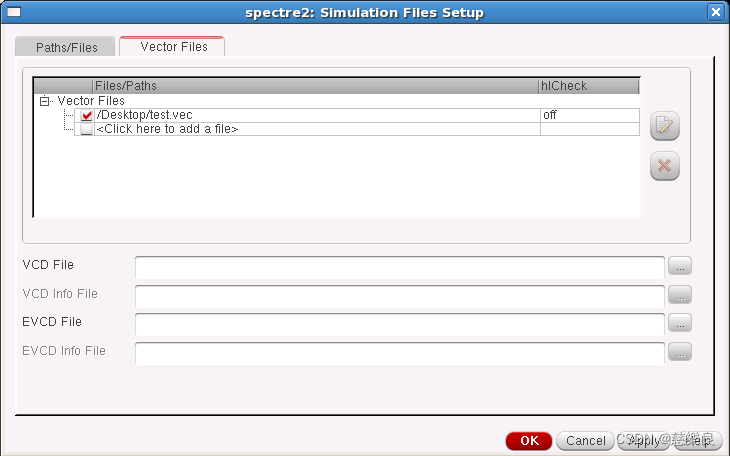

从ADE L中Setup - Simulation Files - 选择Vector Files,输入vec文件路径即可。

vec中激励不会显示在schematic中,但可以通过net名来连接。

VCD转换VEC方法——使用HSIM中的vcd2vec

VCD格式激励示例

由QuestaSim生成的VEC激励部分代码如下所示,可见其有两个激励信号CLK和ENABLE。

对于转换需要,要将信号的module top 删除,只保留激励,见注释。

$scope module TB $end //此行删除

$scope module DIG_TOP $end //此处删除

$var reg 1 ! CLK $end

$var wire 1 " ENABLE $end

$upscope $end //此处删除

$upscope $end //此处删除

$enddefinitions $end

#0

$dumpvars

0!

x"

$end

#10000

0"

#4000000

1!

#6000000

0!

#8000000

1!

io_top.sig文件格式激励示例

转换需要的io_top.sig文件格式如下所示,包含了输入的激励名称,输入高低电平,输出高低电平,上升下降时间等参数,此文件需要自己准备。

#in CLK

#in ENABLE

#vih 3.3

#vil 0

#voh 1.8

#vol 0

#trise 100p

#tfall 100p

#slope 100p

转换指令

从terminal中输入如下指令可将File1.vcd文件通过 io_top.sig文件转换为File1.vec文件。生成的vec文件即可导入cadence中进行仿真。

vcd2vec - d -nvcd File1.vcd -nsig io_top.sig -nvec File1.vec

本文介绍了如何在Cadence仿真中导入VEC格式激励,包括从ADEL中选择和导入VEC文件,以及使用HSIM的vcd2vec工具将VCD格式转换为VEC。还提供了io_top.sig文件格式的激励示例和转换指令。

本文介绍了如何在Cadence仿真中导入VEC格式激励,包括从ADEL中选择和导入VEC文件,以及使用HSIM的vcd2vec工具将VCD格式转换为VEC。还提供了io_top.sig文件格式的激励示例和转换指令。

7459

7459

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?