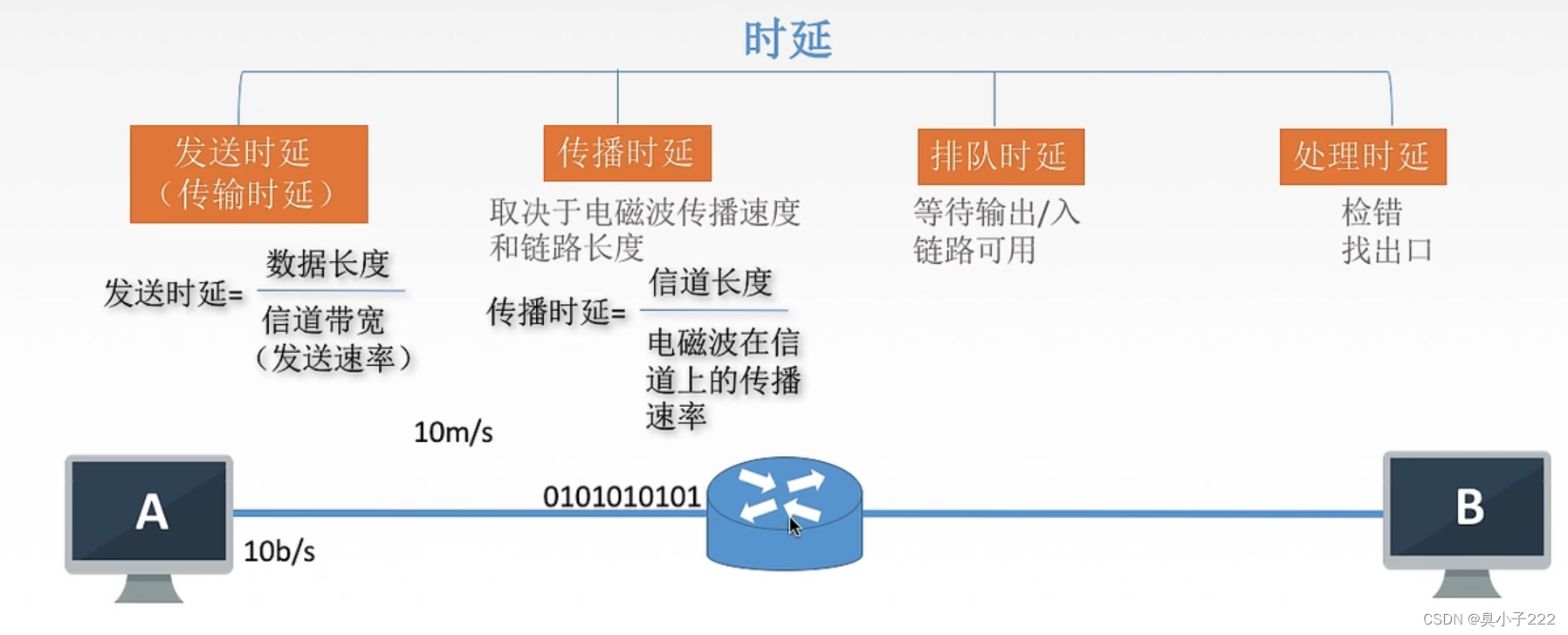

时延

时延:数据(报文、分组、比特流)从网络的一端传送到另一端所需要的时间。也叫延迟或迟延,单位是s。

时延包括:发送时延(传输时延),传播时延,排队时延,处理时延。

高速链路:发送速率提高,并不会影响电磁波的传输速度

传输速度仅仅与传播介质有关,电磁波传播是固定的。

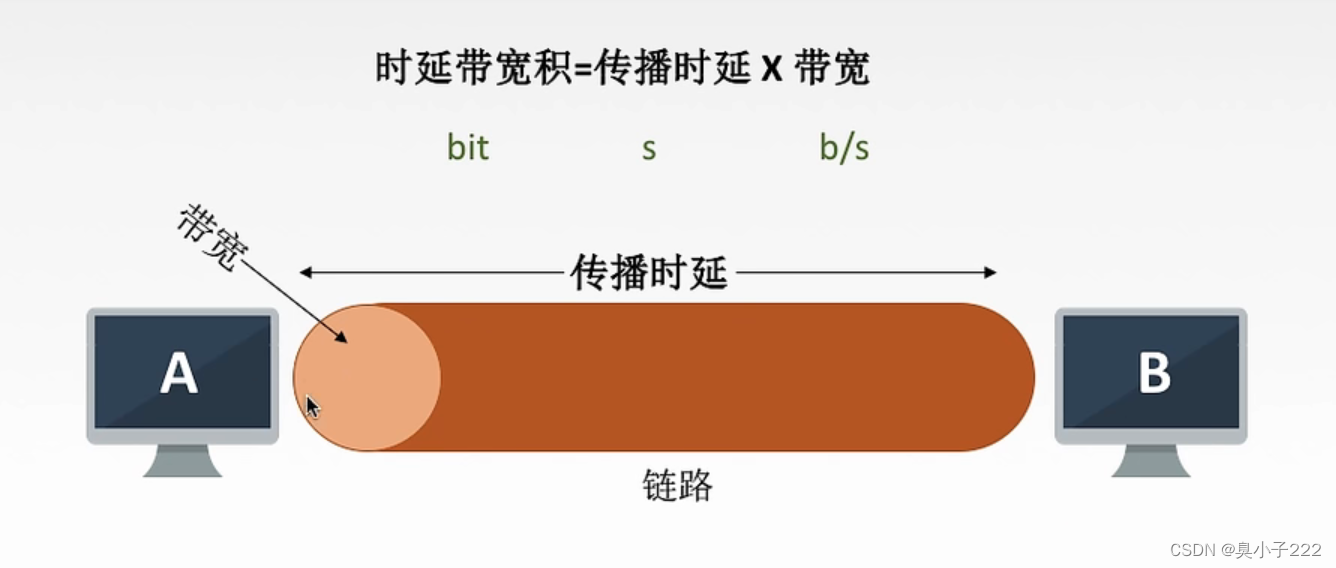

时延带宽积

时延带宽积=传播时延*带宽。时延带宽积其实表示的包含的数据量。

时延带宽积又可称为以比特为长度的链路长度。即某段链路现在有多少比特。

RTT

往返时延RTT:发送方发送数据开始到收到接收方确认消息总共经历的时延。

RTT越大,在收到确认之前可以发送的数据就越多

RTT包括:往返传播时延(传播时延*2)和末端处理时延

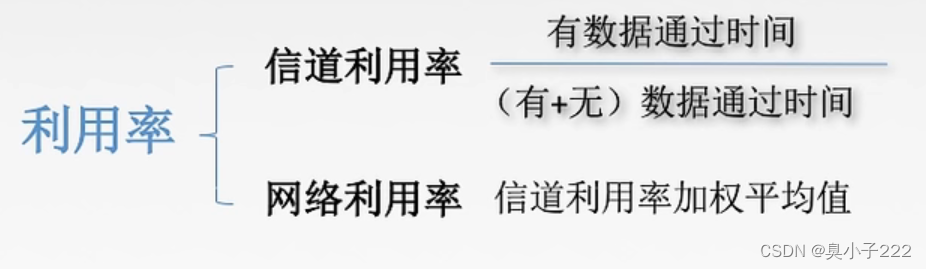

利用率

利用率包括:信道利用率和网络利用率

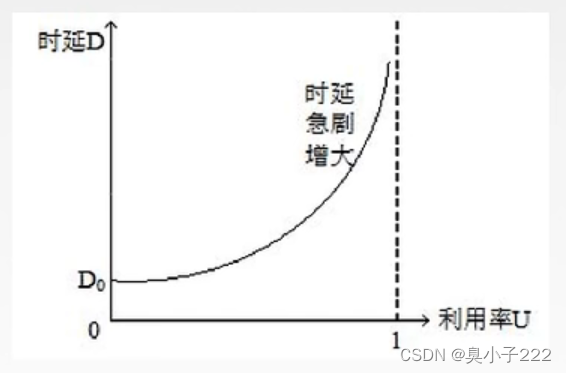

时延和利用率的关系:

那车流举例子,车道中车辆越多,汽车通过时间越大

时延是指数据在网络中传输所需的时间,包括发送、传播、排队和处理等环节。时延带宽积等于传播时延与带宽的乘积,反映链路的数据容量。RTT是往返时延,从发送数据到接收到确认的总时间,它与能发送的数据量有关。利用率则涉及信道和网络的使用效率,时延和利用率之间的关系可以通过交通流量类比来理解,车辆多时,通过时间会增加。

时延是指数据在网络中传输所需的时间,包括发送、传播、排队和处理等环节。时延带宽积等于传播时延与带宽的乘积,反映链路的数据容量。RTT是往返时延,从发送数据到接收到确认的总时间,它与能发送的数据量有关。利用率则涉及信道和网络的使用效率,时延和利用率之间的关系可以通过交通流量类比来理解,车辆多时,通过时间会增加。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?