前言

截止2022年2月15日,中国科学院大学《高等数字集成电路分析及设计》课程终于完结,所以我计划分享几个自己完成的实践作业,供大家交流学习。

设计收获

- 体会到了verilog语法的痛点:在数组赋值、连续加法等方面操作很不方便

数据排序题目

设计一个时序逻辑电路,对输入32个8位无符号整数从小到大进行排序(若存在多个数据值相等,则不分先后,见例子)。例如:

- 输入32个数据依次为:31, 29, 27, 25, 23, 21, 19, 17, 15, 13, 11, 9, 7, 5, 3, 1, 2, 2, 4, 4, 4, 4, 8, 16, 8, 16, 32, 32, 0, 10, 20, 30

- 输出32个数据依次为:0, 1, 2, 2, 3, 4, 4, 4, 4, 5, 7, 8, 8, 9, 10, 11, 13, 15, 16, 16, 17, 19, 20, 21, 23, 25, 27, 29, 30, 31, 32, 32

顶层模块名为sort_32_u8,输入输出功能定义:

| 名称 | 方向 | 位宽 | 描述 |

|---|---|---|---|

| clk | I | 1 | 系统时钟 |

| rst_n | I | 1 | 系统异步复位,低电平有效 |

| vld_in | I | 1 | 输入数据有效指示 |

| din_0, din_1, … …, din_31 | I | 8 | 输入数据0,输入数据1,……, 输入数据31 |

| vld_out | O | 1 | 输出数据有效指示 |

| dout_0, dout_1, … …, dout_31 | O | 8 | 输出数据0,输出数据1,……, 输出数据31 |

注:din_0 ~ din_31共32个输入端口,dout_0~ dout_31共32个输出端口。输出数据dout_0 ~ dout_31的值从小到大排列。

设计要求:

- Verilog实现代码可综合,给出综合以及仿真结果。

- 逻辑资源和延迟需要做权衡,使得数据输入到结果输出延迟周期数尽量

说明

本作业代码设计代码参考

https://blog.csdn.net/yanchuan23/article/details/79780605中第二种并行全比较排序法的思路,但原始参考中代码不全,且verilog语句中有不可综合语句,这里进行了改进。

架构和原理

基于并行全比较,计算每个输入数据的得分,然后依据得分结果进行排序输出。大致划分为三级流水来实现。

第一个时钟周期:将其中一个数据和其他数据在一个周期中一一比较,比较器分三种情况:

- 这个数据小于其他数据,则它的得分为0;

- 这个数据等于其他数据,若它在这个序列中比和它相等的其他数据靠前,则它的得分为0,反之为1;

- 这个数据大于其他数据,则它的得分为1;

第二个时钟周期:将每个数据和其他数据比较后的数据累加;

第三个时钟周期:将每个数据根据自己的得分赋值给新的数组(若得分为1的就赋值给数组中的第一个数,2就赋值给新的数组中第二个数);

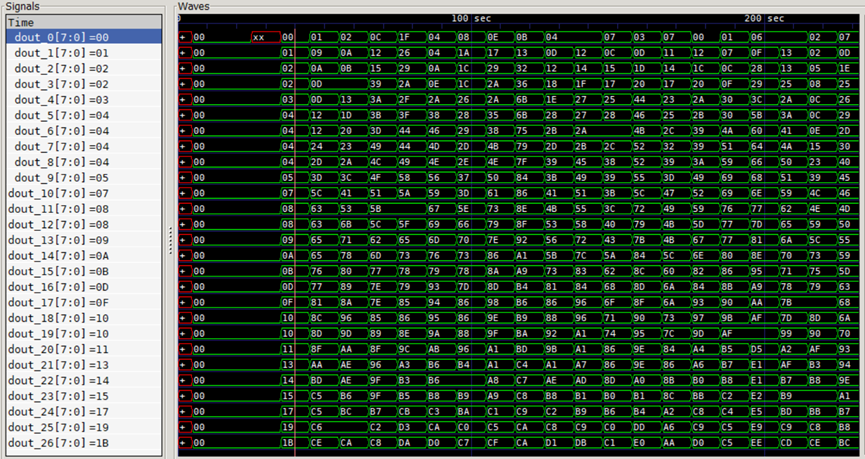

仿真(iverilog)

通过观察波形可以知道,设计实现了文档要求的功能。

附录

源码获取见原文底部

434

434

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?