Register

介绍

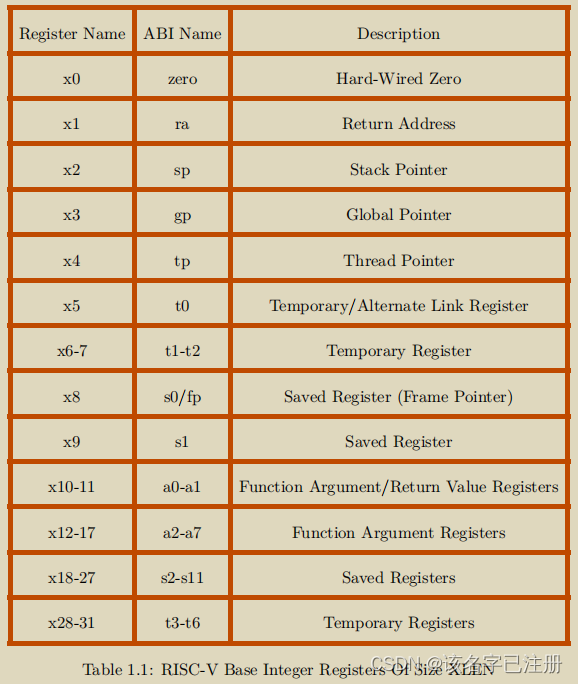

RISC-V架构提供31个用户可修改的通用(基本)寄存器,即x1到x31,以及一个额外的只读寄存器x0,硬连接到0。x0寄存器的一个常见用途是帮助将其他寄存器初始化为零。

• 共有31个通用寄存器。

• 其中7个是临时寄存器(t0−t6)。

• a0−a7用于函数参数。s0−s11用于保存寄存器或函数定义内。

• 一个堆栈指针,一个全局指针和一个线程指针寄存器。

• 一个返回地址寄存器(x1),用于存储函数调用的返回地址。

• 一个程序计数器(pc)。PC保存着当前指令的地址。

• 所有寄存器都可以作为通用寄存器使用

Stack Pointer Register(SP)

在RISC-V体系结构中,x2寄存器被用作栈指针(sp),并保存栈的基址。此外,栈基址必须对齐到4个字节。如果不这样做,可能会出现加载/存储对齐错误。

Global Pointer Register(GP)

RISC-V使用x3 (gp)寄存器将所有全局变量放置在指定的特定区域。x3寄存器将保存全局变量所在位置的基址。

Thread Pointer Register(TP)

在多线程应用程序中,每个线程可能有自己的私有变量集,称为“线程特定变量”。这组变量将由寄存器x4 (tp)指向。

因此,每个线程在其x4寄存器中都有一个不同的值。

Return Address Register(RA)

x1 (ra)寄存器用于保存子程序的返回地址。在执行子程序调用之前,x1设置为子程序的返回地址,通常为“pc + 4”。标准的软件调用约定使用x1 (ra)寄存器来保存函数调用的返回地址。

Argument Register(参数寄存器)

在RISC-V中,8个参数寄存器,即x10−x17(对应a0−a7)用于在子程序中传递参数。

在子程序调用之前,子程序的参数被复制到参数寄存器。在参数数量超过8的情况下使用栈。

Temporary Register(临时寄存器)

临时寄存器用于在指令执行期间保存中间值。在RISC-V中有7个临时寄存器(t0−t6)。

Privilege mode

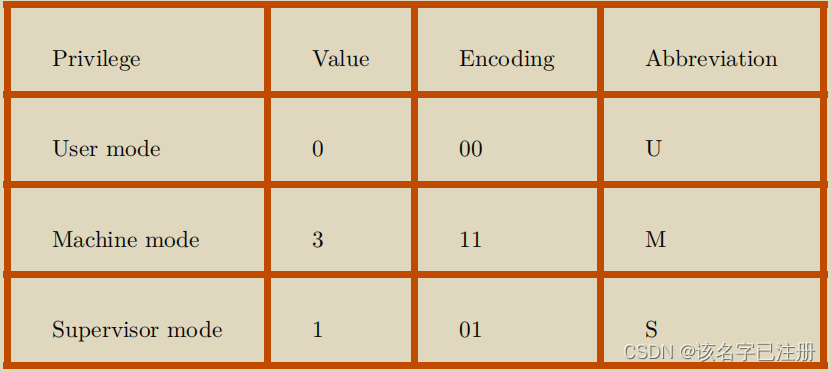

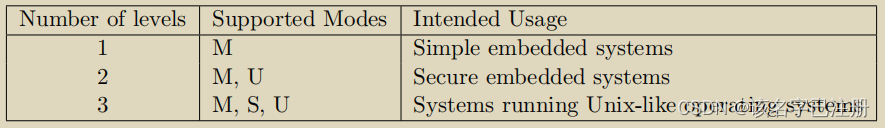

risc-v架构将特权等级分为三个M、S、U。

User Mode:简称U 通常运行应用程序

Supervisor Mode:简称S 通常运行操作系统

Machine Mode:简称M 用于管理安全执行环境,最高权限,必选,其他两种模式都是可选的。

三种模式可以互相切换

Control and Status Registers (CSRs)

Registers

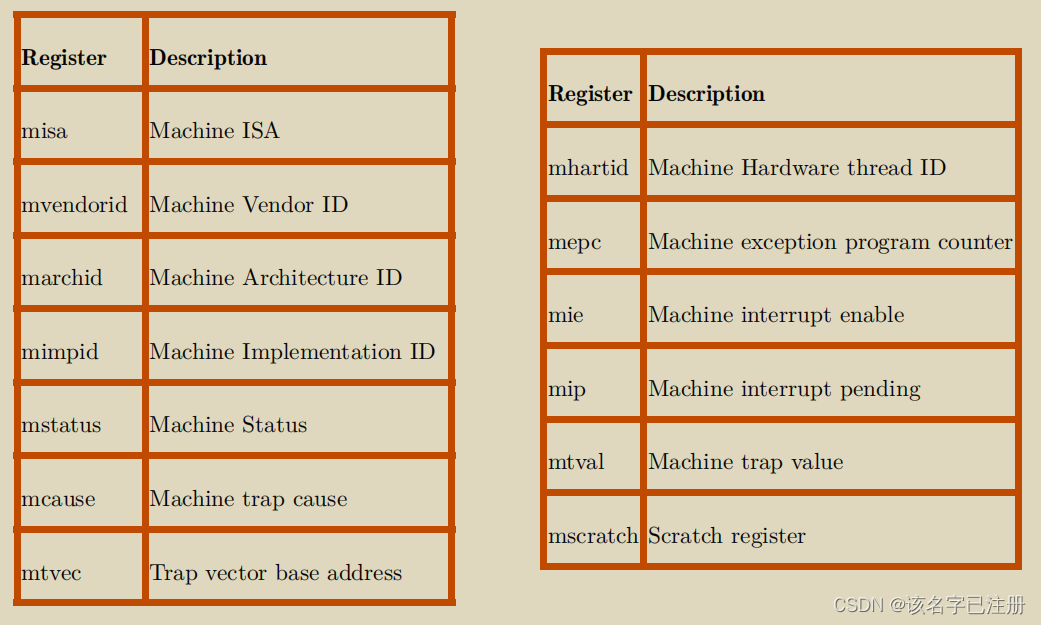

CSR寄存器非常多,下图为一些经常使用到的寄存器

MSTATUS(Machine Status Register)

Machine Status Register(MSTATUS)寄存器详细描述了机器的状态,并帮助控制机器的状态。mstatus寄存器有几个位来控制机器的不同状态。

](https://i-blog.csdnimg.cn/blog_migrate/963108ce46a1f20e2e69d08b09aa6f4e.png)

MSTATUS包含许多可以读取和更新的字段。通过修改这些字段,软件可以做一些事情,比如启用/禁用中断和更改虚拟内存模型等。

mstatus.MIE:Machine- Mode interrupt enable,机器模式全局中断使能位

mstatus.SIE: Supervisor-Mode interrupt enable,管理员模式全局中断使能位

x IE:=1则使能全局中断,=0则关闭全局中断,其只能控制小于或等于x模式下的中断,比如SIE=0,M模式下的中断不受其影响。

mstatus.MPIE:Machine- Mode previous interrupt enable,机器模式先前中断使能位

mstatus.SPIE:Supervisor-Mode previous interrupt enable,管理员模式先前中断使能位

x PIE:保存在trap之前interrupt-enable(x IE)位的值。

mstatus.MPP:Machine- Mode previous privilege,机器模式先前特权模式

mstatus.SPP:Supervisor- Mode previous privilege,管理员模式先前特权模式

x PP:保存trap之前的特权模式。xPP字段只能持有最多x的特权模式,因此MPP是2位宽,SPP是1位宽。

mstatus.MPRV:MPRV (Modify PRiVilege)位修改有效特权模式,即加载和存储执行时的特权级别。当MPRV=0时,使用当前特权模式的转换和保护机制,加载和存储行为正常。当MPRV=1时,加载和存储内存地址被转换和保护,并应用字节顺序,就好像当前特权模式被设置为MPP。指令地址转换和保护不受MPRV设置的影响。如果不支持U-mode,则MPRV为只读0。

当使用mret从trap中返回。会根据MPP的值来确定返回的新的特权模式,然后硬件改写mstatus中的MPP=0,MIE=MPIE,MPIE=进trap前的MIE,并设置PC=MEPC。

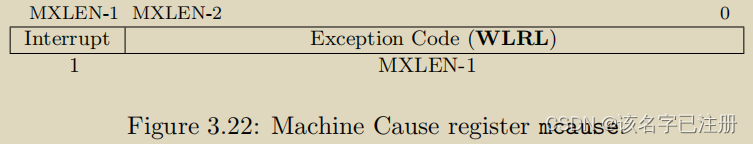

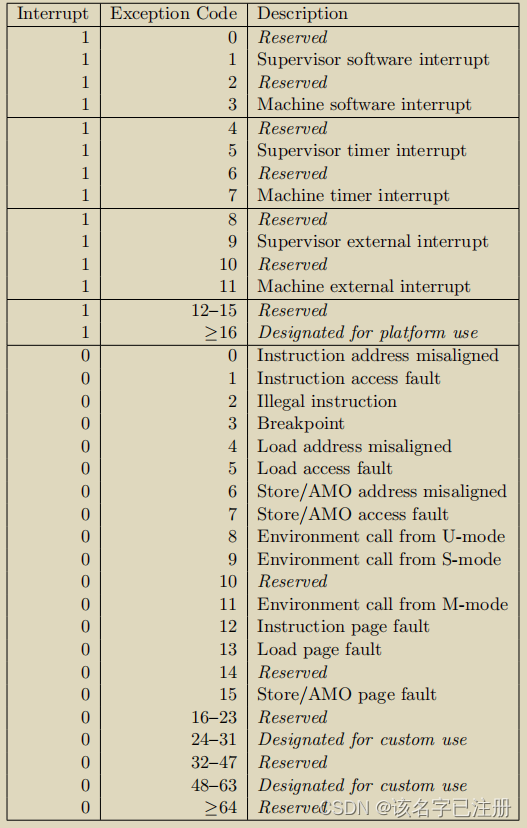

MCAUSE(Machine Cause Register)

Machine Cause Register寄存器是一个mxlen位的读写寄存器。当一个trap被带入m模式时,mcause被硬件写入一个代码,指示导致该trap的事件。如果trap是由中断引起的,则设置mcause寄存器中的中断bit位。

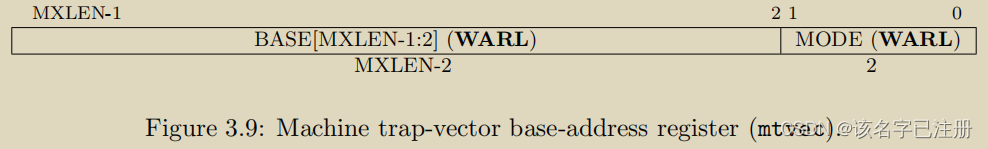

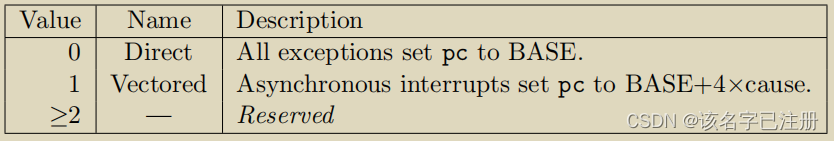

MTVEC(Machine Trap Vector Base Address register)

MTVEC用于存储Trap处理程序的地址。就是存储中断向量表的基地址。写入MTVEC的地址必须是4字节对齐的地址,不然异常向量表不生效

当MODE=Direct时,所有进入机器模式的trap都会导致pc被设置为BASE字段中的地址。当MODE= vector时,所有进入机器模式的同步异常都会导致pc被设置为BASE字段中的地址,而异步中断会导致pc被设置为BASE字段中的地址加上中断cause数的四倍。

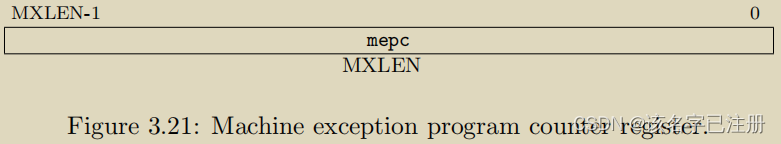

MEPC(Machine Exception Program Counter)

它保存导致trap的指令的地址。

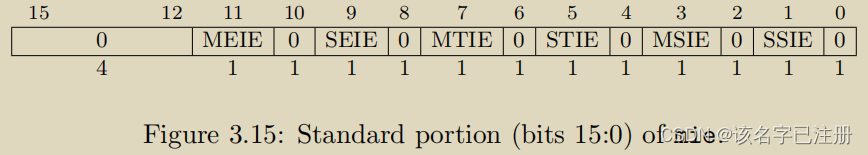

MIE(Machine Interrupt Enable Register)

中断使能寄存器,区别于mstatus.MIE作为全局控制,MIE是局部控制。

MEIE:M模式外部中断使能位

SEIE:S模式外部中断使能位

MTIE:M模式timer中断使能位

STIE:S模式外部中断使能位

MSIE:M模式软中断使能位

SSIE:S模式软中断使能位

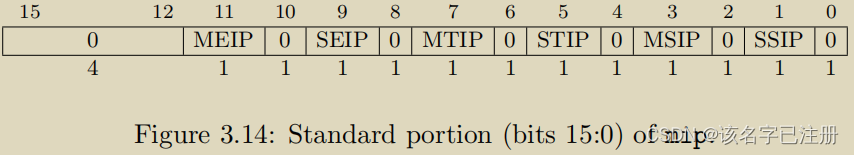

MIP(Machine Interrupt Pending Register )

中断挂起寄存器,包含关于挂起中断的信息。

我的理解:当正在处理一个中断,并且mie关掉中断时,同时设置了mip,此时产生了另一个中断则其会被pending,则MIP里对应的中断信息会被记录。

MEIP:M模式外部中断挂起位

SEIP:S模式外部中断挂起位

MTIP:M模式timer中断挂起位

STIP:S模式外部中断挂起位

MSIP:M模式软中断挂起位

SSIP:S模式软中断挂起位

MSCRATCH

mscratch 寄存器用于机器模式下的程序临时保存某些数据。mscratch 寄存器可以提供一

种快速的保存和恢复机制。譬如,在进入机器模式的异常处理程序后,将应用程序的某个通

用寄存器的值临时存入 mscratch 寄存器中,然后在退出异常处理程序之前,将 mscratch 寄

存器中的值读出恢复至通用寄存器。

CSR Instructions

Register to Register instructions

在系统的两个寄存器上执行指定的操作,并将结果留在指定的寄存器中。

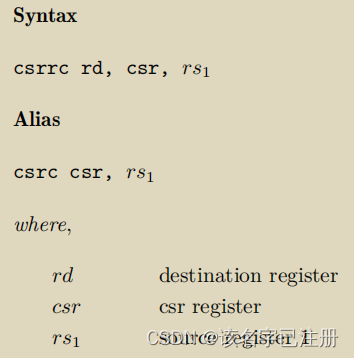

CSRRC

CSRRC:CSR Read and Clear Bits,用于清除CSR。

将之前CSR的值复制到目的寄存器,然后将CSR的一些选定位清除为0,rs1的值作为位掩码,用于选择CSR中哪些位需要清除(逻辑与 and)。

例子:

csrrc x1, mcause, x2 将之前的mcause读取到x1,并与x2逻辑与

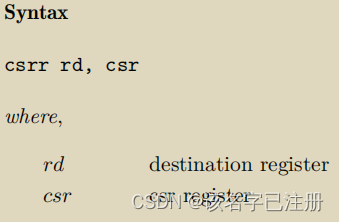

CSRR

CSRR:CSR Read,用于读取CSR。

CSRR指令用于读取CSR的值。将CSR的前一个值复制到目标寄存器。这是一个原子读取操作。

例子:

csrr x1, mtvec 读取mtvec到x1

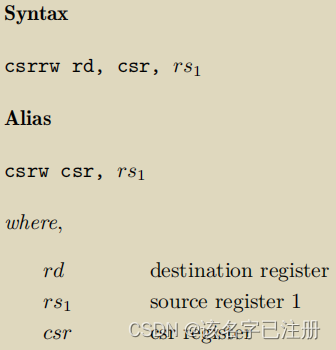

CSRRW

CSRRW:CSR Read and Write,用于读写CSR。

将CSR的前一个值复制到目标寄存器,源寄存器的值(rs1)被复制到CSR,这是一个原子写操作。要读取CSR而不写入它,源寄存器(rs1)可以指定为x0。要编写CSR而不读取它,目标寄存器(rd)可以指定为x0。这是一个原子操作。

简单来说就是rd是读CSR到rd中,rs1是将rs1的值写入到CSR。

例子:

csrrw x0, mtvec, x1 将x1中的值写入mtvec

csrrw x1, mtvec, x0 读取mtvec到x1

csrrw x1, mtvec, x2 读取之前mtvec到x1,将x2写入mtvec

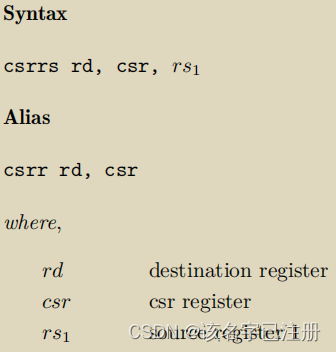

CSRRS

CSRRS:CSR Read and Set Bits,用于设置CSR的位。

将CSR之前的值复制到目标寄存器,然后将CSR的某些位设置为0,rs1中的值用作位掩码,用于选择在CSR中设置哪些位(逻辑或 or)。

例子:

csrrs x1, mstatus, x2 读取mstatus到x1,并与x2逻辑或

Immediate Instructions

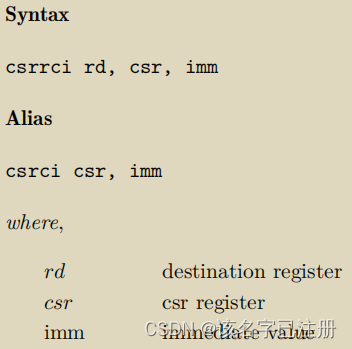

CSRRCI

CSRRCI:CSR Read and Clear Immediate

将之前CSR的值复制到目的寄存器,然后将立即数与CSR进行逻辑与操作,清除CSR指定的位。

例子:

csrrci x1, mie, 3 保存mie的值到x1中,并将mie与3按位与

其他的寄存器与上述寄存器到寄存器的指令同理

Trap

Exception

异常通常是同步的,并且总是与程序集指令相关联。异常可能在指令执行的任何阶段出现。例如,在指令解码阶段,硬件可能会检测到一个错误的操作码字段。这将触发一个“非法指令”异常。当异常发生时,硬件用相应的异常代码设置mcause寄存器。

pc被设置为trap处理程序的基地地址。异常代码有助于识别异常的类型。在RISC-V中可能的异常列在表中

• Illegal instruction (非法指令异常):当程序试图执行任何非法指令时,会发生异常。例如,试图写入只读CSR寄存器将产生非法指令异常。

• Instruction/Load/Store address misaligned (指令地址错位异常):当程序试图执行无条件跳转或执行目标地址不是4字节对齐的分支时,会发生异常。例如,执行一个起始地址为0x80000001的程序。这将在无条件跳转时生成一个指令地址错位异常。

• Instruction/Load/Store access fault (访问异常):当程序试图执行加载指令以访问来自未对齐地址或非4字节对齐的地址的数据时,会发生异常。例如,试图访问一个数据段而没有正确对齐,就会导致这个异常。

• Environment call (环境调用异常):当程序执行系统调用时发生此异常。需要使用RISC-V的ecall调用指令。调用指令还可以用于从低权限模式切换到高权限模式。指令:ecall

• Break point :当程序执行程序中设置的断点以进入调试模式时,会发生异常。

Handle Exception

一旦发生异常,处理器将停止执行并将控制传递给trap处理程序。

在此过程中,处理器特权被设置为Machine模式,处理器使用异常代码设置mcause寄存器。mepc设置为发生异常前指令所在的pc。所有异常都首先出现在机器模式trap处理程序中。这适用于来自不同特权级别的异常。机器模式trap处理程序在机器模式中执行。在trap处理程序中,首先寄存器的上下文被保存在栈中。然后处理trap。在此之后,栈中保存的上下文将被恢复。通过这种方式,可以在不给执行流造成太多麻烦的情况下处理trap。

硬件如何跳转到trap处理程序? 这是通过使用trap处理程序的物理地址设置mtvec寄存器来建立的。通常将mtvec中的值称为“Trap entry”。

我们有时可能不希望在Machine Mode中处理异常。我们可能想把它弄进去

管理员模式甚至用户模式。因此,可以将一些或所有trap“delegate”委托给较低的特权级别。

MRET:机器模式Trap处理程序返回(MRET)用于从正在机器模式中执行的Trap处理程序返回。

一旦trap服务和保存的上下文被恢复。可以调用mret指令。

这条指令基本上是告诉处理器将控制权传递回mepc寄存器中的地址。来自较低特权级别的异常。MRET指令将控制转移到该特权级别。状态寄存器的MPP字段将被引用,以确定返回到哪个模式(m, s,或u)。返回将通过将保存的程序计数器从mepc复制到程序计数器(pc)来实现。

Exception Registers

mie、mstatus、mepc、mtvec、mcause等。参考CSR章节。

Interrupt

中断是由外部源触发的异步事件。处理器可能倾向于处理或忽略中断。中断可以是软件中断,也可以是硬件中断。在RISC-V中断中,分为定时器中断(Timer Interrupts)、软件中断(Software Interrupts)和外部中断(External Interrupts)。外部中断也称为全局中断。定时器中断在core中处理。软件中断是处理器内部(核间中断)的,外部中断由PLIC模块处理。在本章中,我们将学习如何在RISC-V中处理定时器和外部中断。

Timer Interrupts

当一个单独的定时器电路指示一个预定的间隔已经结束时,timer interrupt就会产生。将中断当前正在执行的代码。定时器中断由操作系统处理,操作系统使用它们来实现时间片多线程。

mtime Register

是一个同步计数器。它从处理器上电开始运行,并以滴答数提供当前的实时时间。

mtimecmp Register

这个寄存器用于存储计时器中断将要发生的时间。

mtimecmp的值与mtime进行比较。当mtime值大于mtimecmp时,发生定时器中断。mtime和mtimecmp寄存器都是64位内存映射寄存器。

External Interrupts

External Interrupts外部中断来自处理器外部,这种中断是异步的,由外部源通过硬件产生,由处理器处理。例如,在嵌入式过程控制系统中使用的RISC-V处理器可能会接收来自各种要求采取适当行动的传感器的外部中断。这些中断由平台级中断控制器(PLIC)处理。PLIC的中断源是连接到SoC (IO, UART, SPI等)的设备。根据RISC-V规范,这些被称为全局中断源,每个中断源被PLIC优先排序并路由到核心。

Software Interrupts

Software Interrupts软中断是由在机器状态字中设置一个位引起的。在多核芯片中,运行在一个核上的线程需要向另一个核发送中断信号。

5786

5786

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?