以前一直不能领会这俩家伙,现在特地写博客记录。

维基说:

In electronic logic circuits, a pull-up resistor or pull-down resistor

is a resistor used to ensure a known state for a signal. It is

typically used in combination with components such as switches and

transistors, which physically interrupt the connection of subsequent

components to ground or to VCC.在逻辑电路中,上拉电阻或下拉电阻是用于确保信号处于已知状态的电阻。 它通常与开关和晶体管等组件结合使用,物理阻断了一系列电路与地(GND)和电源(VCC)相连。

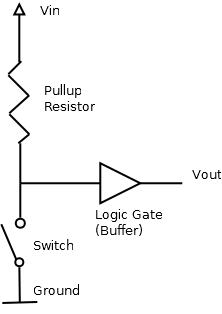

上拉电阻的使用,这里是逻辑门在开关断开的时候输入高电平

粗暴来讲,就是防止引脚悬空,让信号已知为逻辑高电平(上拉电阻)或者低电平(下拉电阻)。

但或许你会问了,为什么上面的上拉电阻一定要接这个电阻呢?我直接接电源不行吗?

其实,这个电阻的确起到了一个上拉电压的效果,也的确因这种现象为这个电阻命名为上拉电阻,但不要因为名字陷入误区,这个电阻起到的是限流的作用(这不就是电阻的本职么),保护负载,防止电流过大而烧毁负载,如果没有上面这个电阻,也有可能烧毁这个逻辑门。上拉电阻只是“接入电源,再接一个电阻”的体现而已。

下拉电阻同理,也有起到保护IC的效果。

这些电阻还有增强IO口的驱动能力的作用等。

深入一步了解可以参考这篇转载:电阻之上拉电阻与下拉电阻详解(转)

757

757

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?