10.4.3. Bank Interleaving

当控制器错过一个页面,并且该页面在不同的组中时,可以使用组交错来维持总线效率。

注意:

页面大小是指使用单个激活命令访问的任何行上的最小列位置数。

对于DDR4,存储体是指存储体地址和存储体组。

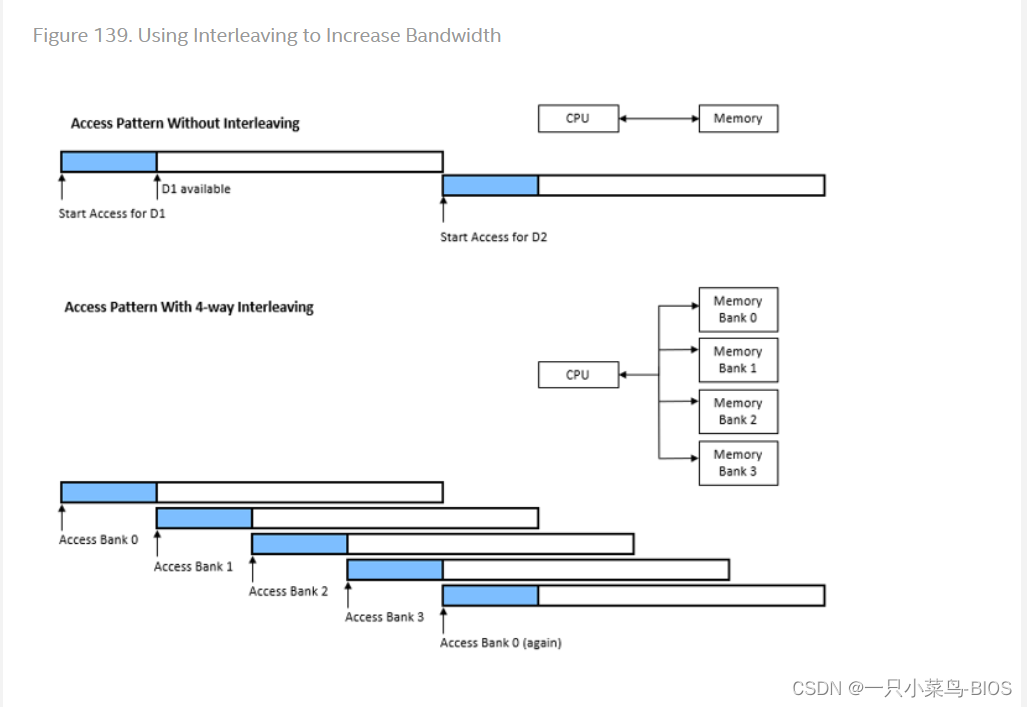

在没有交织的情况下,控制器将地址发送到SDRAM设备,接收所请求的数据,然后等待SDRAM设备预充电并在启动下一个数据事务之前重新激活,从而浪费了几个时钟周期。

交错允许SDRAM设备的组交替其后台操作和访问周期。一个存储体经历其预充电/激活周期,而另一个正在被访问。通过交替存储体,控制器通过掩蔽每个存储体的预充电/激活时间来提高其性能。如果系统中有四个存储体,则理想情况下,控制器可以在连续的时钟周期中向每个存储体发送一个数据请求。

例如,在第一个时钟周期中,CPU向存储体0发送一个地址,然后在第二个时钟周期中将下一个地址发送到存储体1,然后分别在第三个和第四个时钟周期将第三个地址发送给存储体2和3。顺序如下:

控制器将地址0发送到Bank0。

控制器向存储体1发送地址1,并从存储体0接收数据0。

控制器向存储体2发送地址2,并从存储体1接收数据1。

控制器向存储体3发送地址3,并从存储体2接收数据2。

控制器接收来自银行3的数据3。

下图显示了如何使用交织来增加带宽。

控制器支持三种交错选项:

CS BG Bank CID Row Col–这是一个非交错选项。选择此选项可提高随机流量的效率

CS CID Row Col Bank BG–此选项使用不带芯片选择交错的组交错。选择此选项可以通过在芯片中的所有库中分布较小的数据结构来提高顺序流量的效率。

CID行CS bank列BG–此选项使用带芯片选择交错的银行交错。选择此选项可提高顺序流量和多芯片选择的效率。此选项允许较小的数据结构分布在多个银行和芯片上。

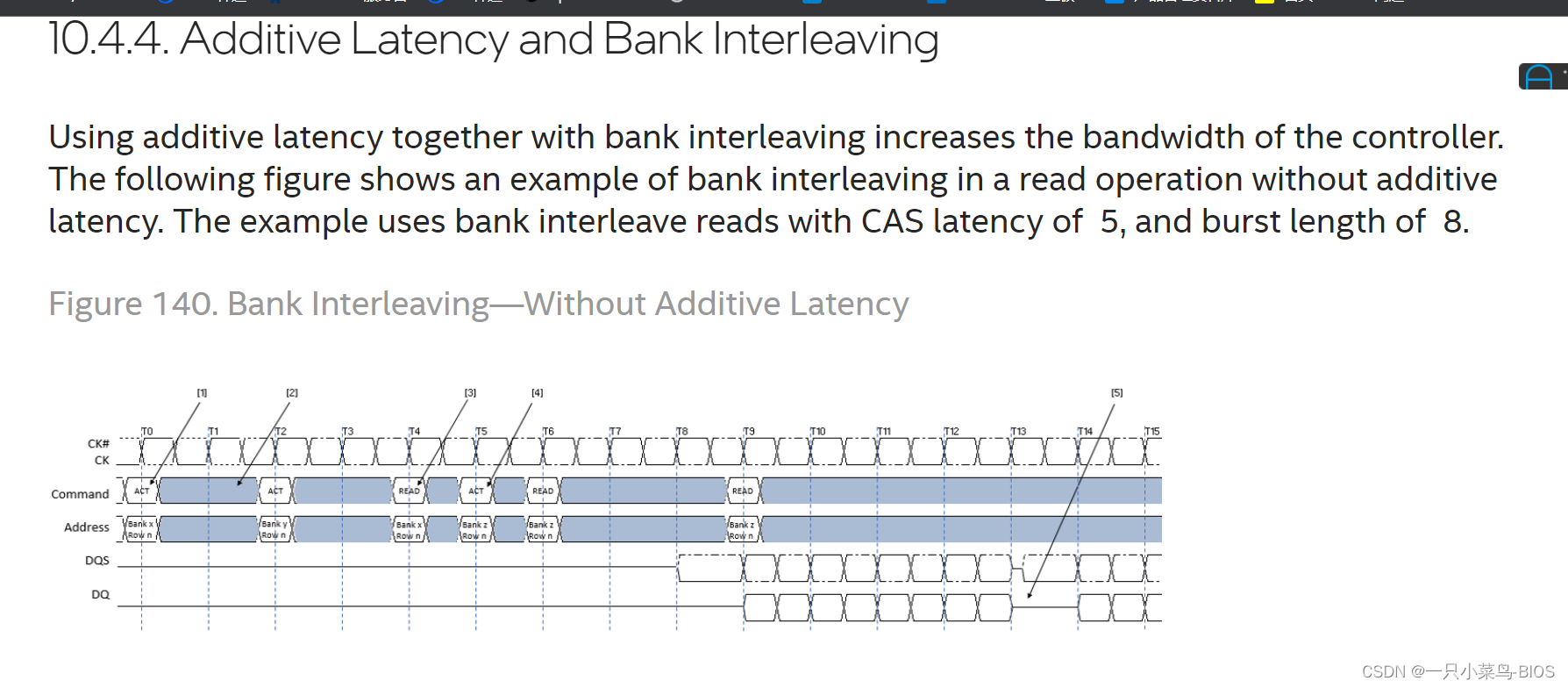

bank交错是一种固定的数据事务模式,实现了最佳情况下的带宽和延迟,并允许开户银行之间有足够的交错事务来完全隐藏tRC。对于具有8个银行的银行交错交易,最优系统可以实现100%的效率。一个少于8家银行的系统不太可能实现100%。

注意:增加延迟可以提高背靠背交错读取或写入的效率,但不能提高单独的随机读取或写入。

控制器随后在上升沿T4上执行带自动预充电命令tRCD time的读取。

控制器发出激活命令打开BANK,激活bankx及其所在行。

tRCD时间过后,控制器向指定银行发出read with auto precharge命令。

banky在tRRD时间后收到激活命令。

控制器无法在其最佳位置向气缸组z发出激活命令,因为它必须等待气缸组x接收带有自动预充电命令的读取,从而将激活命令延迟一个时钟周期。

激活命令延迟导致存储设备的输出数据出现间隙。

1027

1027

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?