随机访问存储器(Random-Access Memory, RAM)分为两类: 静态的和动态的

静态RAM(SRAM)比动态RAM(DRAM)更快

SRAM用来作为高速缓存存储器, 既可以在CPU芯片上, 也可以在片下

DRAM用来作为主存以及图形系统的帧缓冲区

1.静态RAM

SRAM将每个位存储在一个双稳态的(bistable)存储器单元里。每个单元是用一个六晶体管电路来实现的。这个电路有这样一个属性, 它可以无限期地保持在两个不同的电压配置(configuration)或状态( state)之一。

也就是只要通电,它的值会永远保持。

2、动态RAM

DRAM每个单元由一个电容和一个访问晶体管组成,它将每个位存储为对一个电容的充电,但是DRAM易受干扰而漏电,内存系统必须周期性地通过读出, 然后重写来刷新内存每一位,保证数据不改变。

SRAM和DRAM对比

只要有供电, SRAM就会保持不变。与DRAM不同, 它不需要刷新。SRAM的存取比DRAM快。SRAM对诸如光和电噪声

这样的干扰不敏感。代价是SRAM单元比DRAM单元使用更多的晶体管, 因而密集度低, 而且更贵, 功耗更大。

1.DRAM芯片

1.位的组织

DRAM中的位,被以w为一组,分成了d个组,每个组都被称为一个supercell(书中翻译为超单元)。这d个组被组织成一个r*c的矩阵。在这个矩阵中,每个超单元都有一个坐标一样的地址(i,j),如下图所示。

此图展示的是一个16X8的DRAM芯片的组织, 有d = 16个超单元, 每个超单元有w = 8位,r =4行,c= 4列。带阴影的方框表示地址(2, 1)处的超单元。

2. 信息的传输

信息通过称为引脚(pin)的外部连接器流入和流出芯片。每个引脚携带一个1位的信号。上图中给出了两组引脚: 8个data引脚, 它们能传送一个字节到芯片或从芯片传出一个字节(8位), 以及2个addr引脚, 它们携带2位的行和列超单元地址。其他携带控制信息的引脚没有显示出来。

3.内存控制器

DRAM芯片被连接内存控制器,它可以一次传送w位到每个DRAM芯片或一次从每个DRAM芯片传出w位。在读取DRAM芯片信息时,控制器先发送i,再发送j

4.读取流程

DRAM 中读出超单元( 2, 1), 内存控制器发送行地址2, DRAM 的响应是将行2 的整个内容都复制到一个内部行缓冲区。接下来, 内存控制器发送列地址1,DRAM 的响应是从行缓冲区复制出超单元(2, 1)中的8 位, 并把它们发送到内存控制器。

行地址1称为RAS(Row A ccess Strobe, 行访问选通脉冲)请求。列地址]称为CAS(Column Access Strobe, 列访问选通脉冲)请求。

2.内存模块

内存模块的基本思想如下图所示。

1.数据存储

示例模块用8 个64 Mbit的8MX8 DRAM

芯片,总共存储64MB(兆字节),这8 个芯片编号为0~7。每个芯片只存储主存的一个字节,而用相应超单元地址为(i,j)的8 个超单元来表示主存中字节地址A 处的64 位字。

示例图中, DRAM0 存储第一个(低位)字节, DRAM1 存储下一个字节, 依此类推。

2.数据取出

要取出内存地址A 处的一个字, 内存控制器将A 转换成一个超单元地址(i,j)并将它发送到内存模块, 然后内存模块再将i和j广播到每个DRAM。作为响应,每个DRAM 输出它的(i,j)超单元的8位内容。模块中的电路收集这些输出, 并把它们合并成一个64 位字, 再返回给内存控制器。

通过将多个内存模块连接到内存控制器, 能够聚合成主存。在这种情况中, 当控制器收到一个地址A 时, 控制器选择包含A 的模块k,将A 转换成它的(i,j)的形式,并将(i,j)发送到模块k。

3.增强的DRAM

1.快页模式 DRAM (FPM DRAM)

- 传统的DRAM

将超单元的一整行复制到它的内部行缓冲区中, 使用一个, 然后丢弃剩余的。 - FPM DRAM

允许对同一行连续地访问可以直接从行缓冲区得到服务。

例如, 要从一个传统的DRAM的行1中读4个超单元, 内存控制器必须发送4个RAS/CAS请求, 即使是行地址i在每个情况中都是一样的。要从一个FPM DRAM的同一行中读取超单元, 内存控制器发送第一个RAS/CAS请求, 后面跟三个CAS请求。初始的RAS/CAS请求将行i复制到行缓冲区, 并返回CAS寻址的那个超单元。接下来三个超单元直接从行缓冲区获得, 因此返回得比初始的超单元更快。

2. 扩展数据输出DRAM

FPMDRAM的一个增强的形式, 它允许各个CAS信号在时间上靠得更紧密一点。

3.同步DRAM、双倍同步DRAM

速度上更快了,其中双倍同步DRAM(DDR DRAM)是同步DRAM的优化,比他快一倍。

3、非易失性存储器

如果断电,DRAM 和SRAM 会丢失它们的信息,非易失性存储器即使是在关电后,仍然保存着它们的信息。现在有很多种非易失性存储器。由于历史原因,虽然ROM中有的类型既可以读也可以写, 但是它们整体上都被称为只读存储器( Read-Only Memory, ROM) 。

ROM 是以它们能够被重编程(写)的次数和对它们进行重编程所用的机制来区分的。

1. PROM(Programmable ROM, 可编程ROM)

只能被编程一次。PROM 的每个存储器单元有一种熔丝(fuse), 只能用高电流熔断一次。

2.可擦写可编程ROM(Erasable Programmable ROM, EPROM)

EPROM 能够被擦除和重编程的次数的数矗级可以达到1000 次。

3.电子可擦除PROM(Electrically ErasablePROM, EEPROM)

类似于EPROM, 但是它不需要一个物理上独立的编程设备, 因此可

以直接在印制电路卡上编程。

EEPROM 能够被编程的次数的数量级可以达到

1

0

5

10^5

105 次。

4. 闪存(flash memory)

是一类非易失性存储器, 基于EEPROM,一种新型的基于闪存的磁盘驱动器, 称为固态硬盘(Solid State Disk, SSD), 它能提供相对于传统旋转磁盘的一种更快速、更强健和更低能耗的选择。

5.固件

存储在ROM 设备中的程序通常被称为固件(firmware)。当一个计算机系统通电以后,它会运行存储在ROM 中的固件。

4. 访问主存

首先我们明确我们讨论的结构

主要部件是CPU 芯片、我们将称为I/O桥接器的芯片组(其中包括内存控制器),以及组成主存的DRAM 内存模块。

这些部件由一对总线连接起来, 其中一条总线是系统总线(system bus), 它连接CPU 和I/O桥接器, 另一条总线是内存总线(memory bus), 它连接I/O桥接器和主存。I/O桥也将系统总线和内存总线连接到I/O总线, 像磁盘和图形卡这样的I/O设备共享I/O总线。

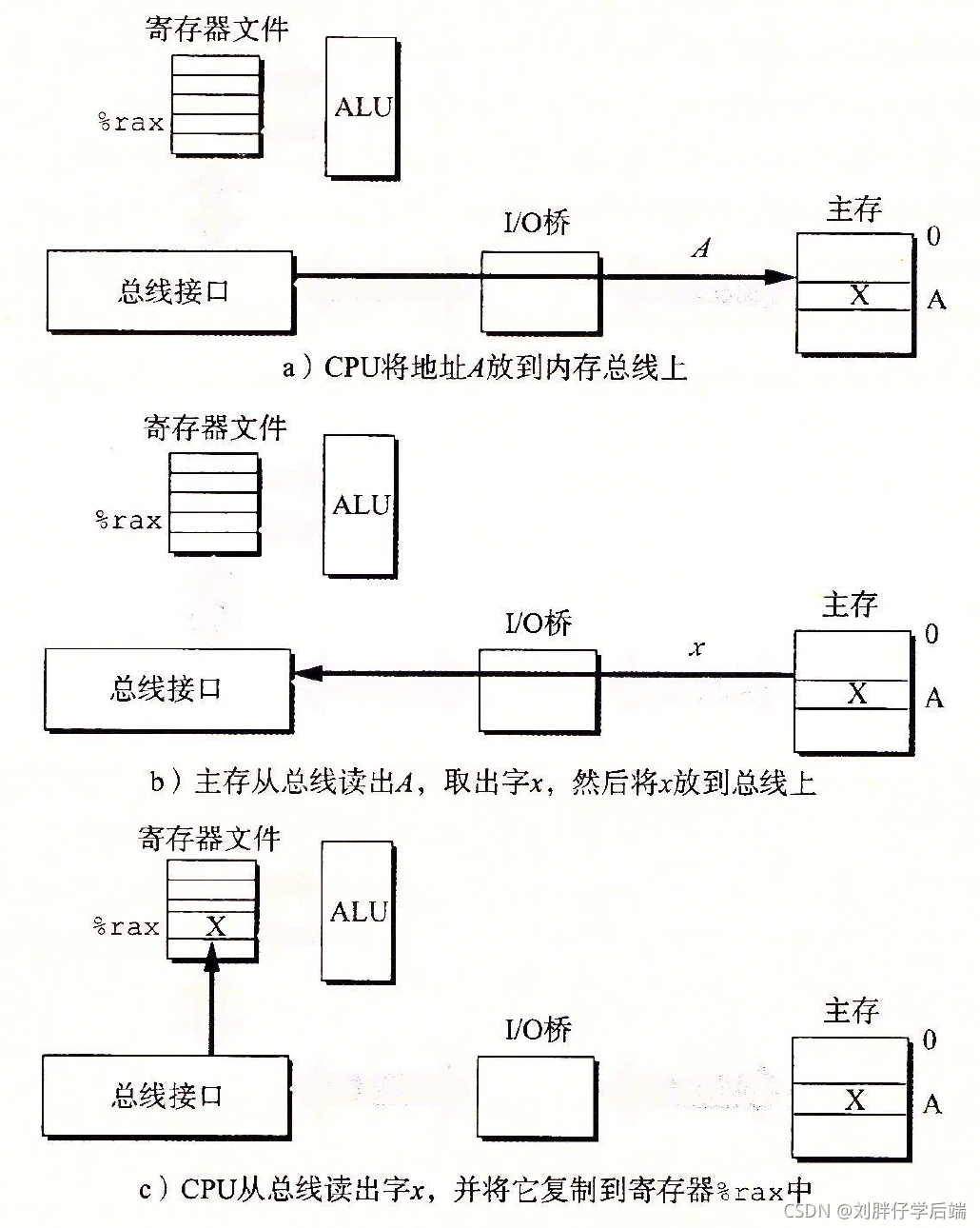

1.读取事务

考虑当CPU 执行一个如下加载操作时会发生什么

movq A,%rax 这里,地址A 的内容被加载到寄存器% rax 中。

读事务是由以下步骤组成的。

- 首先,CPU 将地址A 放到系统总线上。I/O桥将信号传递到内存总线。

- 接下来,主存感觉到内存总线上的地址信号,从内存总线读地址,从DRAM 取出数据字,并将数据写到内存总线。

- I/O 桥将内存总线信号翻译成系统总线信号,然后沿着系统总线传递

- 最后,CPU 感觉到系统总线上的数据,从总线上读数据,并将数据复制到寄存器%rax

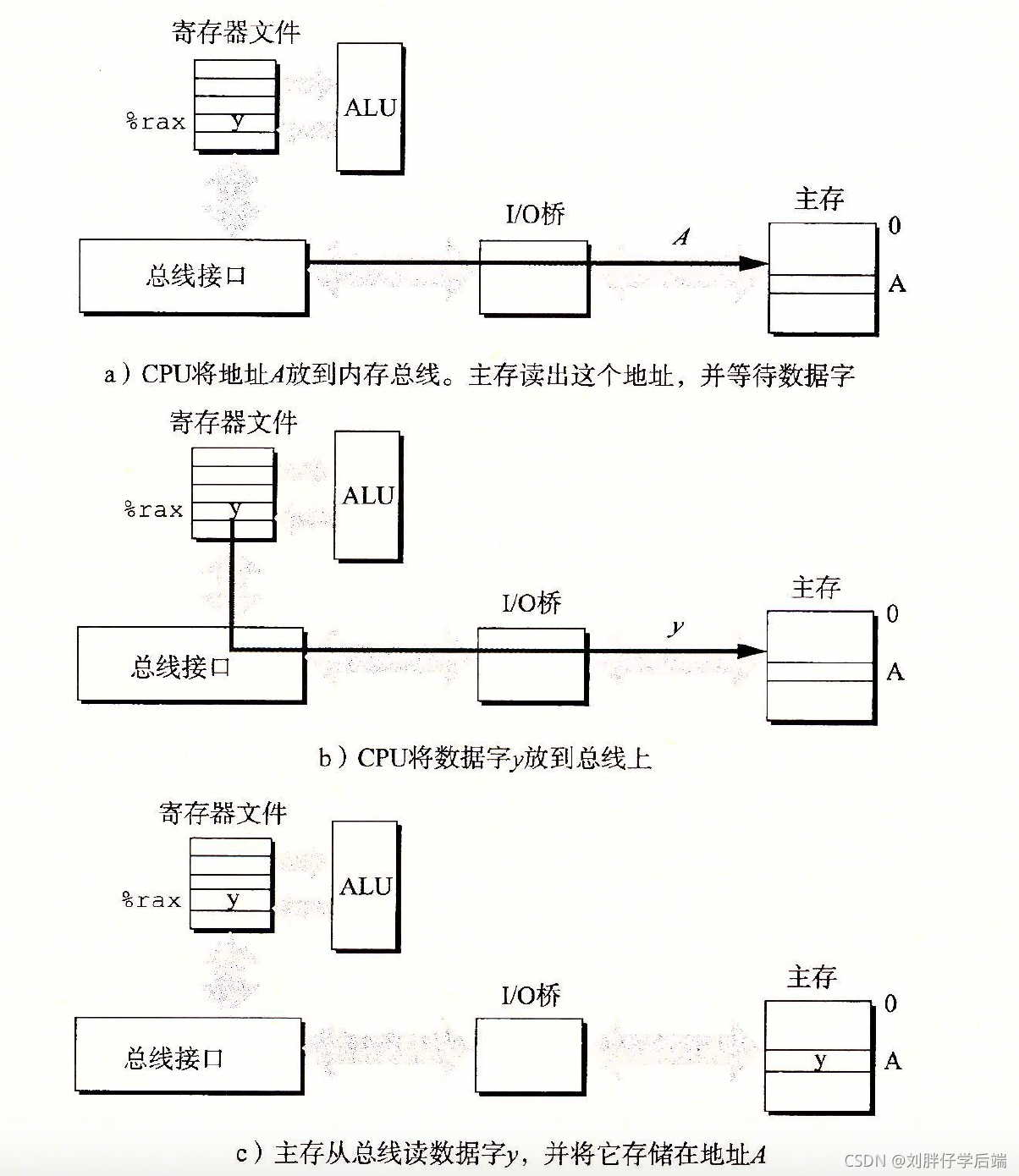

2.写事务

同样,有三个基本步骤。

- 首先,CPU 将地址放到系统总线上。内存从内存总线读出地址,并等待数据到达

- 接下来,CPU 将%rax中的数据字复制到系统总线

- 最后,主存从内存总线读出数字,并且将这些位存储到DRAM 中

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?