ADS1191心电采集系统设计方案

一、硬件电路设计

(一)、ADS1191的电源和地

ADS1191支持两种电源模式:单电源模式和双电源模式(芯片手册53页)。具体区别应该也是对芯片内部集成运放工作的区别。两种电源模式的优缺点待补……。(参考电路采用的是单电源模式,模仿为上)

单电源模式框图👇:

使用立创EDA画出的阶段性原理图👇:

(二)、ADS1191的时钟电路

ADS1191提供两种不同的设备时钟方法:内部时钟振荡器和外部时钟。内部时钟非常适合低功耗、电池供电的系统。

时钟选择由CLKSEL引脚和CLK_EN寄存器位控制。

在使用 外部时钟 时,将CLKSEL引脚拉低,外部时钟从CLK引脚输入。

在使用 内部时钟振荡器 时,将CLKSEL引脚拉高。此时若寄存器中时钟使能位CLK_EN为1,则在CLK引脚输出内部时钟;若时钟使能位CLK_EN为0,则CLK引脚为3-state(不定态?高阻态?)。

对于CLK引脚时钟输出作用的猜测:SPI多从机有两种实现方法:多NSS和菊花链。多NSS方式中,各个从机可以由主机统一提供时钟信号。而在菊花链方式中,使用每个从机的CLK引脚进行对外时钟输出,来为下一个从机提供时钟信号,更符合菊花链式的特点。

在此,只有一个从机ADS1191,所以采用内部时钟(将CLKSEL引脚拉高),并编程将寄存器中时钟使能位CLK_EN置为0。

采用内部时钟(将CLKSEL引脚拉高)的具体操作为,将CLKSEL引脚通过10k电阻上拉至数字VDD。由上表可知,在此时钟模式下,CLK引脚为3-state,引脚电平状态不能确定,因此参考其他设计,将CLK引脚经过10k电阻下拉为低电平。

(三)、ADS1191的SPI相关引脚配置

基本SPI引脚

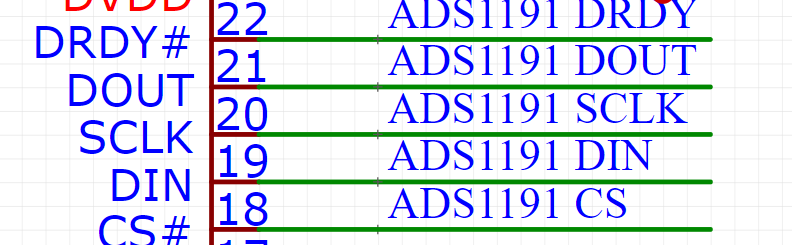

ADS1191原理图上的基本SPI引脚有四个:CS#、SCLK、DIN和DOUT。

分别对应于传统SPI协议里的SS、SCLK、MOSI、MISO。

MISO: Master input slave output 主机输入,从机输出(数据来自从机);

MOSI: Master output slave input 主机输出,从机输入(数据来自主机);

SCLK :Serial Clock 串行时钟信号,由主机产生发送给从机;

SS: Slave Select 片选信号,由主机发送,以控制与哪个从机通信,通常是低电平有效信号。

拓展SPI引脚

DRDY#引脚是一个数字输出引脚。当它变低时,指示新的转换数据准备好了。

原理图采用网络标号,方便与单片机相连。

(四)、ADS1191的GPIO相关引脚配置

GPIO即General-purpose input/output。按照芯片手册上所说,类似于MCU的普通引脚,即可以通过编程实现输出高低电平,或者读取引脚的外部电平状态。不使用时,需要下拉至数字地。

(五)、PWDN#/RESET#引脚

PWDN#/RESET# 引脚可以理解为硬件复位引脚,低电平有效。ADS1191还可以通过软件复位,因此将该引脚上拉至DVDD。

(六)、START开始转换引脚

与复位引脚类似可以通过软件复位,并且软件复位更加灵活。高电平有效,因此将该引脚下拉至数字地。

软件SPI编程测试

时序图:

#define CS P10

#define SCLK P11

#define MOSI P12

#define MISO P13

unsigned char SPI_Byte(unsigned char SendByte)

{

unsigned char i,RecByte = 0x00;

CS = 0; //拉低片选,开始SPI数据传输

SCLK = 0; //SCLK空闲状态为低电平

for(i=8;i>0;i--)

{

SCLK = 0;

Delay10us(); //延时一会维持低电平,保证一定的周期

RecByte <<= 1; //数据接收时最高位在前

if(MISO)

RecByte |= 0x01;

SCLK = 1;

if((SendByte&0x80) == 0x80) MOSI = 1; //数据发送时最高位在前

else MOSI = 0;

SendByte <<= 1;

Delay10us(); //延时一会维持高电平,保证一定的周期

SCLK = 0;

}

return RecByte;

}

发送字节SendByte=0xAA时,SCLK和MOSI的波形:

发送字节SendByte=0x4C时,SCLK和MOSI的波形:

2万+

2万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?