裸机配置硬件SPI

详细的SPI时序介绍可看我的另外一篇文章:STM32之SPI详细解析

ESPI介绍

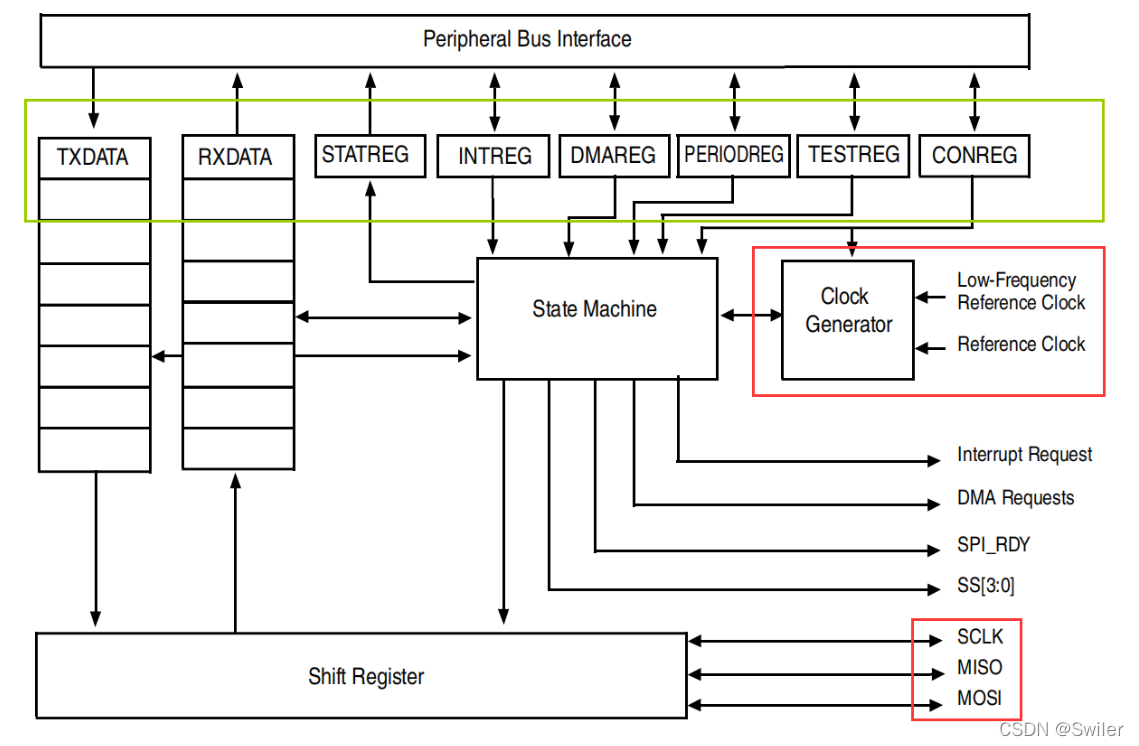

IMX6U 自带的 SPI 外设叫做 ECSPI,全称是 Enhanced Configurable Serial Peripheral Interface,ECSPI包含一个64x32接收缓冲区(RXFIFO)和一个64x32传输缓冲区(TXFIFO)。通过数据FIFOs,ECSPI允许以更少的软件中断快速进行数据通信。IMX6U有4个ESPI。下图是ECSPI的框图。由一堆寄存器,时钟产生器,外部引脚,一个状态机组成。

特性如下:

①全双工同步串行接口。

②可配置的主/从模式。

③四个片选信号,支持多从机。

④发送和接收都有一个 32x64 的 FIFO。

⑤片选信号 SS/CS,时钟信号 SCLK 极性可配置。

⑥支持 DMA。

支持的模式有3种:

①主机模式

②从机模式

③低功耗模式

外部引脚

和通常的SPI一样,都有MOSI、MISO、CLK、CS引脚,但是ESPI的硬件片选引脚支持4个外部设备片选。(可使用软件配置引脚替代硬件片选引脚。)

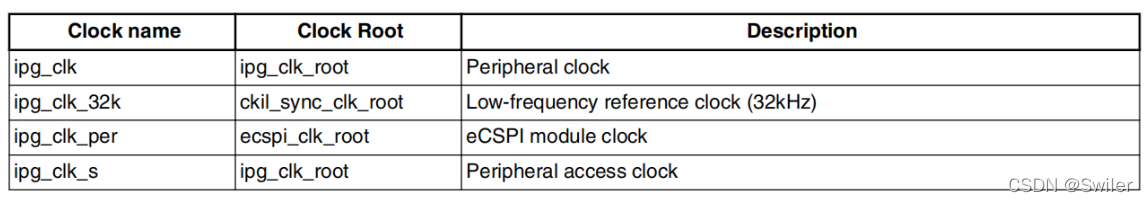

时钟

ESPI的时钟源有4个选项:

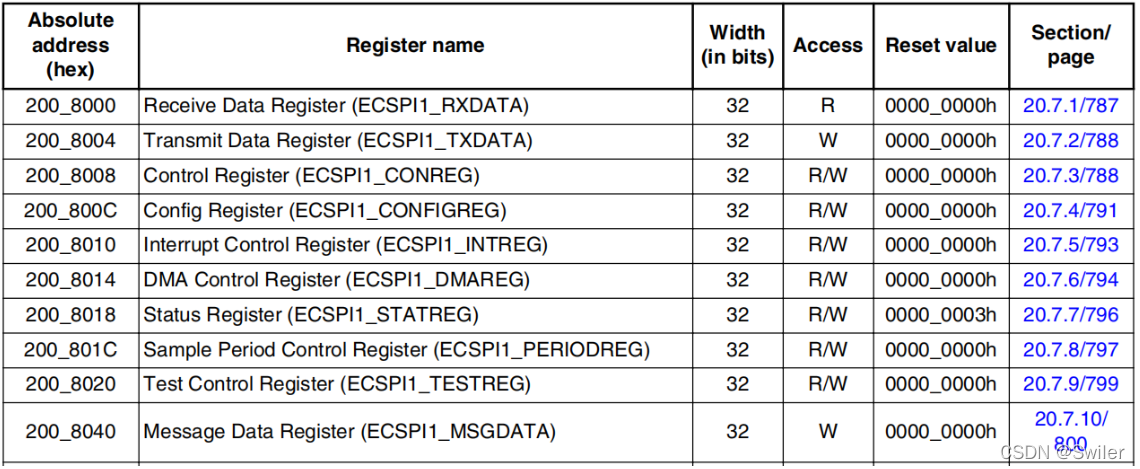

寄存器

每组SPI都有如下的寄存器组。包括:数据接收寄存器、数据发送寄存器、控制寄存器、配置寄存器、中断寄存器、DMA寄存器、状态寄存器、采样周期控制寄存器、测试控制寄存器、消息数据寄存器。

ECSPIx_RXDATA:数据接收寄存器;由于ECSPI的数据接收块是一个64*32的FIFO块,所以数据接收寄存器又在这个块内作为头部。

ECSPIx_TXDATA:数据发送寄存器;同理ECSPIx_RXDATA,它是数据发送块的头部。

ECSPIx_CONREG:控制寄存器,用来使能SPI,配置工作模式等。

[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-1vEIRyDW-1650546158115)(C:\Users\15894\AppData\Roaming\Typora\typora-user-images\image-20220421201406035.png)]

- BURST_LENGTH段:突发长度,即配置SPI的突发传输数据长度,最大可达2^12bit,一般配置为8bit

- CHANNEL_SELECT段:SPI通道选择

- DRCTL段:配置准备信号。0:不关心,1:边沿触发,2:电平触发

- PRE_DIVIDER段:配置SPI时钟预分频

- POST_DIVIDER段:配置SPI时钟分频

- CHANNEL_MODE:SPI通断模式选择,1:主模式,0:从模式

- SMC:开始模式控制

- XCH:配置是否开启SPI突发访问

- EN:SPI使能位,1使能,0关闭

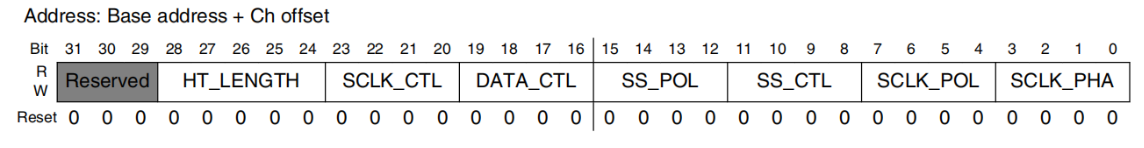

ECSPIx_CONFIGREG:配置寄存器,配置SPI相关的一些参数

-

SCLK_CTL:配置SCLK信号的空闲状态电平,4个位,分别对应4个通道,0:低电平,1:高电平

-

DATA_CTL:配置数据线空闲状态电平,4个位,分别对应4个通道,0:低电平,1:高电平

-

SS_POL:配置片选信号极性,4个位,分别对应4个通道,0:低电平有效,1:高电平有效

-

SCLK_POL:配置SPI时钟极性

-

SCLK_PHA:配置SPI时钟相位

ECSPIx_INTREG:中断控制寄存器,一共有8个中断

ECSPIx_DMAREG:DMA控制

本文围绕裸机配置硬件SPI展开,介绍了IMX6U自带的ESPI,包括其特性、支持模式、外部引脚、时钟源等。详细说明了每组SPI的寄存器组,如数据接收、发送寄存器等。还阐述了SPI主机模式的一次通信流程,并对相关代码的C文件和H文件进行分析。

本文围绕裸机配置硬件SPI展开,介绍了IMX6U自带的ESPI,包括其特性、支持模式、外部引脚、时钟源等。详细说明了每组SPI的寄存器组,如数据接收、发送寄存器等。还阐述了SPI主机模式的一次通信流程,并对相关代码的C文件和H文件进行分析。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1089

1089

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?