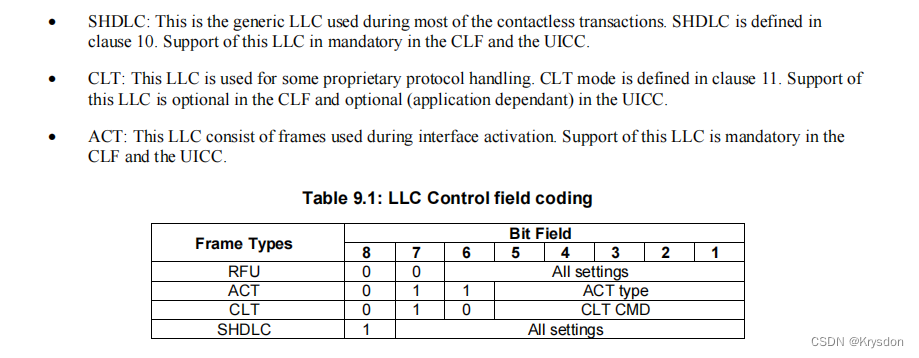

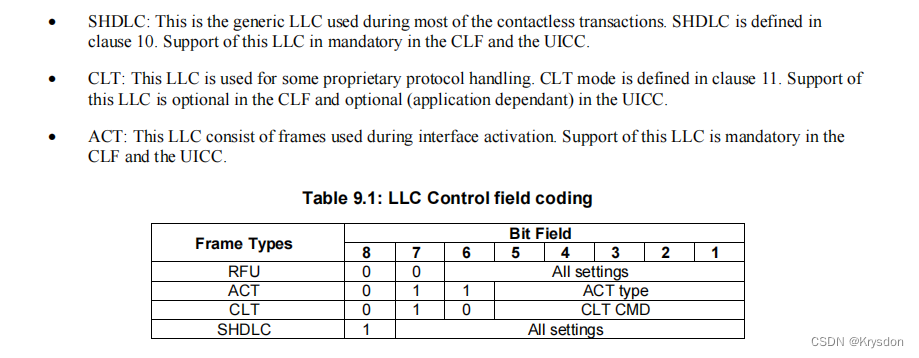

一、数据帧类型

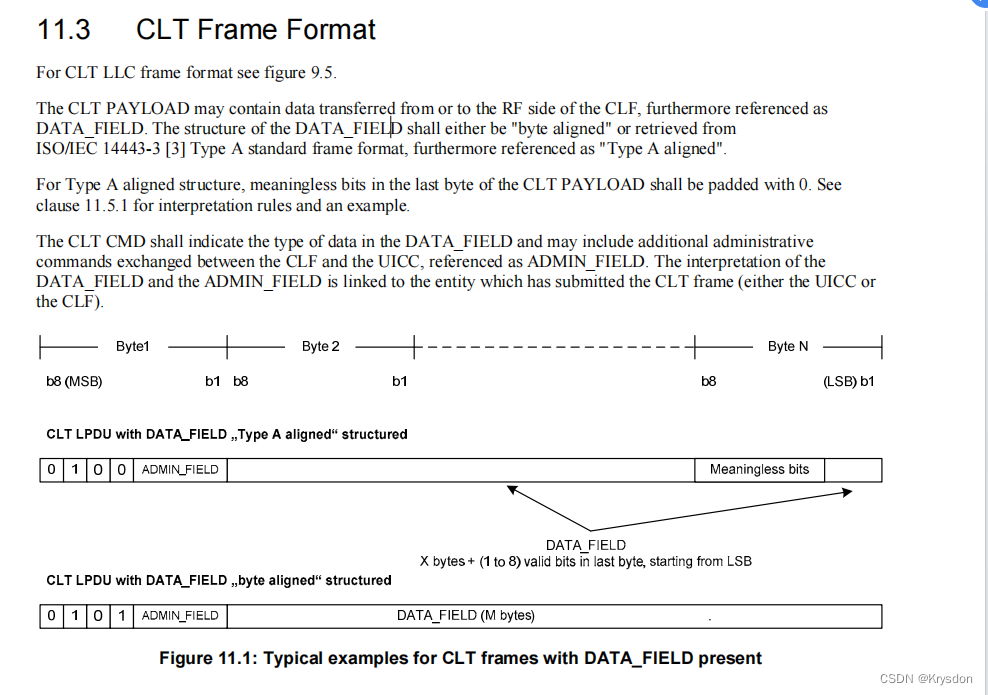

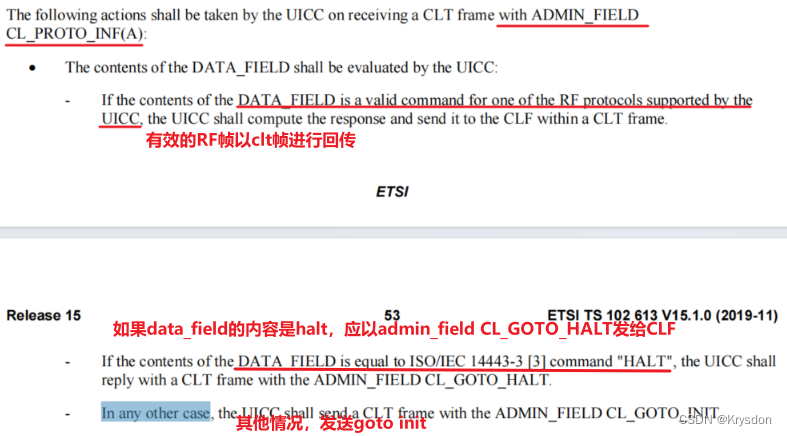

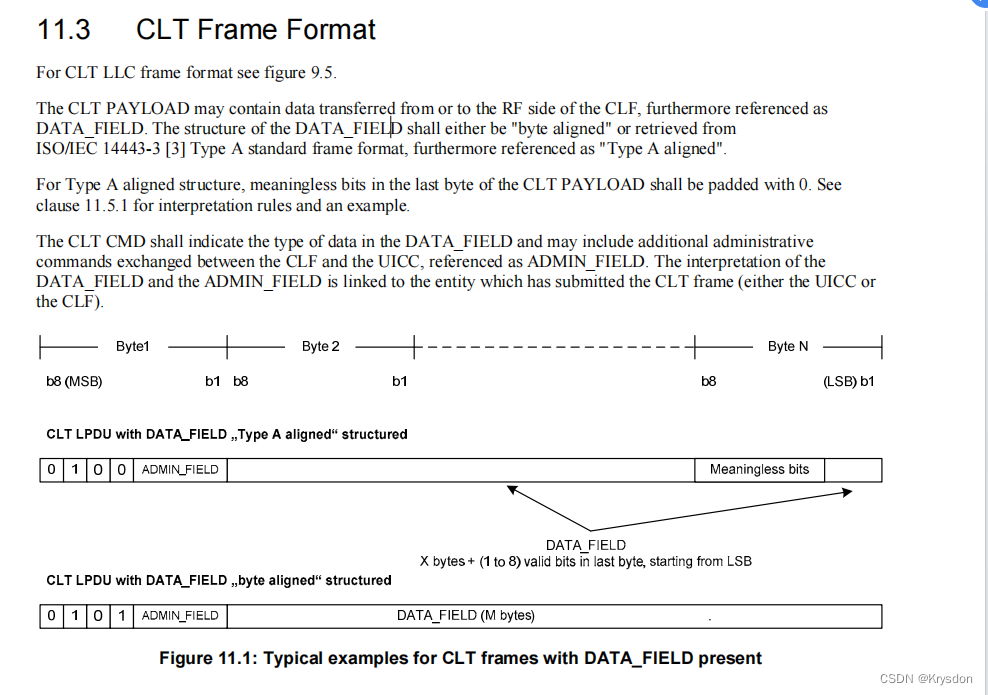

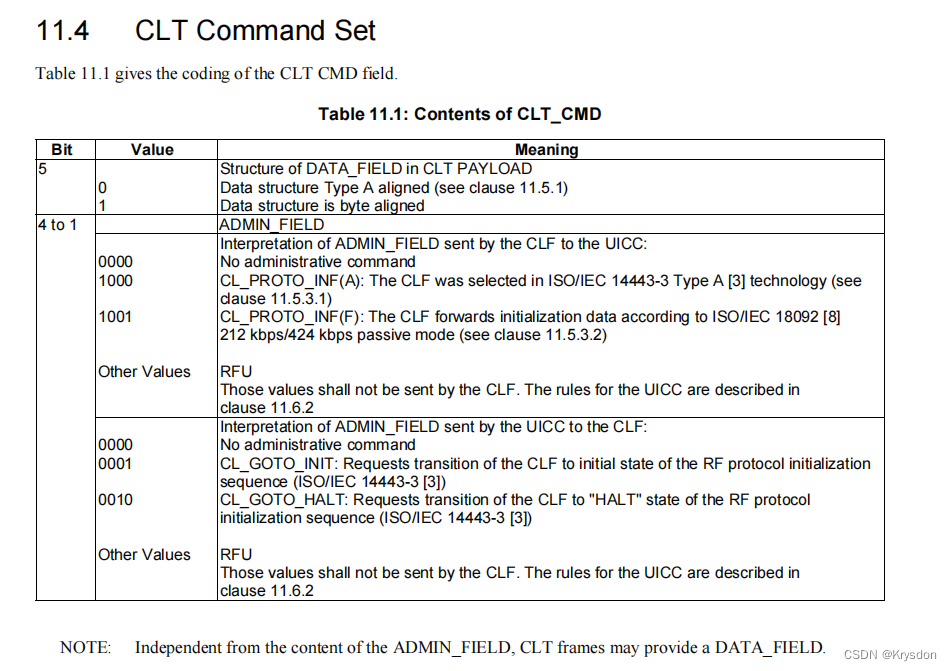

二、CLT帧

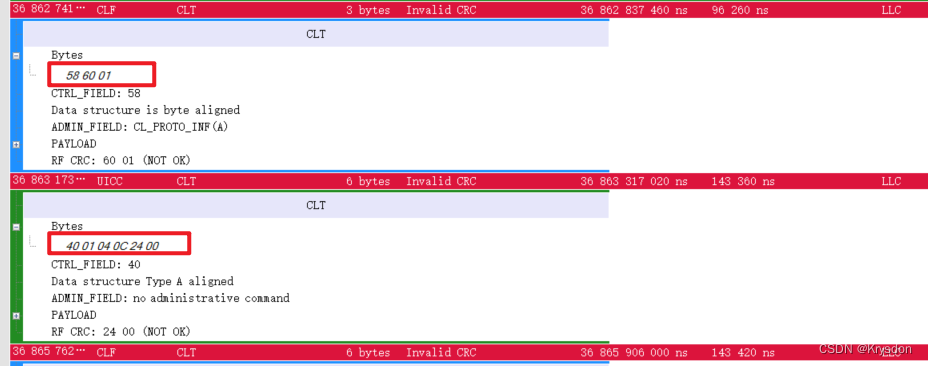

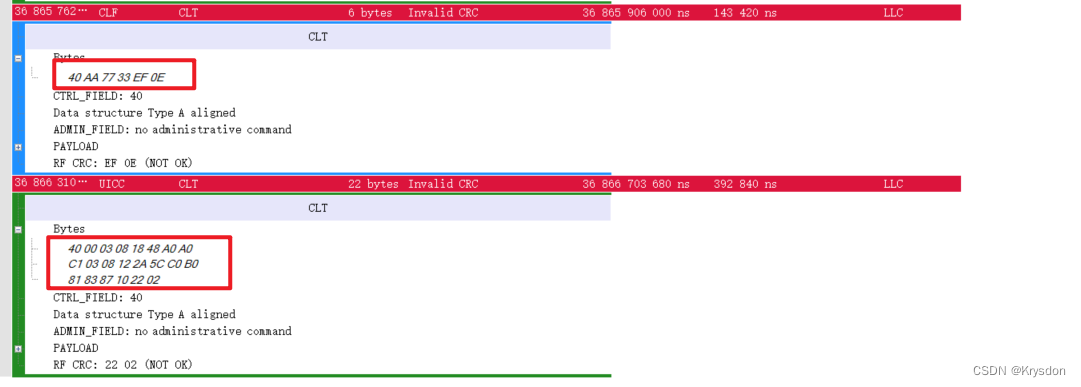

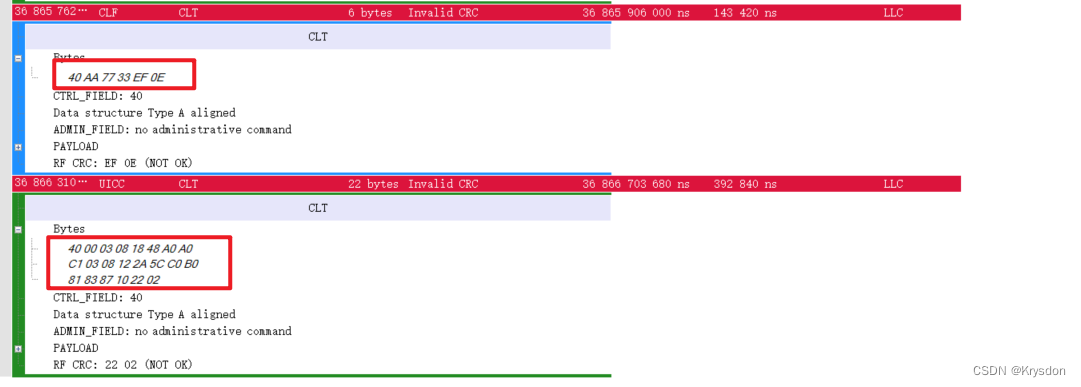

40:type A对齐

40:type A对齐

50:字节对齐

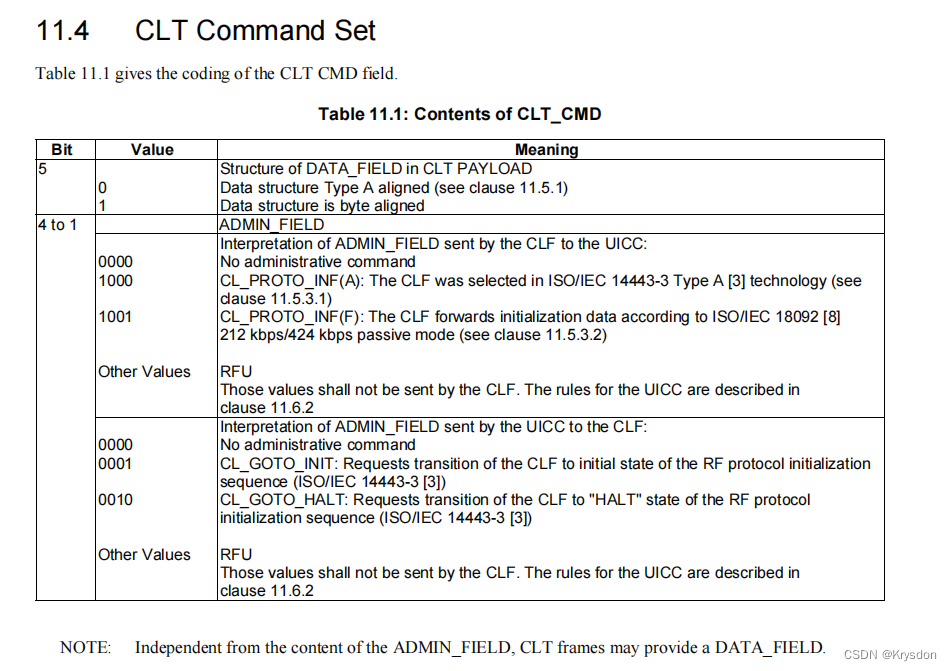

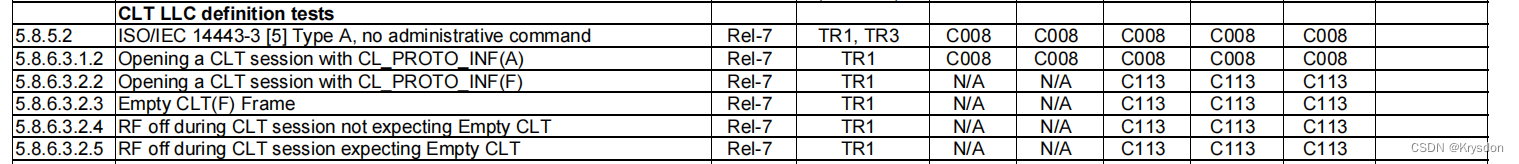

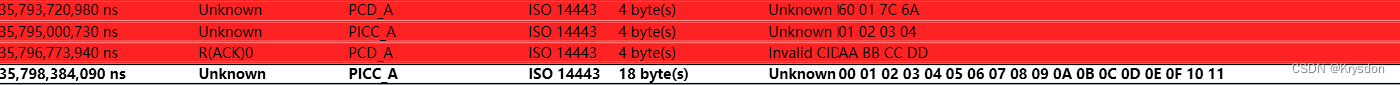

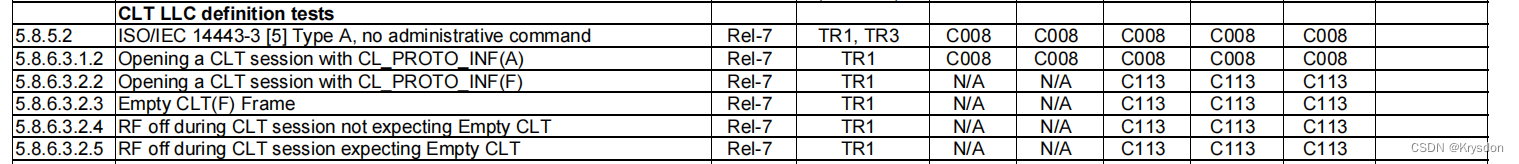

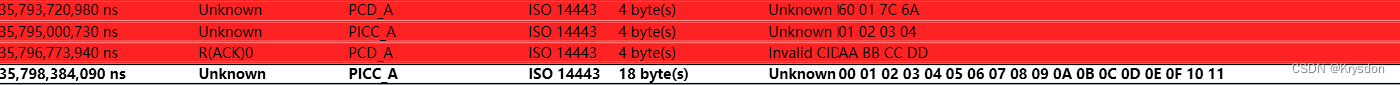

测试对应case

case:5852

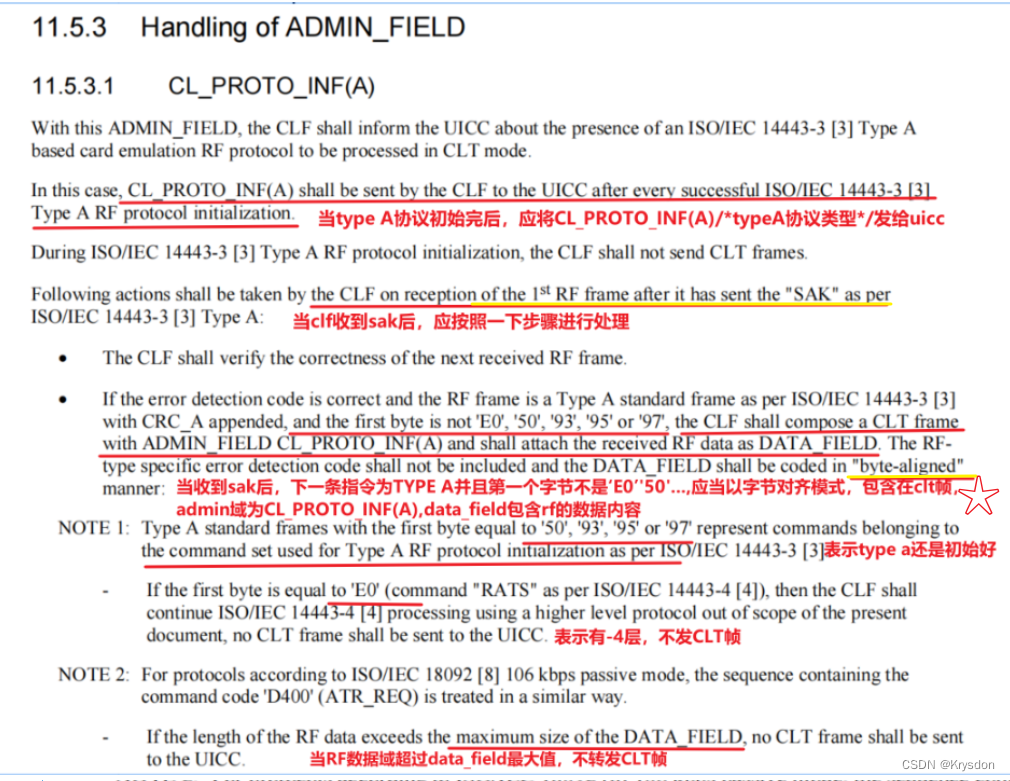

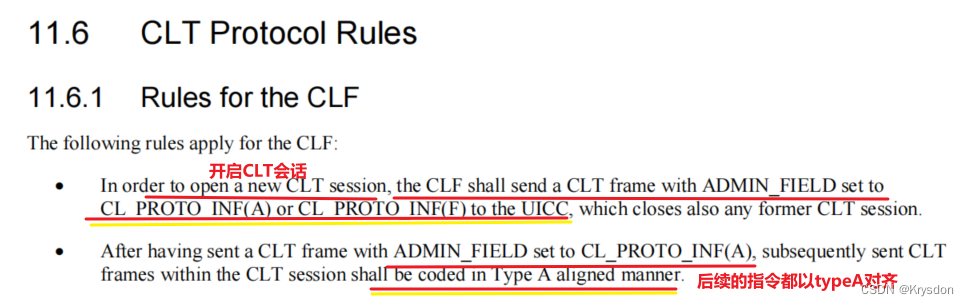

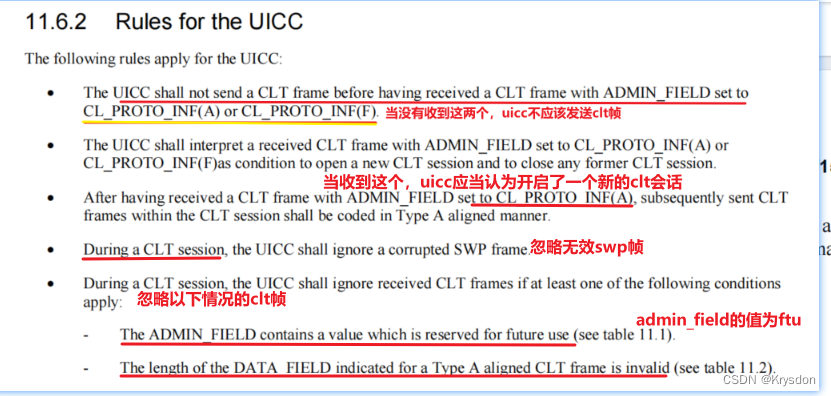

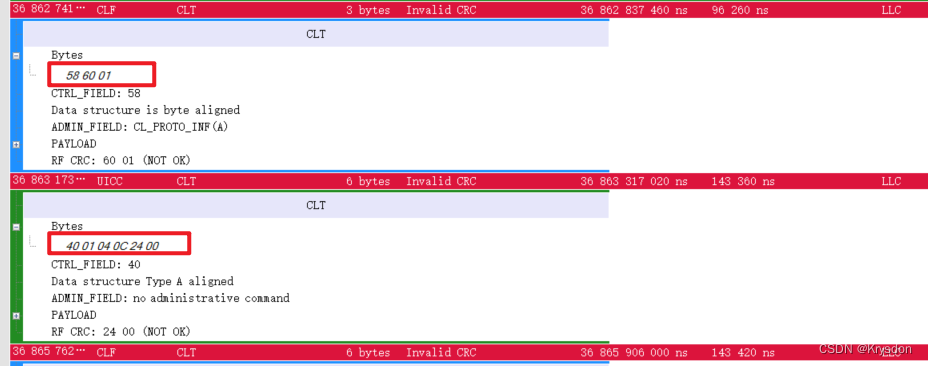

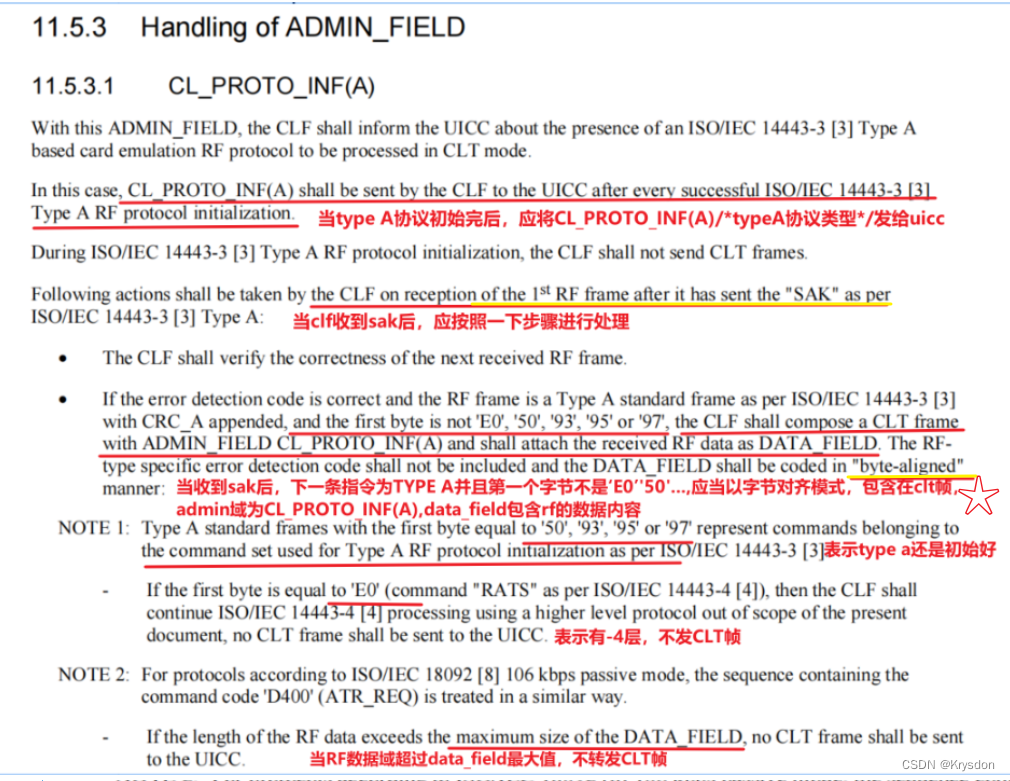

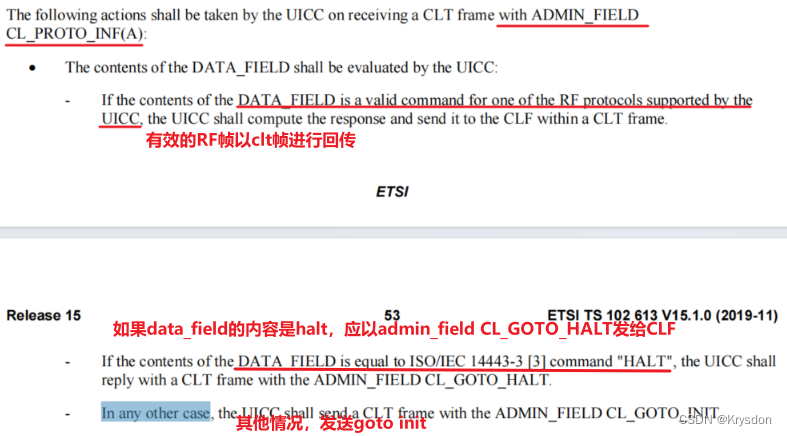

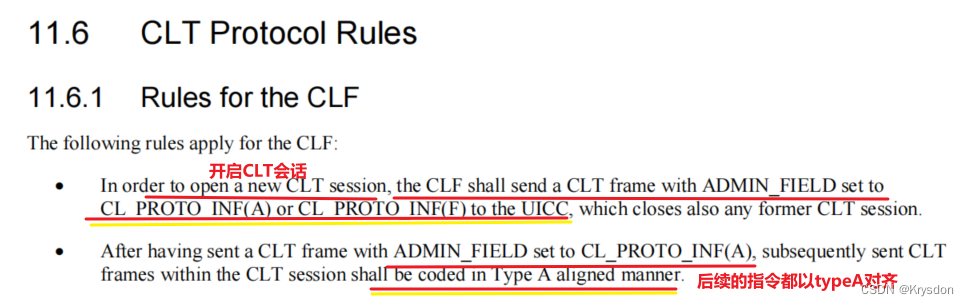

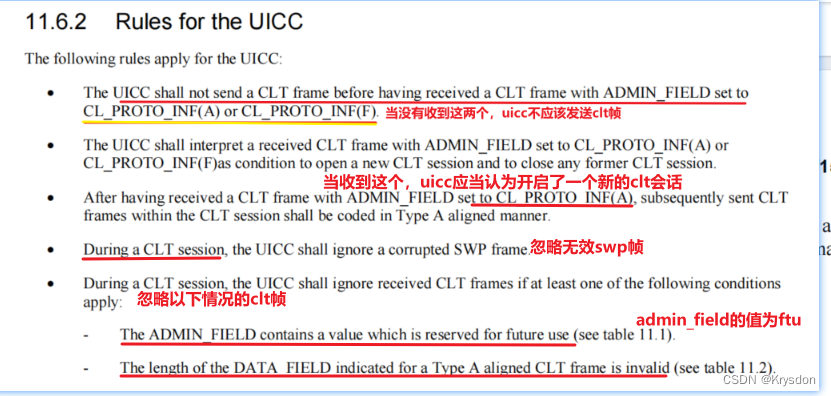

mifare指令,sak后 第一帧发送CL_PROTO_INF(A),并以byte aligned格式发送给UICC开启CLT会话,后续的以typeA aligned格式对齐发送给UICC。

一、数据帧类型

二、CLT帧

40:type A对齐

40:type A对齐

50:字节对齐

测试对应case

case:5852

mifare指令,sak后 第一帧发送CL_PROTO_INF(A),并以byte aligned格式发送给UICC开启CLT会话,后续的以typeA aligned格式对齐发送给UICC。

1056

1056

952

952

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?