简易计时闹钟设计verilog语言实现

任务描述:

用电路或verilog语言实现以下功能

简易计时闹钟:

有四位数码管,前两位计分钟,表示00~99分钟, 后面两位记秒,值为00~59秒。

有三个按键,第一个是分键,第 二个是秒键,第三个是启动/暂停键。

功能:

分秒两键同时按下清 零且停止计时,外于设置态,按一次分键分钟加1, 99增1变为0; 按一次秒键秒增1,59增1变为0。

此状态下按启动/暂停键开始计时,设置值为0000则为正计时,设置值为非零值则为倒计时。

正计时时,按启动/暂停键会暂停计时,再按启动/暂停键则会继 续计时。 (如果加满?清零?)

倒计时时,减到零时停止减数且发出警示蜂鸣声,直到 启动/暂停 键被按下时进入设置态且同时显示前设置值和停止发出蜂鸣声。

选择verilog语言实现。

可能用到的模块:

7位数码管;

蜂鸣器;

学习笔记:

Verilog中用:begin end 代替{ };

一个always中不可同时存在阻塞赋值和非阻塞赋值;

活的信号上升沿或者下降沿的算法:

判断其前后时钟周期的电平变化;

reg [3:0]t2_a;

reg [3:0]t2_b;

reg [3:0]t1_a;

reg [3:0]t1_b;

reg [3:0]t0_a;

reg [3:0]t0_b;

reg press_m;

reg press_s;

reg press_set;

always@(posedge clk) begin

t2_a<=reg_m;

t2_b<=t2_a;

t1_a<=reg_s;

t1_b<=t1_a;

t0_a<=reg_set;

t0_b<=t0_a;

end

always@(posedge clk) begin

if(t2_a==0&&t2_b==1)

press_m<=1;

if(t1_a==0&&t1_b==1)

press_s<=1;

if(t0_a==0&&t0_b==1)

press_set<=1;

end

消抖算法:

统计按键输入保持的时间,达到一定阈值更改值

parameter SAMPLE_TIME = 7;//类似宏定义,0.007s

reg [2:0] m_low;

reg [2:0] m_high;

reg [2:0] s_low;

reg [2:0] s_high;

reg [2:0] set_low;

reg [2:0] set_high;

always @(posedge clk)begin

if(input_m==1'b0)

m_low <= m_low + 1;

else

m_low <= 0;

if(input_s==1'b0)

s_low <= s_low + 1;

else

s_low <= 0;

if(input_set==1'b0)

set_low <= set_low + 1;

else

set_low <= 0;

if(input_m==1'b1)

m_high <= m_high + 1;

else

m_high <= 0;

if(input_s==1'b1)

s_high <= s_high + 1;

else

s_high <= 0;

if(input_set==1'b1)

set_high <= set_high + 1;

else

set_high <= 0;

end

always @(posedge clk) begin

if(m_high == SAMPLE_TIME)

reg_m<= 1;

else if(m_low == SAMPLE_TIME)

reg_m<= 0;

if(s_high == SAMPLE_TIME)

reg_s<= 1;

else if(s_low == SAMPLE_TIME)

reg_s<= 0;

if(set_high == SAMPLE_TIME)

reg_set<= 1;

else if(m_low == SAMPLE_TIME)

reg_set<= 0;

end

源程序:

`timescale 1ns / 1ps

//////////////////////////////////////////////////////////////////////////////////

// Company:

// Engineer:

//

// Create Date: 2019/11/22 18:29:54

// Design Name:

// Module Name: Clock

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//////////////////////////////////////////////////////////////////////////////////

module Clock(

input_m,

input_s,

input_set,

clk,//1000Hz 用于按键消抖

L3,

L2,

L1,

L0,

buzzer,

/////////////test

press_m,

press_s,

press_set,

reg_m,

reg_s,

reg_set,

m_low,

m_high,

s_low,

s_high,

set_low,

set_high,

Em_a,

Em_b,

Es_a,

Es_b,

Eset_a,

Eset_b,

reg_m0,

reg_m1,

reg_s0,

reg_s1,

reg_W0,

reg_W1,

reg_A0,

reg_A1,

en,

count,

sym,

z

////////test

);

///////输入转化

input input_m;

input input_s;

input input_set;

input clk;

output L3;

output L2;

output L1;

output L0;

output buzzer;

//////test

output press_m;

output press_s;

output press_set;

output reg_m;

output reg_s;

output reg_set;

output m_low;

output m_high;

output s_low;

output s_high;

output set_low;

output set_high;

output Em_a;

output Em_b;

output Es_a;

output Es_b;

output Eset_a;

output Eset_b;

output reg_m0;

output reg_m1;

output reg_s0;

output reg_s1;

output reg_W0;

output reg_W1;

output reg_A0;

output reg_A1;

output en;

output count;

output sym;

output z;

///////test

wire input_m;

wire input_s;

wire input_set;

wire clk;

// assign input_m=M;

// assign input_s=S;

// assign input_set=SET;

// assign clk=CLK;

//////////////

reg reg_m;//按键状态寄存器,

reg reg_s;

reg reg_set;

initial begin

reg_m<=0;

reg_s<=0;

reg_set<=0;

end

///////////////////////// 消抖

parameter SAMPLE_TIME = 2'b11;//类似宏定义,0.003s

reg [10:0] m_low;

reg [10:0] m_high;

reg [10:0] s_low;

reg [10:0] s_high;

reg [10:0] set_low;

reg [10:0] set_high;

initial begin

m_low<=0;

m_high<=0;

s_low<=0;

s_high<=0;

set_low<=0;

set_high<=0;

end

always @(posedge clk)begin

if(input_m==1'b0)

m_low <= m_low + 1;

else

m_low <= 0;

if(input_s==1'b0)

s_low <= s_low + 1;

else

s_low <= 0;

if(input_set==1'b0)

set_low <= set_low + 1;

else

set_low <= 0;

if(input_m==1'b1)

m_high <= m_high + 1;

else

m_high <= 0;

if(input_s==1'b1)

s_high <= s_high + 1;

else

s_high <= 0;

if(input_set==1'b1)

set_high <= set_high + 1;

else

set_high <= 0;

end

always @(posedge clk) begin

if(m_high == SAMPLE_TIME)

reg_m<= 1;

else if(m_low == SAMPLE_TIME)

reg_m<= 0;

if(s_high == SAMPLE_TIME)

reg_s<= 1;

else if(s_low == SAMPLE_TIME)

reg_s<= 0;

if(set_high == SAMPLE_TIME)

reg_set<= 1;

else if(m_low == SAMPLE_TIME)

reg_set<= 0;

end

////输出reg_x

////////捕获输入上升沿

reg Em_a;

reg Em_b;

reg Es_a;

reg Es_b;

reg Eset_a;

reg Eset_b;

reg press_m;

reg press_s;

reg press_set;

initial begin

Em_a<=0;

Em_b<=0;

Es_a<=0;

Es_b<=0;

Eset_a<=0;

Eset_b<=0;

press_m<=0;

press_s<=0;

press_set<=0;

end

always@(clk) begin

Em_a<=reg_m;

Em_b<=Em_a;

Es_a<=reg_s;

Es_b<=Es_a;

Eset_a<=reg_set;

Eset_b<=Eset_a;

end

always@(clk) begin

if(Em_a==1&&Em_b==0)

press_m<=1;

else

press_m<=0;

if(Es_a==1&&Es_b==0)

press_s<=1;

else

press_s<=0;

if(Eset_a==1&&Eset_b==0)

press_set<=1;

else

press_set<=0;

end

////////////press_x为按下,reg_x为状态

//////////功能实现

reg [3:0]reg_m1;//分显示寄存器

reg [3:0]reg_m0;

reg [3:0]reg_s1;//秒显示寄存器

reg [3:0]reg_s0;

reg [3:0]reg_W1; //分记忆寄存器

reg [3:0]reg_W0;

reg [3:0]reg_A1; //秒记忆寄存器

reg [3:0]reg_A0;

reg [1:0]z;//状态寄存器,0为外置态,1为倒计时,2为正计时

reg buzzer;//蜂鸣器使能,高电平有效

reg en;//正计时使能,用于暂停/开始

reg [9:0]count;

reg sym;

initial begin

reg_m0<=0;

reg_m1<=0;

reg_s0<=0;

reg_s1<=0;

reg_W0<=0;

reg_W1<=0;

reg_A0<=0;

reg_A1<=0;

z<=0;

buzzer<=0;

en<=0;

count<=0;

sym<=0;

end

////////////////外置态

always@(posedge clk)begin

if(reg_m==1&®_s==1)begin

z<=0;

reg_m1<=0;

reg_m0<=0;

reg_s1<=0;

reg_s0<=0;

end

end

always@(clk)begin

if(z==0)begin

if(press_m==1&&press_s==0)begin

if(reg_m0!=9)

reg_m0<=reg_m0+1;

else if(reg_m0==9&®_m1!=9)begin

reg_m0<=0;

reg_m1<=reg_m1+1;

end

else if(reg_m0==9&®_m1==9)begin

reg_m0<=0;

reg_m1<=0;

end

end

if(press_m==0&&press_s==1)begin

if(reg_s0!=9)

reg_s0<=reg_s0+1;

else if(reg_s0==9&®_s1!=5)begin

reg_s0<=0;

reg_s1<=reg_s1+1;

end

else if(reg_s0==9&®_s1==5)begin

reg_s0<=0;

reg_s1<=0;

end

end

if(reg_m==0&®_s==0&&press_set==1&®_m0==0&®_m1==0&®_s0==0&®_s1==0)begin////正计时

z<=2;

en<=1;

end

if((reg_m==0&®_s==0&&press_set==1)&&(reg_m0!=0||reg_m1!=0||reg_s0!=0||reg_s1!=0))begin倒计时

z<=1;

reg_W0<=reg_m0;

reg_W1<=reg_m1;

reg_A0<=reg_s0;

reg_A1<=reg_s1;

end

end

end

///////////////////sym=1时,获得1s

always@(posedge clk)begin

if(count!=1000)begin

count<=count+1;

sym<=0;

end

else begin

sym<=1;

count<=0;

end

end

//////////////////倒计时

always@(sym)begin

if(z==1)begin

if(sym==1)begin

if(reg_s0!=0)

reg_s0<=reg_s0-1;

else if(reg_s1!=0&®_s0==0)begin

reg_s0<=9;

reg_s1<=reg_s1-1;

end

else if(reg_s1==0&®_s0==0&®_m0!=0)begin

reg_s1<=5;

reg_s0<=9;

reg_m0=reg_m0-1;

end

else if(reg_s1==0&®_s0==0&®_m0==0&®_m1!=0)begin

reg_m1<=reg_m1-1;

reg_m0<=9;

reg_s1<=5;

reg_s0<=9;

end

end

if(reg_s1==0&®_s0==0&®_m0==0&®_m1==0)begin

buzzer<=1;

// if(press_set==1)begin

// buzzer<=0;

// z<=0;

// reg_m0<=reg_W0;

// reg_m1<=reg_W1;

// reg_s0<=reg_A0;

// reg_s1<=reg_A1;

// end

end

else begin

buzzer<=0;

end

end

end

always@( clk)begin

if(z==1)begin

if(buzzer==1)begin

if(press_set==1)begin

buzzer<=0;

z<=0;

reg_m0<=reg_W0;

reg_m1<=reg_W1;

reg_s0<=reg_A0;

reg_s1<=reg_A1;

end

end

end

end

////////////////正计时

always@(clk)begin

if(z==2)begin

if(press_set==1)begin

if(en==1)

en<=0;

else

en<=1;

end

end

end

always@(sym)begin

if(z==2)begin

////////////暂停/开始

// if(press_set==1)begin

// if(en==1)

// en<=0;

// else

// en<=1;

// end

if(en==1)begin

if(sym==1)begin

if(reg_s0!=9)

reg_s0<=reg_s0+1;

else if(reg_s0==9&®_s1!=5)begin

reg_s0<=0;

reg_s1<=reg_s1+1;

end

else if(reg_s0==9&®_s1==5&®_m0!=9)begin

reg_s0<=0;

reg_s1<=0;

reg_m0<=reg_m0+1;

end

else if(reg_s0==9&®_s1==5&®_m0==9&®_m1!=9)begin

reg_s0<=0;

reg_s1<=0;

reg_m0<=0;

reg_m1<=reg_m1+1;

end

else if(reg_s0==9&®_s1==5&®_m0==9&®_m1==9)begin

reg_s0<=0;

reg_s1<=0;

reg_m0<=0;

reg_m1<=0;

end

end

end

end

end

////////////////数码管控制模块,4-7译码器,此处设置为共阴极

reg [6:0]L3;

reg [6:0]L2;

reg [6:0]L1;

reg [6:0]L0;

always@(reg_m1)

case(reg_m1)

0:L3<=7'h7e;

1:L3<=7'h30;

2:L3<=7'h6d;

3:L3<=7'h79;

4:L3<=7'h33;

5:L3<=7'h5b;

6:L3<=7'h5f;

7:L3<=7'h70;

8:L3<=7'h7f;

9:L3<=7'h7b;

default:L3<=7'h00;

endcase

always@(reg_m0)

case(reg_m0)

0:L2<=7'h7e;

1:L2<=7'h30;

2:L2<=7'h6d;

3:L2<=7'h79;

4:L2<=7'h33;

5:L2<=7'h5b;

6:L2<=7'h5f;

7:L2<=7'h70;

8:L2<=7'h7f;

9:L2<=7'h7b;

default:L2<=7'h00;

endcase

always@(reg_s1)

case(reg_s1)

0:L1<=7'h7e;

1:L1<=7'h30;

2:L1<=7'h6d;

3:L1<=7'h79;

4:L1<=7'h33;

5:L1<=7'h5b;

6:L1<=7'h5f;

7:L1<=7'h70;

8:L1<=7'h7f;

9:L1<=7'h7b;

default:L1<=7'h00;

endcase

always@(reg_s0)

case(reg_s0)

0:L0<=7'h7e;

1:L0<=7'h30;

2:L0<=7'h6d;

3:L0<=7'h79;

4:L0<=7'h33;

5:L0<=7'h5b;

6:L0<=7'h5f;

7:L0<=7'h70;

8:L0<=7'h7f;

9:L0<=7'h7b;

default:L0<=7'h00;

endcase

endmodule

下面进行testbench学习与编写:

statement is similar to always, it just starts once at the beginning, and does not repeat.

Will execute at the beginning once.

Testbench has no inputs, outputs

实际上 initial块与always 块可看做是顺序执行的。因为在的always块运行时,initial已经给相应的信号赋了值,否则always出来的初始值应该是不可预期的,可能会是红线X。或者always块里本身也有赋初值的语句,

经过一番艰苦的探索,,,

- 编的过程中不仿真,最后两行泪。

- 调试的时候和C一样,把所有中间变量都输出然后监控进行调试。

- 一些vivado使用技巧。

下面进行仿真:

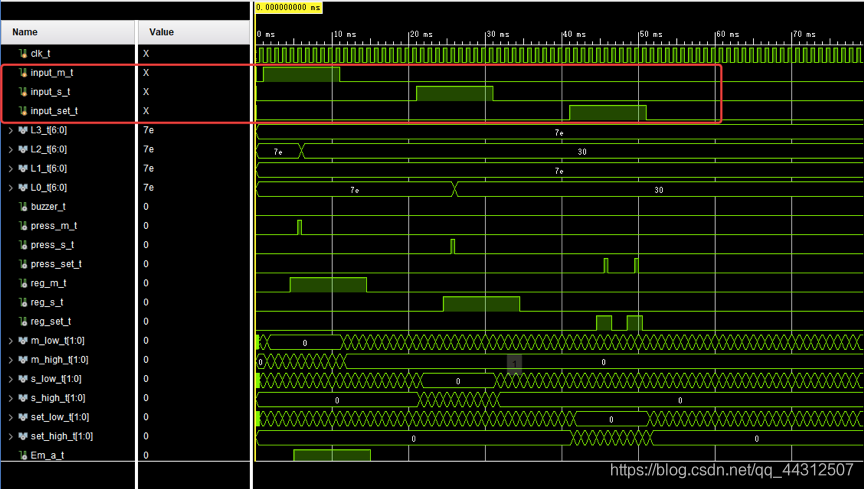

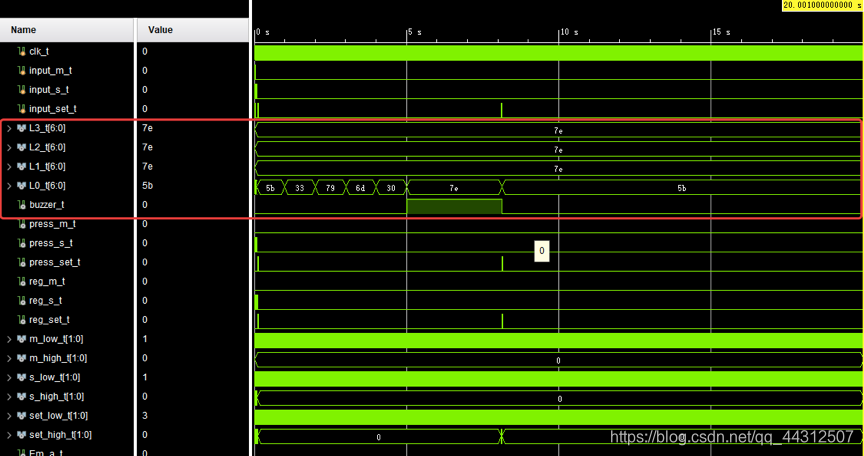

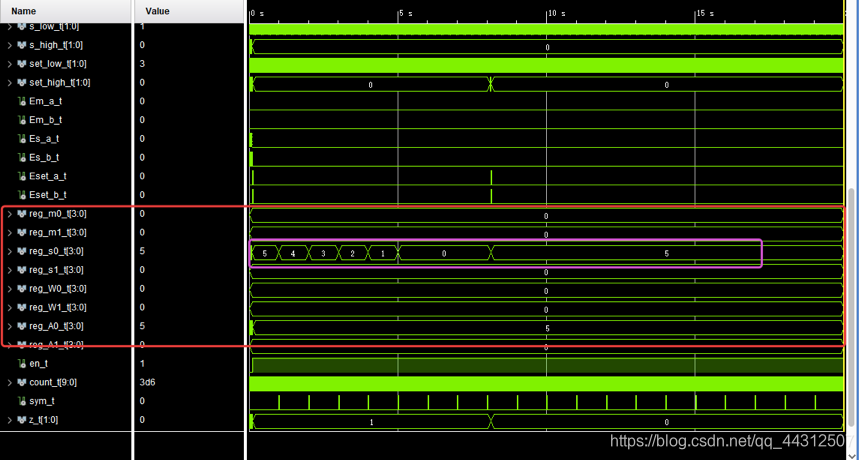

有许多事调试时监控的中间变量,最后也懒得删除了,留着还可以接着调试,真正的输入输出会圈出来。

外置态和倒计时:

`timescale 1ns / 1ps

//////////////////////////////////////////////////////////////////////////////////

// Company:

// Engineer:

//

// Create Date: 2019/11/28 10:31:59

// Design Name:

// Module Name: testbench_3

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//////////////////////////////////////////////////////////////////////////////////

module testbench_clock_set();

reg clk_t;

reg input_m_t;

reg input_s_t;

reg input_set_t;

wire [6:0] L3_t;

wire [6:0] L2_t;

wire [6:0] L1_t;

wire [6:0] L0_t;

wire buzzer_t;

////test

wire press_m_t;

wire press_s_t;

wire press_set_t;

wire reg_m_t;

wire reg_s_t;

wire reg_set_t;

wire [1:0]m_low_t;

wire [1:0]m_high_t;

wire [1:0]s_low_t;

wire [1:0]s_high_t;

wire [1:0]set_low_t;

wire [1:0]set_high_t;

wire Em_a_t;

wire Em_b_t;

wire Es_a_t;

wire Es_b_t;

wire Eset_a_t;

wire Eset_b_t;

wire [3:0]reg_m0_t;

wire [3:0]reg_m1_t;

wire [3:0]reg_s0_t;

wire [3:0]reg_s1_t;

wire [3:0]reg_W0_t;

wire [3:0]reg_W1_t;

wire [3:0]reg_A0_t;

wire [3:0]reg_A1_t;

wire en_t;

wire [9:0]count_t;

wire sym_t;

wire [1:0]z_t;

////test

Clock DUT(

.clk(clk_t),

.input_m(input_m_t),

.input_s(input_s_t),

.input_set(input_set_t),

.L3(L3_t),

.L2(L2_t),

.L1(L1_t),

.L0(L0_t),

.buzzer(buzzer_t),

////test

.press_m(press_m_t),

.press_s(press_s_t),

.press_set(press_set_t),

.reg_s(reg_s_t),

.reg_m(reg_m_t),

.reg_set(reg_set_t),

.m_low(m_low_t),

.m_high(m_high_t),

.s_low(s_low_t),

.s_high(s_high_t),

.set_low(set_low_t),

.set_high(set_high_t),

.Em_a(Em_a_t),

.Em_b(Em_b_t),

.Es_a(Es_a_t),

.Es_b(Es_b_t),

.Eset_a(Eset_a_t),

.Eset_b(Eset_b_t),

.reg_m0(reg_m0_t),

.reg_m1(reg_m1_t),

.reg_s0(reg_s0_t),

.reg_s1(reg_s1_t),

.reg_W0(reg_W0_t),

.reg_W1(reg_W1_t),

.reg_A0(reg_A0_t),

.reg_A1(reg_A1_t),

.en(en_t),

.count(count_t),

.sym(sym_t),

.z(z_t)

////test

);

initial #1 clk_t<=0;

always #500000 clk_t=~clk_t;//1000Kz时钟

initial begin

#1input_m_t<=0; input_s_t<=0; input_set_t<=0;

#1000000 input_m_t<=1; //input_s_t<=1;

#10000000 input_m_t<=0;//input_s_t<=0;

#10000000 input_s_t<=1;

#10000000 input_s_t<=0;

#10000000 input_set_t<=1;

#10000000 input_set_t<=0;

// #10000000 input_m_t<=1;

// #10000000 input_m_t<=0;

// #10000000 input_m_t<=1;

// #10000000 input_m_t<=0;

// #10000000 input_s_t<=1;

// #10000000 input_s_t<=0;

// #10000000 input_s_t<=1;

// #10000000 input_s_t<=0;

// #10000000 input_s_t<=1;

// #10000000 input_m_t<=1;

end

endmodule

输入:在原始状态(外置态)按一下 分设置按钮,按一下 秒设置按钮,按一下 设置按钮

结果对应1分1秒倒计时

输出:L3,L2,L1,L0,buzzer,

因为L是数码管,这里为了更方便,列出数码管控制寄存器

可以看到设置和倒计时和蜂鸣器正常。

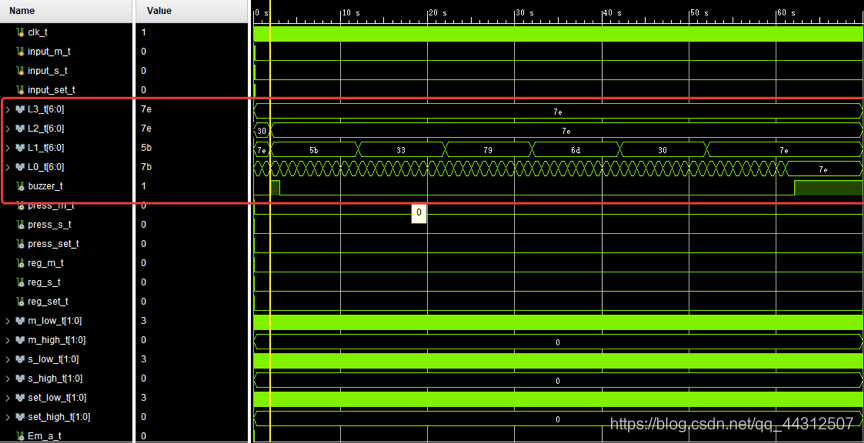

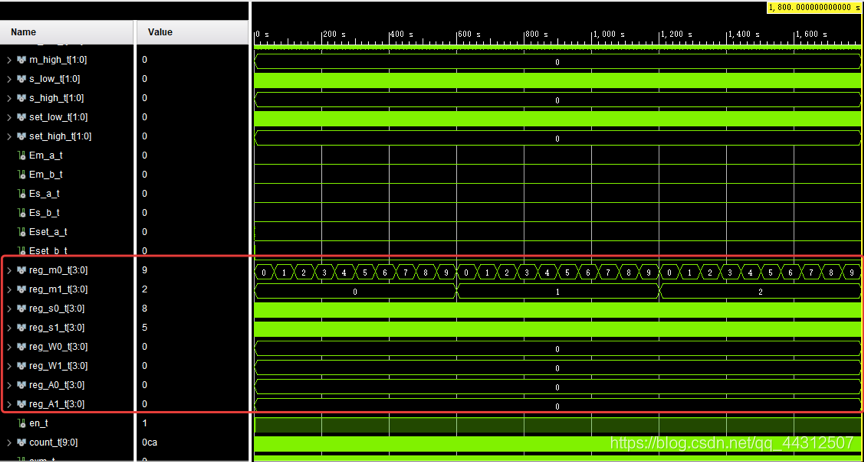

倒计时回到外置态

`timescale 1ns / 1ps

//////////////////////////////////////////////////////////////////////////////////

// Company:

// Engineer:

//

// Create Date: 2019/11/28 10:31:59

// Design Name:

// Module Name: testbench_3

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//////////////////////////////////////////////////////////////////////////////////

module testbench_clock_set();

reg clk_t;

reg input_m_t;

reg input_s_t;

reg input_set_t;

wire [6:0] L3_t;

wire [6:0] L2_t;

wire [6:0] L1_t;

wire [6:0] L0_t;

wire buzzer_t;

////test

wire press_m_t;

wire press_s_t;

wire press_set_t;

wire reg_m_t;

wire reg_s_t;

wire reg_set_t;

wire [1:0]m_low_t;

wire [1:0]m_high_t;

wire [1:0]s_low_t;

wire [1:0]s_high_t;

wire [1:0]set_low_t;

wire [1:0]set_high_t;

wire Em_a_t;

wire Em_b_t;

wire Es_a_t;

wire Es_b_t;

wire Eset_a_t;

wire Eset_b_t;

wire [3:0]reg_m0_t;

wire [3:0]reg_m1_t;

wire [3:0]reg_s0_t;

wire [3:0]reg_s1_t;

wire [3:0]reg_W0_t;

wire [3:0]reg_W1_t;

wire [3:0]reg_A0_t;

wire [3:0]reg_A1_t;

wire en_t;

wire [9:0]count_t;

wire sym_t;

wire [1:0]z_t;

////test

Clock DUT(

.clk(clk_t),

.input_m(input_m_t),

.input_s(input_s_t),

.input_set(input_set_t),

.L3(L3_t),

.L2(L2_t),

.L1(L1_t),

.L0(L0_t),

.buzzer(buzzer_t),

////test

.press_m(press_m_t),

.press_s(press_s_t),

.press_set(press_set_t),

.reg_s(reg_s_t),

.reg_m(reg_m_t),

.reg_set(reg_set_t),

.m_low(m_low_t),

.m_high(m_high_t),

.s_low(s_low_t),

.s_high(s_high_t),

.set_low(set_low_t),

.set_high(set_high_t),

.Em_a(Em_a_t),

.Em_b(Em_b_t),

.Es_a(Es_a_t),

.Es_b(Es_b_t),

.Eset_a(Eset_a_t),

.Eset_b(Eset_b_t),

.reg_m0(reg_m0_t),

.reg_m1(reg_m1_t),

.reg_s0(reg_s0_t),

.reg_s1(reg_s1_t),

.reg_W0(reg_W0_t),

.reg_W1(reg_W1_t),

.reg_A0(reg_A0_t),

.reg_A1(reg_A1_t),

.en(en_t),

.count(count_t),

.sym(sym_t),

.z(z_t)

////test

);

initial #1 clk_t<=0;

always #500000 clk_t=~clk_t;//1000Kz时钟

initial begin

#1input_m_t<=0; input_s_t<=0; input_set_t<=0;

// #1000000 input_m_t<=1; //input_s_t<=1;

// #10000000 input_m_t<=0;//input_s_t<=0;

#10000000 input_s_t<=1;

#10000000 input_s_t<=0;

#10000000 input_s_t<=1;

#10000000 input_s_t<=0;

#10000000 input_s_t<=1;

#10000000 input_s_t<=0;

#10000000 input_s_t<=1;

#10000000 input_s_t<=0;

#10000000 input_s_t<=1;

#10000000 input_s_t<=0;//5秒

#10000000 input_set_t<=1;

#10000000 input_set_t<=0;

#1000000000;

#1000000000;

#1000000000;

#1000000000;

#1000000000;

#1000000000;

#1000000000;

#1000000000 input_set_t<=1;

#10000000 input_set_t<=0;

end

endmodule

同样的:

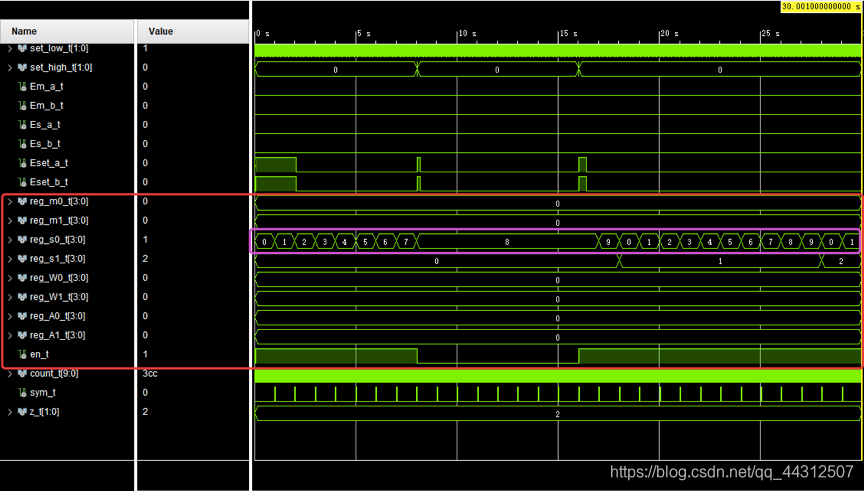

正计时

`timescale 1ns / 1ps

//////////////////////////////////////////////////////////////////////////////////

// Company:

// Engineer:

//

// Create Date: 2019/11/28 10:31:59

// Design Name:

// Module Name: testbench_3

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//////////////////////////////////////////////////////////////////////////////////

module testbench_clock_set();

reg clk_t;

reg input_m_t;

reg input_s_t;

reg input_set_t;

wire [6:0] L3_t;

wire [6:0] L2_t;

wire [6:0] L1_t;

wire [6:0] L0_t;

wire buzzer_t;

////test

wire press_m_t;

wire press_s_t;

wire press_set_t;

wire reg_m_t;

wire reg_s_t;

wire reg_set_t;

wire [1:0]m_low_t;

wire [1:0]m_high_t;

wire [1:0]s_low_t;

wire [1:0]s_high_t;

wire [1:0]set_low_t;

wire [1:0]set_high_t;

wire Em_a_t;

wire Em_b_t;

wire Es_a_t;

wire Es_b_t;

wire Eset_a_t;

wire Eset_b_t;

wire [3:0]reg_m0_t;

wire [3:0]reg_m1_t;

wire [3:0]reg_s0_t;

wire [3:0]reg_s1_t;

wire [3:0]reg_W0_t;

wire [3:0]reg_W1_t;

wire [3:0]reg_A0_t;

wire [3:0]reg_A1_t;

wire en_t;

wire [9:0]count_t;

wire sym_t;

wire [1:0]z_t;

////test

Clock DUT(

.clk(clk_t),

.input_m(input_m_t),

.input_s(input_s_t),

.input_set(input_set_t),

.L3(L3_t),

.L2(L2_t),

.L1(L1_t),

.L0(L0_t),

.buzzer(buzzer_t),

////test

.press_m(press_m_t),

.press_s(press_s_t),

.press_set(press_set_t),

.reg_s(reg_s_t),

.reg_m(reg_m_t),

.reg_set(reg_set_t),

.m_low(m_low_t),

.m_high(m_high_t),

.s_low(s_low_t),

.s_high(s_high_t),

.set_low(set_low_t),

.set_high(set_high_t),

.Em_a(Em_a_t),

.Em_b(Em_b_t),

.Es_a(Es_a_t),

.Es_b(Es_b_t),

.Eset_a(Eset_a_t),

.Eset_b(Eset_b_t),

.reg_m0(reg_m0_t),

.reg_m1(reg_m1_t),

.reg_s0(reg_s0_t),

.reg_s1(reg_s1_t),

.reg_W0(reg_W0_t),

.reg_W1(reg_W1_t),

.reg_A0(reg_A0_t),

.reg_A1(reg_A1_t),

.en(en_t),

.count(count_t),

.sym(sym_t),

.z(z_t)

////test

);

initial #1 clk_t<=0;

always #500000 clk_t=~clk_t;//1000Kz时钟

initial begin

#1input_m_t<=0; input_s_t<=0; input_set_t<=0;

// #1000000 input_m_t<=1; //input_s_t<=1;

// #10000000 input_m_t<=0;//input_s_t<=0;

#10000000 input_set_t<=1;

#10000000 input_set_t<=0;

// #10000000 input_s_t<=1;

// #10000000 input_s_t<=0;

// #10000000 input_s_t<=1;

// #10000000 input_s_t<=0;

// #10000000 input_s_t<=1;

// #10000000 input_s_t<=0;

// #10000000 input_s_t<=1;

// #10000000 input_s_t<=0;

// #10000000 input_s_t<=1;

// #10000000 input_s_t<=0;//5秒

// #10000000 input_set_t<=1;

// #10000000 input_set_t<=0;

// #1000000000;

// #1000000000;

// #1000000000;

// #1000000000;

// #1000000000;

// #1000000000;

// #1000000000;

// #1000000000 input_set_t<=1;

// #10000000 input_set_t<=0;

end

endmodule

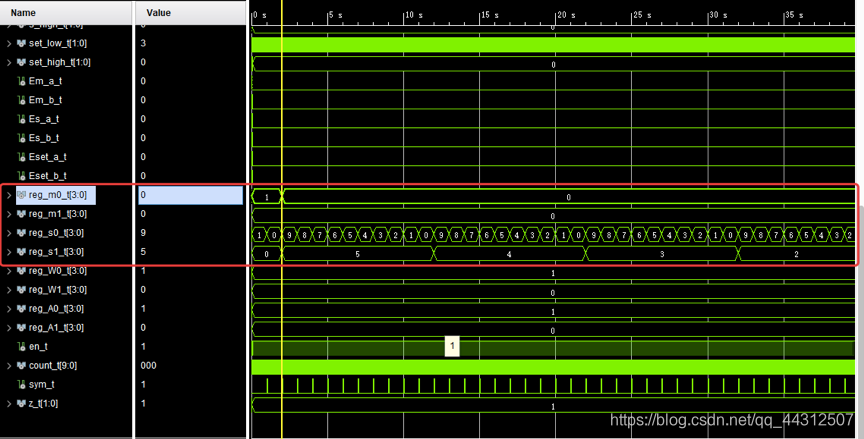

正计时暂停

`timescale 1ns / 1ps

//////////////////////////////////////////////////////////////////////////////////

// Company:

// Engineer:

//

// Create Date: 2019/11/28 10:31:59

// Design Name:

// Module Name: testbench_3

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//////////////////////////////////////////////////////////////////////////////////

module testbench_clock_set();

reg clk_t;

reg input_m_t;

reg input_s_t;

reg input_set_t;

wire [6:0] L3_t;

wire [6:0] L2_t;

wire [6:0] L1_t;

wire [6:0] L0_t;

wire buzzer_t;

////test

wire press_m_t;

wire press_s_t;

wire press_set_t;

wire reg_m_t;

wire reg_s_t;

wire reg_set_t;

wire [1:0]m_low_t;

wire [1:0]m_high_t;

wire [1:0]s_low_t;

wire [1:0]s_high_t;

wire [1:0]set_low_t;

wire [1:0]set_high_t;

wire Em_a_t;

wire Em_b_t;

wire Es_a_t;

wire Es_b_t;

wire Eset_a_t;

wire Eset_b_t;

wire [3:0]reg_m0_t;

wire [3:0]reg_m1_t;

wire [3:0]reg_s0_t;

wire [3:0]reg_s1_t;

wire [3:0]reg_W0_t;

wire [3:0]reg_W1_t;

wire [3:0]reg_A0_t;

wire [3:0]reg_A1_t;

wire en_t;

wire [9:0]count_t;

wire sym_t;

wire [1:0]z_t;

////test

Clock DUT(

.clk(clk_t),

.input_m(input_m_t),

.input_s(input_s_t),

.input_set(input_set_t),

.L3(L3_t),

.L2(L2_t),

.L1(L1_t),

.L0(L0_t),

.buzzer(buzzer_t),

////test

.press_m(press_m_t),

.press_s(press_s_t),

.press_set(press_set_t),

.reg_s(reg_s_t),

.reg_m(reg_m_t),

.reg_set(reg_set_t),

.m_low(m_low_t),

.m_high(m_high_t),

.s_low(s_low_t),

.s_high(s_high_t),

.set_low(set_low_t),

.set_high(set_high_t),

.Em_a(Em_a_t),

.Em_b(Em_b_t),

.Es_a(Es_a_t),

.Es_b(Es_b_t),

.Eset_a(Eset_a_t),

.Eset_b(Eset_b_t),

.reg_m0(reg_m0_t),

.reg_m1(reg_m1_t),

.reg_s0(reg_s0_t),

.reg_s1(reg_s1_t),

.reg_W0(reg_W0_t),

.reg_W1(reg_W1_t),

.reg_A0(reg_A0_t),

.reg_A1(reg_A1_t),

.en(en_t),

.count(count_t),

.sym(sym_t),

.z(z_t)

////test

);

initial #1 clk_t<=0;

always #500000 clk_t=~clk_t;//1000Kz时钟

initial begin

#1input_m_t<=0; input_s_t<=0; input_set_t<=0;

// #1000000 input_m_t<=1; //input_s_t<=1;

// #10000000 input_m_t<=0;//input_s_t<=0;

#10000000 input_set_t<=1;

#10000000 input_set_t<=0;

#1000000000;

#1000000000;

#1000000000;

#1000000000;

#1000000000;

#1000000000;

#1000000000;

#1000000000 input_set_t<=1;

#10000000 input_set_t<=0;

#1000000000;

#1000000000;

#1000000000;

#1000000000;

#1000000000;

#1000000000;

#1000000000;

#1000000000 input_set_t<=1;

#10000000 input_set_t<=0;

end

endmodule

可以看到暂停,启动正常。

3万+

3万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?