目录

1.特性

- 高性能:分辨率可配置为 12 位、10 位或 8 位;每个通道的采样时间可编程;数据对齐且内置数据一致性;支持直接内存访问(DMA);最多可对 32 次转换求平均值。

- 低功耗:能在微控制器(MCU)的等待(WAIT)/ 停止(STOP)模式下工作;等待模式可防止 ADC 在低总线时钟频率应用中溢出;自动禁用模式在非启动转换阶段禁用 ADC,降低功耗。

- 模拟输入通道:有 32 个来自 IO 的外部模拟输入和 5 个内部通道;转换启动方式可通过软件,也可通过极性可配置的硬件触发。

- 转换模式:可转换单个通道或扫描一系列通道;有单次模式(每次触发转换一次)、连续模式(连续转换)和不连续模式。

- 中断生成:在采样结束、转换结束、序列转换结束时,或发生 ADC 比较、溢出事件,以及 ADC 或先入先出队列(FIFO)准备好时产生中断。

- ADC 比较功能:转换器可使用内部或外部参考;支持单端和差分输入配置。

- 注意:自动禁用模式和差分输入功能仅部分设备(FC4150F2M、FC4150F1M_A 和 FC4150I1M_B)支持,其他特性所有设备均支持;仅支持 32 位访问 。

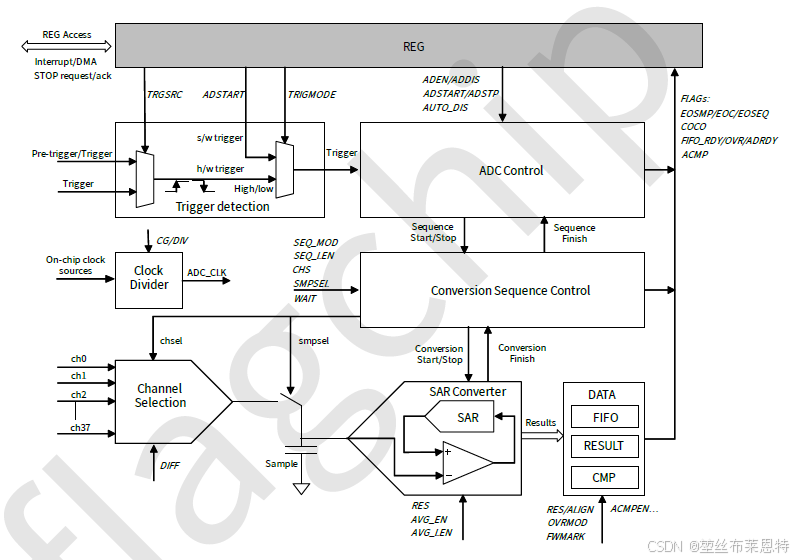

2.概述

- ADC 基本特性:该 ADC 是一个精度为 12 位的逐次逼近寄存器型(SAR)模拟数字转换器,拥有多达 38 个通道,其中 32 个外部模拟源通道和 5 个内部模拟源通道,可用于测量不同的模拟信号。

- 转换模式与数据存储:各个通道的 A/D 转换可在单次、连续或不连续模式下执行,转换结果数据存储在先进先出队列(FIFO)或结果寄存器中,数据格式可以是左对齐或右对齐。

- 参考电压选择:FC4150 系列 MCU 支持 2 个 ADC,可通过 ADC_CFG2.REF_EXT 选择内部或外部参考电压。外部参考电压连接到 VREFH 和 VREFL;内部参考电压连接到 VDDA 和 VSSA。

3.功能描述

3.1 ADC控制模块

3.1.1 ADC开启和关闭

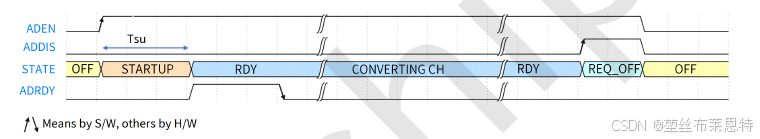

- 基本原理:在微控制器(MCU)上电时,ADC 处于禁用和掉电模式(ADEN=0)。在准确转换前,ADC 需要一段稳定时间 Tsu。通过两个控制位 ADEN 和 ADDIS 来启用或禁用 ADC。将 ADEN 设为 1 可启用 ADC,一旦 ADC 准备好运行,ADRDY 标志位就会被置位。将 ADDIS 设为 1 可禁用 ADC 并使其进入掉电模式,当 ADC 完全禁用后,ADEN 和 ADDIS 位会被硬件自动清零。启用触发后,可通过设置 ADSTART 为 1 或外部触发事件来启动转换。

- 启用 ADC 步骤:首先在 ADC_CONTROL 寄存器中将 ADEN 设为 1;然后等待 ADC_INT_STATUS 寄存器中的 ADRDY 变为 1(ADRDY 在 ADC 启动时间后设置),如果在 ADC_INT_STATUS 寄存器中使能了中断(设置 ADRDYIE 位),则可以通过中断处理。

- 禁用 ADC 步骤:先检查 ADC_CONTROL 寄存器中的 ADSTART 是否为 0,以确保没有正在进行的转换;如有必要,通过将 ADC_CONTROL 寄存器中的 ADSTP 位写 1 来停止正在进行的转换,并等待该位变为 0;接着在 ADC_CONTROL 寄存器中将 ADDIS 设为 1;根据应用需求,等待 ADC_CONTROL 寄存器中的 ADEN 变为 0(对于 FC4150F512,还需额外 3 个 ADC_CLK 周期),当 ADEN 为 0 时,表明 ADC 已完全禁用(ADDIS 在 ADEN 为 0 时会自动复位)。

3.1.2 ADC控制寄存器的写入操作

- ADEN 位写入条件:当 ADC 处于禁用状态时(此时 ADEN 肯定为 0 ),软件必须向 ADC_CONTROL 寄存器中的 ADEN 位进行写入操作,以启用 ADC。

- ADSTART 和 ADDIS 位写入条件:仅当 ADC 处于就绪(RDY)且已启用状态(ADEN = 1),同时没有挂起的禁用 ADC 请求(ADDIS = 0)时,软件才能向 ADC_CONTROL 寄存器中的 ADSTART 和 ADDIS 位进行写入操作。

- 其他控制位写入条件:对于 ADC_CFG1、ADC_CFG2、ADC_SMPR、ADC_CMP_CTRL、ADC_CMP_TR 和 ADC_SCn 等寄存器中的其他控制位,仅当没有正在进行的转换(ADSTART = 0)时,软件才能对配置控制位进行写入操作。对于 FC4150F512,这意味着在触发 ADSTART 之前、执行 ADSTP 步骤之后,或者在软件触发的转换完成并获取 ADRDY 标志后;对于 FC4150F2M、FC4150F1M_A 和 FC4150I1M_B ,则是在获取 ADRDY 标志之后 。

3.1.3 ADC的通道选择

- 通道组成:ADC 有多达 38 个复用通道,其中 32 个来自 IO 的模拟输入通道和 5 个内部模拟输入通道。

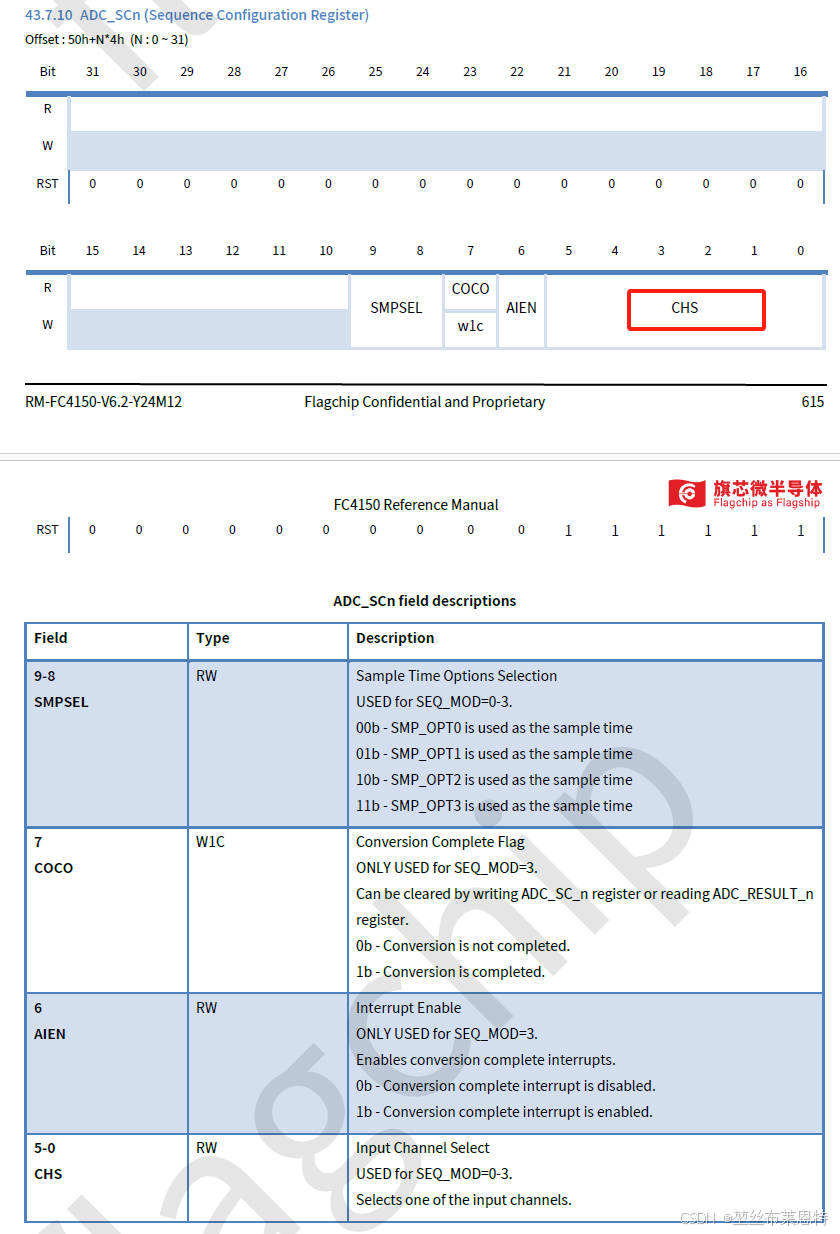

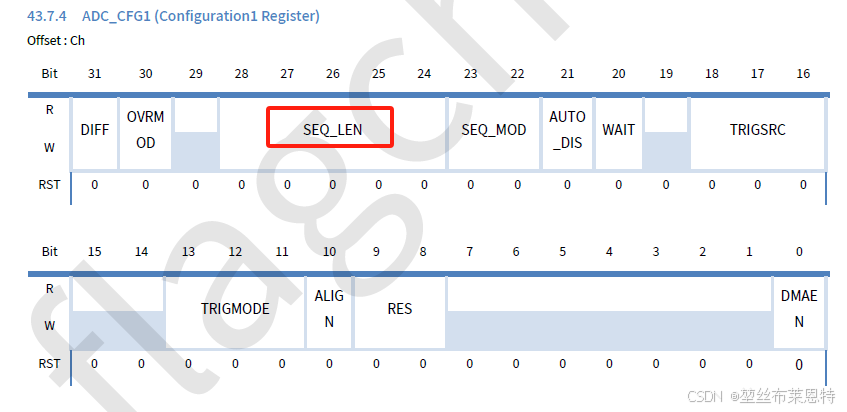

- 转换方式:既可以转换单个通道,也能自动扫描一系列通道。要转换的通道序列按照 ADC_SC0.CHS、ADC_SC1.CHS 、……、ADC_SC31.CHS 的顺序组织,通道序列的长度通过 ADC_CFG1 寄存器中的 SEQ_LEN 进行编程设置。

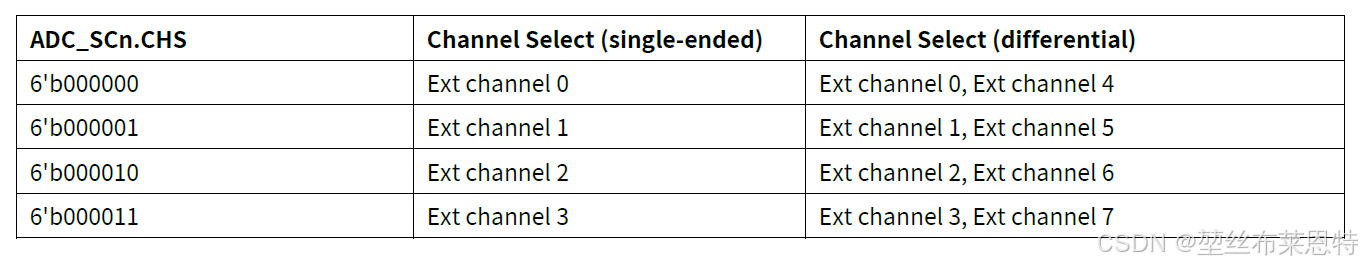

通道选择寄存器

序列长度配置寄存器

- 通道编码:不同编码值对应的单端和差分通道选择情况。单端模式下,如 6'b000000 对应外部通道 0;差分模式下,部分编码有对应组合(如 6'b000000 对应外部通道 0 和外部通道 4 )

3.1.4 ADC采样时间设置

- 采样原理:在开始转换之前,ADC 需要在待测电压源和其内部的采样电容之间建立直接连接。采样时间必须足够长,以确保输入电压源能够给采样保持电容充电,并使其达到输入电压水平。

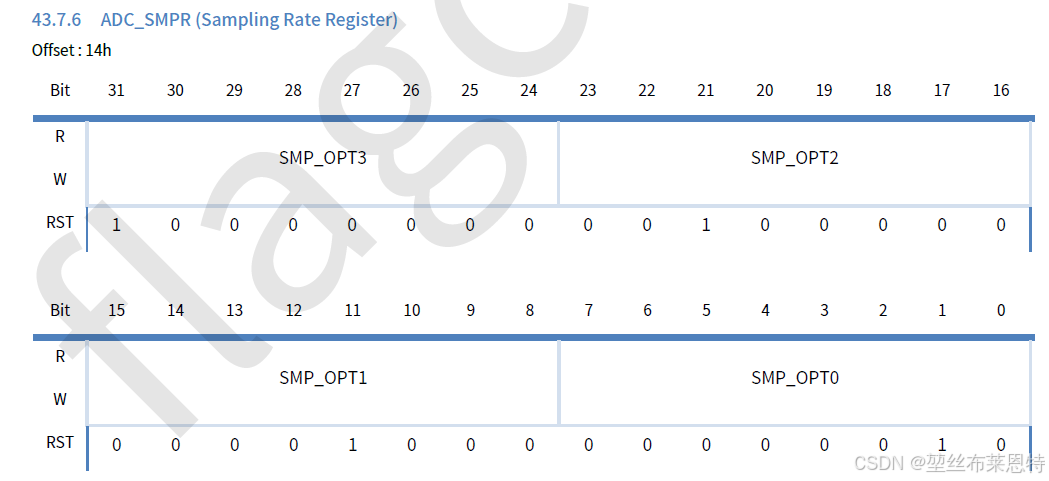

- 可编程采样时间:通过可编程采样时间,可以根据输入电压源的输入电阻来调整转换速度。对于 FC4150F512,ADC 的第 n 通道会在几个 ADC 时钟周期内对输入电压进行采样,具体时钟周期数可通过 ADC_Scn.SMPSEL 位和 ADC_SMPR 寄存器进行选择。对于 FC4150F2M、FC4150F1M_A 和 FC4150I1M_B ,ADC 通道(由 ADC_Scn.CHS 选定)同样在几个 ADC 时钟周期内采样输入电压,时钟周期数也是通过 ADC_Scn.SMPSEL 位和 ADC_SMPR 寄存器选择。

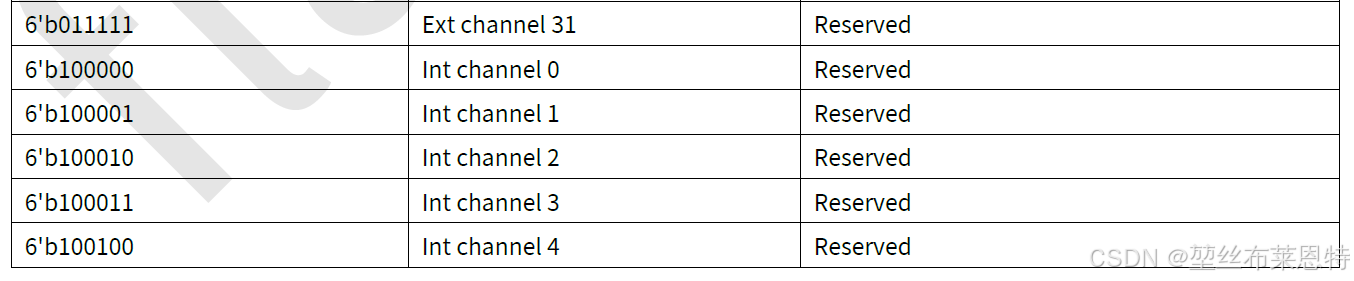

四个采样时间配置:采样时间 = (SMP_OPTN[7:0] + 2) * ADC时钟周期,设置的最小时间是2

具体通道选择第几个时间采样配置

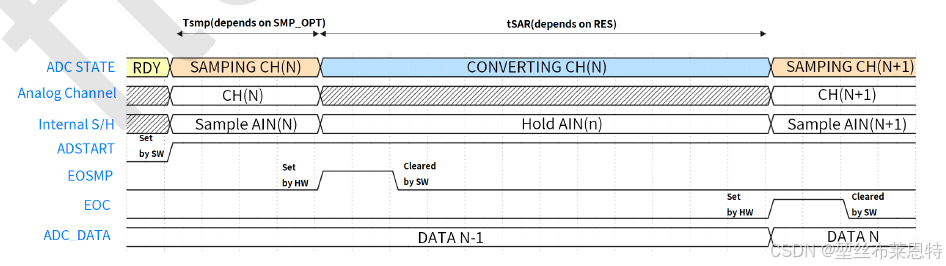

- 采样结束标志:ADC 通过设置 EOSMP 标志位来指示采样阶段的结束

3.1.5 ADC开启转换

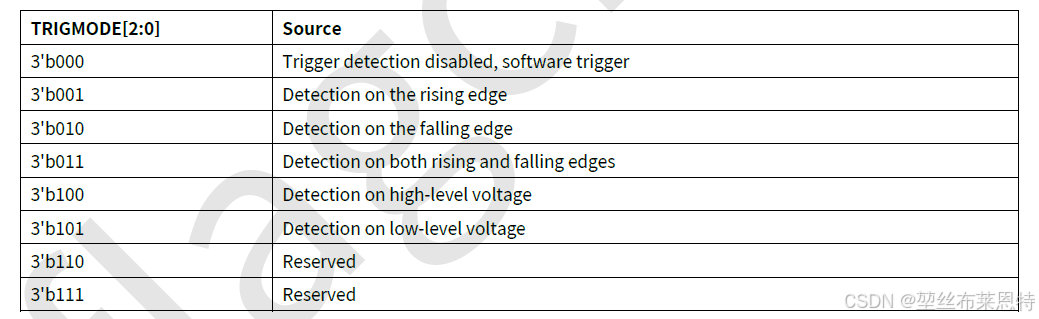

- 转换启动方式:软件通过将 ADSTART 设为 1 来启动 ADC 转换。当 ADSTART 被设置后,如果 TRIGMODE = 0x0(软件触发),转换立即开始;如果 TRIGMODE ≠ 0x0(硬件触发),则在所选硬件触发的下一个有效沿开始转换。

- ADSTART 位清除条件:

- 单次模式(SEQ_MOD = 0)且软件触发时,在任何转换序列结束(EOSEQ = 1)时,硬件会清除 ADSTART 位。

- 不连续模式 0(SEQ_MOD = 2)且软件触发时,在任何转换结束时,硬件会清除 ADSTART 位。

- 在所有情况下,在软件调用 ADSTP 程序执行后,硬件会清除 ADSTART 位。

- 重新启动转换注意事项:对于 FC4150F512,重新设置 ADSTART 时,需确保在执行 ADSTP 程序之后,或者在软件触发的转换完成并获取 ADRDY 标志之后;对于 FC4150F2M、FC4150F1M_A 和 FC4150I1M_B ,则要确保已获取 ADRDY 标志。

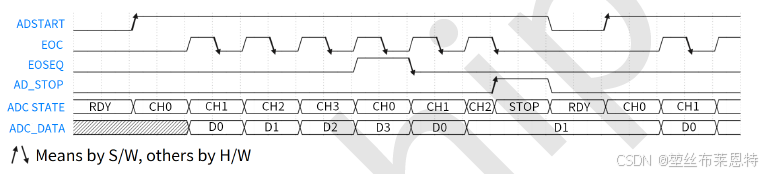

3.1.6 ADC停止转换

停止转换的方法

软件可以通过将 ADC_CONTROL 寄存器中的 ADSTP 位置为 1,来决定停止任何正在进行的转换。当 ADSTP 位被软件置 1 后,会重置 ADC 的操作,ADC 将进入空闲状态,为新的操作做好准备。同时,任何正在进行的转换会被中止,扫描序列也会被中止并重置,这意味着重新启动 ADC 时将开始一个新的序列。

操作完成后的状态及后续处理

一旦停止转换的操作完成,ADC 将回到就绪(RDY)状态,并且 ADSTP 和 ADSTART 位会被硬件自动清零。在启动新的转换之前,软件必须等待,直到 ADSTP 变为 0;对于 FC4150F512,还需要再等待 3 个 ADC 功能时钟周期。

3.2 ADC触发检测模块

3.2.1 基于外部触发的转换以及触发极性

配置触发极性

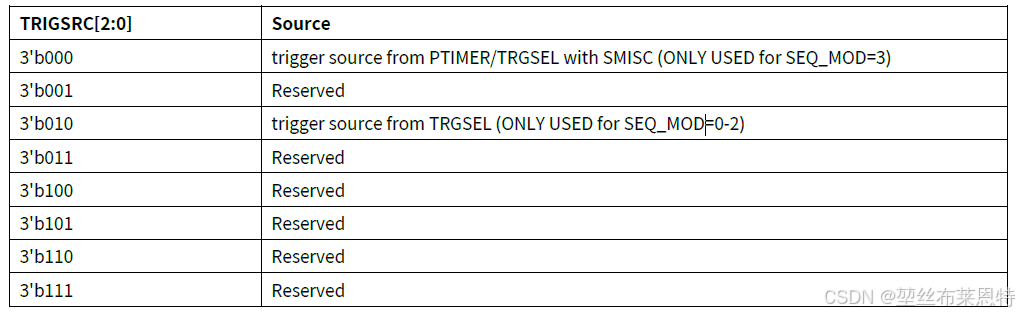

配置触发源的选择

3.2.2 触发源的选择

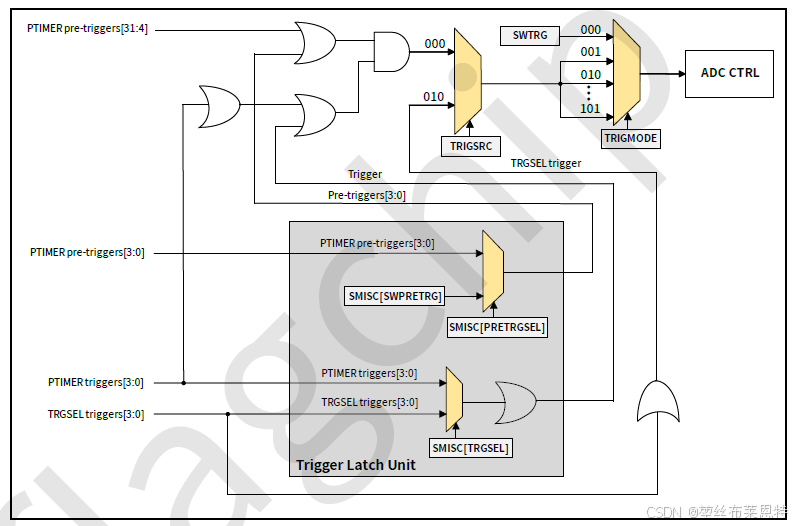

- 触发源构成:ADC 的预触发和触发信号来自 PTIMER(可能是某种定时器)、TRGSEL(触发选择信号)以及 SMISC(可能是系统管理相关的模块)。较低的 4 个预触发和不同来源的触发信号在触发锁存单元(Trigger Latch Unit)中复用,该单元还负责锁存和仲裁。

- 特殊模式设定:在不连续模式 1(SEQ_MOD = 3)下,TRIGSRC 寄存器的值被忽略,会选择来自 PTIMER/TRGSEL 与 SMISC 的预触发(3'b000)作为触发源;TRIGMODE 寄存器的值也被忽略,会选择上升沿检测(3'b001)。

如图所示,触发源有TRGSEL模块过来的四路触发源(由TRGSEL MUX模块配置,总共有四路,任意选择1路效果是一样的)PTIMER的四个channel产生的32个pretriggers和SCn寄存器一一对应(pretrigger让ADC的SC选择外部channel,ptimer的四个channel产生的TRIGGER信号开启ADC转换)

如上图所示,前面四个是ptimer channel0的四个delay的pretriggers,最下面的是ptimer channel0的trigger信号

3.3 ADC转换序列模式

3.3.1 单次转换模式

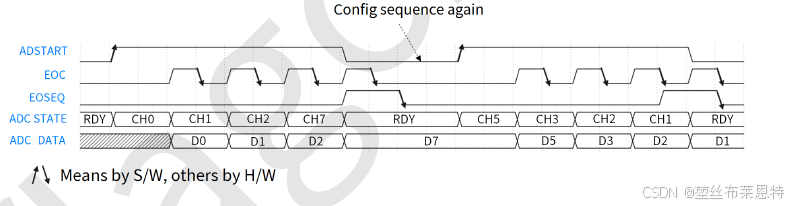

- 单转换模式概述:在单转换模式下,ADC 仅对序列进行一次转换。可以通过两种方式启动转换:设置 ADC_CONTROL 寄存器中的 ADSTART 位;触发硬件触发事件。

- 转换完成后的操作:在转换序列中,每次转换完成后,转换后的数据会存储到 FIFO(先进先出缓冲区)中;转换结束标志(EOC)会被置位;若 EOCIE(转换结束中断使能)位被置位,则会产生一个中断。

- 序列完成后的操作:当整个转换序列完成后,序列结束标志(EOSEQ)会被置位;若 EOSEQIE(序列结束中断使能)位被置位,则会产生一个中断。此后,ADC 会停止工作,直到出现新的外部触发事件或再次设置 ADSTART 位。

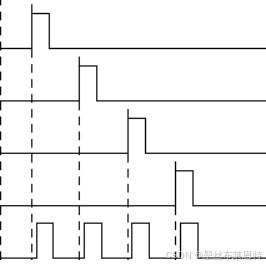

软件触发

硬件触发

3.3.2 连续转换模式

- 连续转换模式概述:在连续转换模式下,当软件或硬件触发事件发生时,ADC 执行一个转换序列。完成一次序列转换后,会自动重新启动并持续执行相同的转换序列。可以通过两种方式启动转换:设置 ADC_CONTROL 寄存器中的 ADSTART 位;触发硬件触发事件。

- 转换过程中的操作:在转换序列中,每次转换完成后,转换后的数据会存储到 FIFO(先进先出缓冲区)中;转换结束标志(EOC)会被置位;若 EOCIE(转换结束中断使能)位被置位,则会产生一个中断。

- 序列完成后的操作:当整个转换序列完成后,序列结束标志(EOSEQ)会被置位;若 EOSEQIE(序列结束中断使能)位被置位,则会产生一个中断。之后,新的转换序列会立即重新启动,ADC 持续重复执行转换序列。

软件触发

硬件触发

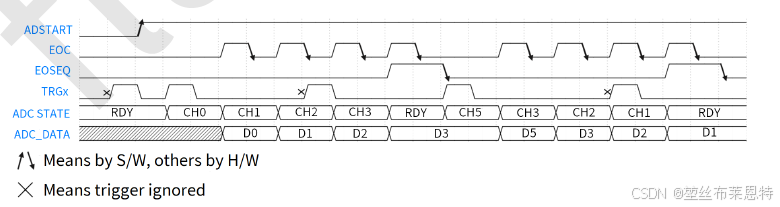

3.3.3 不连续转换模式0

- 模式概述:在该模式下,需要软件或硬件触发事件来启动序列中定义的每次转换。当设置 ADSTP(转换停止)位时,转换过程将会停止。

- 示例:假设要转换的通道为 0、3、7、10。

- 第 1 次触发:转换通道 0,并产生转换结束(EOC)事件。

- 第 2 次触发:转换通道 3,并产生 EOC 事件。

- 第 3 次触发:转换通道 7,并产生 EOC 事件。

- 第 4 次触发:转换通道 10,同时产生 EOC 和序列结束(EOSEQ)事件。

- 第 5 次触发:再次转换通道 0,并产生 EOC 事件,后续按此顺序循环。

3.3.4 不连续转换模式1

- 模式概述:此模式下,需要带有预触发的硬件触发事件来启动序列中定义的每次转换,同样当设置 ADSTP 位时,转换停止。

- 与 PTIMER 协同工作:ADC 可以在启用 PTIMER的背对背(BTB)预触发操作下工作。通过 PTIMER 的 BTB 操作,ADC 能够以可配置的延迟时间对指定通道进行采样。例如,ADC 将选择 ADC_SCn.CHS 中指定的通道,其中 n 由 PTIMER 预触发确定。此模式下,序列长度(SEQ_LEN)无效。

- 转换结果存储:在该模式中,ADC 的转换结果存储在 ADC_RESULTn 寄存器中,而不是 FIFO(先进先出缓冲区) 。

3.4 ADC转换结果管理

3.4.1 可编程的分辨率

- 提高转换速度的方式:通过降低 ADC 的分辨率,可以获得更快的转换时间(tSAR)。在对数据精度要求不高的应用场景中,这种方式能提升转换效率。

- 分辨率的配置:可以通过对 ADC_CFG1 寄存器中的 RES [1:0] 位进行编程,将分辨率配置为 12 位、10 位或 8 位。

- 转换结果特点:无论配置的分辨率是多少,转换结果始终是 12 位宽。当分辨率低于 12 位时,未使用的最低有效位(LSB)会被读为零。

3.4.2 ADC硬件平均功能

- 功能启用:可以通过将 ADC_CFG2 寄存器中的 AVG_EN 位置为 1,来启用 ADC 的硬件平均功能。

- 平均次数设置:通过配置 ADC_CFG2 寄存器中的 AVG_LEN 位,可以设置平均次数,范围是 4 到 32 次。

- 结果存储与标志位:平均后的结果会被保存到 FIFO(先进先出缓冲区)或者 ADC_RESULT 寄存器中,而原始的转换结果不会被保存。EOSMP(采样结束)、EOC(转换结束)、EOSEQ(序列结束)这些标志位,仅在最后一次平均转换步骤时才会被置位。

3.4.3 数据对齐

数据对齐方式

- 控制方式:数据对齐方式由 ADC_CFG1 寄存器中的 ALIGN 位选择。当 ALIGN = 0 时,数据为右对齐;当 ALIGN = 1 时,数据为左对齐。

- 不同分辨率下的存储格式:表格展示了在不同的 ALIGN 设置和 RES [1:0](分辨率设置)下,数据在 32 位存储单元中的存放位置。比如,当 ALIGN = 0,RES [1:0] = 0x0 时,12 位数据 data [11:0] 存放在低 12 位;当 ALIGN = 1,RES [1:0] = 0x1 时,10 位数据 data [9:0] 存放在高 10 位。

不同输入配置下的数据格式

- 单端输入配置:转换后的数据是无符号数据,范围从 0 到最大值(由分辨率决定,如 12 位分辨率时最大值为212−1 ),输入范围是从最小值(VREFL/VSSA)到最大值(VREFH/VDD)。

- 差分输入配置:转换后的数据同样是无符号数据,范围从 0 到最大值(由分辨率决定),输入范围是从最小值(VREFL - VREFH/VSSA - VDDA)到最大值(VREFH - VREFL/VDDA - VSSA)。特定输入值对应特定输出,例如输入为 VREFL - VREFH 时,ADC 输出数据为 0;输入为 VREFH - VREFL 时,12 位分辨率下 ADC 输出数据为 4095;输入为 0V 时,12 位分辨率下 ADC 输出数据为 2048 。

3.4.4 ADC结果溢出

溢出标志(OVR)含义

溢出标志(OVR)用于指示数据溢出事件,当 FIFO(先进先出缓冲区)已满,且转换后的数据未被 CPU 或 DMA 及时读取时,该事件发生。

溢出标志的设置与中断

- 当新的转换完成时,如果 FULL 标志仍为 “1”,则在 ADC_INT_STATUS 寄存器中设置 OVR 标志。

- 如果在 ADC_INT_STATUS 寄存器中设置了 OVRIE 位,就可以产生一个中断。

溢出发生时 ADC 的状态

当发生溢出情况时,ADC 会继续运行并持续转换,除非软件通过设置 ADC_CONTROL 寄存器中的 ADSTP 位来停止并重置转换序列。

溢出标志的清除

OVR 标志可通过软件向其写入 1 来清除。

溢出模式(OVRMOD)配置

可以通过对 ADC_CFG1 寄存器中的 OVRMOD 位进行编程,来配置在溢出事件发生时数据是保留还是被覆盖:

- OVRMOD = 0:溢出事件会保留数据寄存器中的内容不被覆盖,即旧数据保持不变,新的转换结果将被丢弃。如果 OVR 标志仍为 1,可继续进行后续转换,但转换结果都会被丢弃。

- OVRMOD = 1:数据寄存器会被最后一次转换结果覆盖。如果 OVR 标志仍为 1,也可继续进行后续转换,且 FIFO 中始终包含最新的转换数据 。

3.4.5 ADC与DMA

SEQ_MOD = 0 - 2 时的情况

当转换序列模式(SEQ_MOD)的值为 0 到 2 时,一旦 FIFO(先进先出缓冲区)中的数据条目数量超过 FWMARK(FIFO 水位标记)的设置,并且 DMAEN(DMA 使能)位被置位,ADC 就会向 DMA 发送请求。这个请求使得转换后的数据能够从 FIFO 传输到软件选定的目标位置。

SEQ_MOD = 3 时的情况

当 SEQ_MOD 的值为 3 且 DMAEN 位被置位时,一旦 ADC 完成一次转换,并且 ADC_SCn.COC(转换完成)标志被置位,DMA 请求就会被设置,这样就能将 ADC_RESULTn 寄存器中的转换数据传输到软件选定的目标位置 。

3.5 ADC中断

ADC 可以由以下任意事件产生中断:

- ADC 准备就绪:当 ADC 准备好时,对应的 ADRDY 标志置位,会产生中断。这意味着 ADC 已完成初始化等准备工作,可进行转换操作。

- 采样阶段结束:EOSMP 标志置位,即采样阶段结束时触发中断,提示采样操作已完成。

- 任意转换结束:EOC/COCO 标志置位时,表明一次 ADC 转换完成,此时会产生中断,方便获取转换结果。

- 转换序列结束:当整个转换序列完成,EOSEQ 标志置位,会触发中断,用于告知一系列转换操作已全部结束。

- 数据溢出:出现数据溢出情况,OVR 标志置位时产生中断,提醒数据处理不及时,FIFO 可能已满。

- 采样电压超出范围:若采样电压不在规定范围内,ACMP 标志置位,触发中断,可用于监测异常电压输入。

- FIFO 数据量超水位标记:当 FIFO 中的数据数量大于预先设置的水位标记,FIFO_RDY 标志置位,产生中断,以便及时处理 FIFO 中的数据 。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?