1.1边沿检测电路原理

边沿检测指的是检测一个信号的上升沿或者下降沿,如果发现上升沿或者下降沿,则给出一个信号指示

出来。边沿检测电路一般分为上升沿检测电路、下降沿检测电路和双沿检测电路。

复杂的逻辑设计里面,很多情况都需要检测信号的跳变,如果一个信号发生跳变,则给出一个指示, 这

个指示用来触发其他的动作。这里就需要有一个边沿检测电路,因此这个电路是非常常见的一个典型电路,

其设计思想也是一个很重要的设计思想。

我们根据检测边沿的类型一般可以将边沿检测分为上升沿检测电路、下降沿检测电路和双沿检测电路。

下面我们依次来看下这几个类型。我们先来看下上升沿检测电路,信号检测由 0 变 1 的过程,就是上

升沿检测电路(posedge edge), 信号检测由 1 变 0 的过程, 就是下降沿检测电路(negedge edge)。若上升

沿和下降沿都检测,则这个电路就是双沿检测电路(double edge)。

与此同时我们清楚在always程序块中有上升沿触发,下降沿触发,但是内部信号到底是是上升沿触发,还是下降沿触发的,我们并不清楚,下面我写了一个代码进行测试内部信号到底是上身沿,还是下降沿,还是信号本身触发的

//file name : test_edge.v

//file function : 测试信号内部到底是那个触发源触发的

//file version : 1.0version

//file date :2023\4\3

//Author :ZihangNie

//*******************************************

module test_edge(

input sys_clk ,

input sys_rst_n ,

input a,

input b,

//output signal

output reg y

);

always@(posedge sys_clk or negedge sys_rst_n or posedge a ) begin

if(!sys_rst_n) begin

y <= 1'b0 ;

end

else begin

y <= b;

end

end

endmodule

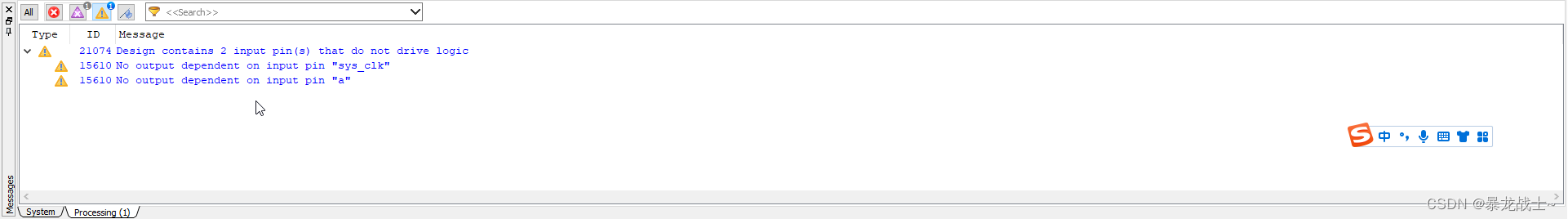

我们可以通过RTL图看出来,sys_clk 和 a 这两个信号没有接入电路,内部信号源的触发完全是由于sys_rst_n的触发源触发的

这只是一个组合电路,并不是我们想要设计的时序电路,这种边沿检测电路是不合理的,这个地方的警告也可以间接的说明在always敏感变量里面只能有一个复位信号和时钟,带时钟的 always 块电路都是寄存器,而寄存器一

般只有一个时钟信号,所以边沿检测不能直接利用 always块语句里面的信号敏感变量作为边沿检测。

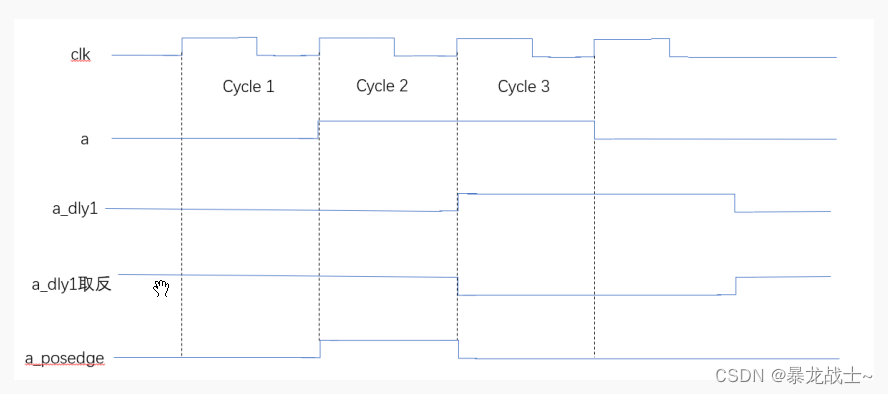

1.1.1上升沿检测电路原理

从上升沿检测电路中可以明白检测原理, 将信号a 先延迟一拍 得到 a_dly1, 然后将信号取反~a_dly_1,然后信号 a_posedge = a & ~a_dly1 ; 所得到的;

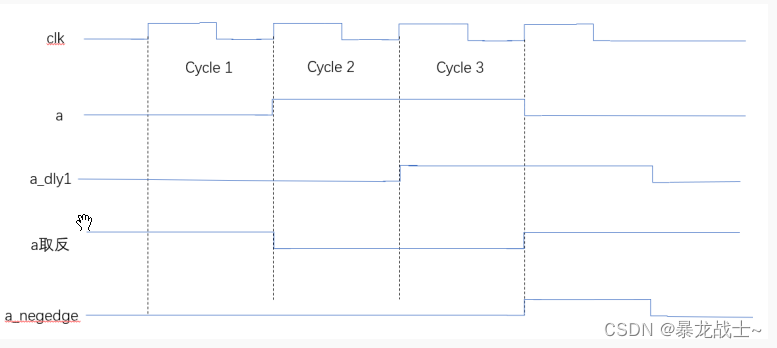

1.1.2下降沿检测电路原理

同理可知 a_nededge = a_dly1 & ~a ;

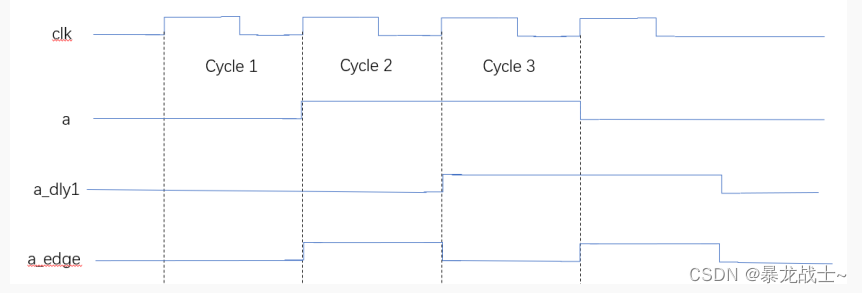

1.1.3 双边沿电路检测电路

a_edge = a ^ a_dly1 ;

1.1.4 程序设计

//file name : n_p_d_edge.v

//file function : 实现边沿检测电路其中包括上边沿检测,下边沿检测,双边沿检测

//file version : 1.0version

//file date : 2023/4/3

//Author : ZihangNie

//*****************************************

module n_p_d_edge (

//input signal ;

input sys_clk , //输入时钟

input sys_rst_n, //输入复位信号

input a , //输入 a

//output signal

output y1, // 输出上边沿检测信号y1,

output y2, // 输出下边沿检测信号y2,

output y3 // 输出双边沿检测 信号y3

);

//寄存器定义

reg a_dly_reg ; //定义一个延迟寄存器

//***************************main***************

//***************************code***************

always@(posedge sys_clk or negedge sys_rst_n) begin

if (!sys_rst_n) begin

a_dly_reg <= 1'b0;

end

else begin

a_dly_reg <= a;//延迟一拍

end

end

assign y1 = ~a_dly_reg & a ;

assign y2 = ~a &(a_dly_reg);

assign y3 = a_dly_reg ^ a ;

endmodule

1.1.5 testbench 文件

//file name : tb_n_p_d_edge.v

//file function : 设计一个上升沿,下降沿,双边沿检测的仿真电路

//file version : 1.0version

//file date : 2023/4/4

//Author :ZihangNie

//*****************************************************************

`timescale 1ns/1ps //仿真时间单位1ns/仿真精度1ps

module tb_n_p_d_edge(); //仿真模块定义

//定义输入信号

reg sys_clk ; //定义输入时钟信号

reg sys_rst_n ; //定义复位信号

reg a ; //定义输入信号a

//定义输出信号

wire y1 ; // 上边沿检测信号

wire y2 ; // 下边沿检测信号

wire y3 ; // 双边沿检测信号

//初始化操作

initial begin

sys_clk = 1'b0 ;

sys_rst_n = 1'b0 ;

a = 1'b0 ;

#200

sys_rst_n = 1'b1 ;

#100

a = 1'b1 ;

#60

a = 1'b0 ;

end

always #10 sys_clk = ~sys_clk ; //每隔十个时钟单位取反一次

//对模块进行例化

n_p_d_edge u_n_p_d_edge(

.sys_clk(sys_clk),

.sys_rst_n(sys_rst_n),

.a(a),

.y1(y1),

.y2(y2),

.y3(y3)

);

endmodule

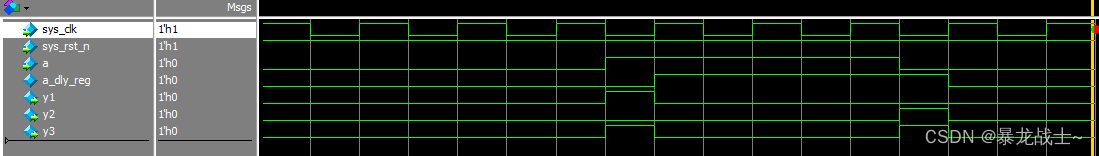

1.1.6modelsim仿真图

从仿真图上可以看出很好的实现了预期的检测功能,与预期结果一致。

本文介绍了边沿检测电路的基本概念,包括上升沿、下降沿和双沿检测,并通过Verilog代码展示了如何设计这些电路。在always块中,详细讨论了信号触发源的问题,并提供了一段测试代码来验证内部触发源。此外,还提供了n_p_d_edge模块的实现,用于上、下和双边沿检测,并附带了相应的testbench文件进行仿真验证,结果显示电路功能符合预期。

本文介绍了边沿检测电路的基本概念,包括上升沿、下降沿和双沿检测,并通过Verilog代码展示了如何设计这些电路。在always块中,详细讨论了信号触发源的问题,并提供了一段测试代码来验证内部触发源。此外,还提供了n_p_d_edge模块的实现,用于上、下和双边沿检测,并附带了相应的testbench文件进行仿真验证,结果显示电路功能符合预期。

398

398

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?