1.锁存器的概念

锁存器( latch)是电平触发的存储单元,数据存储的动作取决于输入时钟(或者使能)信号的电

平值,尽当锁存器处于使能状态时,输出才会随着数据输入发生变化。

锁存器不同于触发器,锁存器在不锁存数据时,输出端的信号随输入信号变化,就像信号通过一

个缓存器一样;一旦锁存信号起锁存作用,则数据被锁住,输入信号不起作用。因此锁存器也称为透明锁存器, 指的是不锁存时输出对输入是透明的。

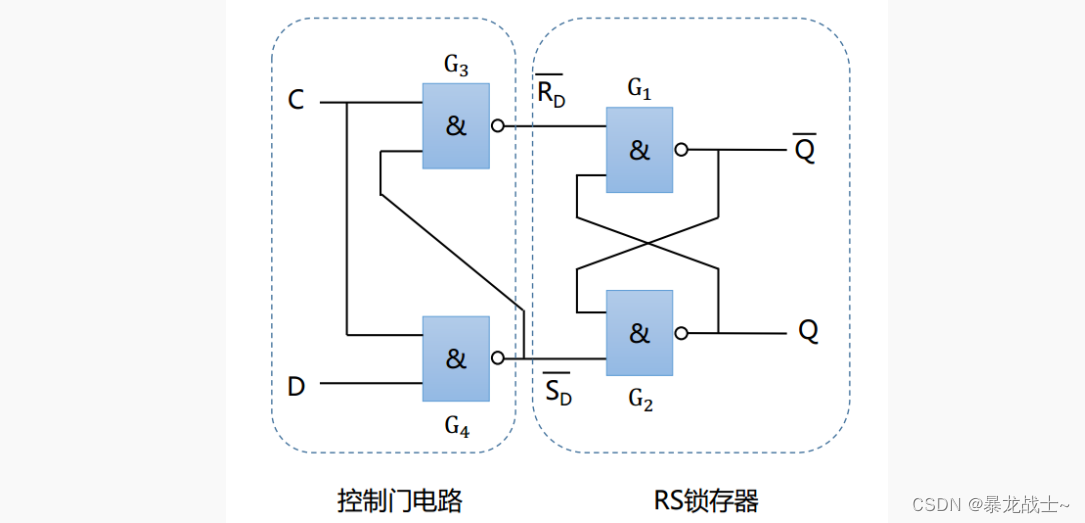

2.锁存器的结构

下面用D锁存器为例子来阐述这个锁存器

基本构成是由四个与非门构成,现在我们假设 C==0,C取0当作输入时候,无论D取任何值 ,Rd和Sd的输出端的输出结果都会是 1,然后当Rd与Sd的结果都为1作为输入的时候,Q与~Q的状态都保持不变。可以理解成起到了锁存的作用,当假设 C==1 ,D==1 ,时根据逻辑电路图可得 SD的状态为0,Rd的状态1,此时Q置1,~Q置数为0. 当C==1 ,D==0,SD为1,RD为0,此时Q置数成1,~Q置数成为0;

从这里看我们看出来,c==0时候,D锁存器是起到锁存的作用,c==1时,此时输出端Q的状态随着输入D的变化而变化,此时D锁存器和D触发器的功能相似。

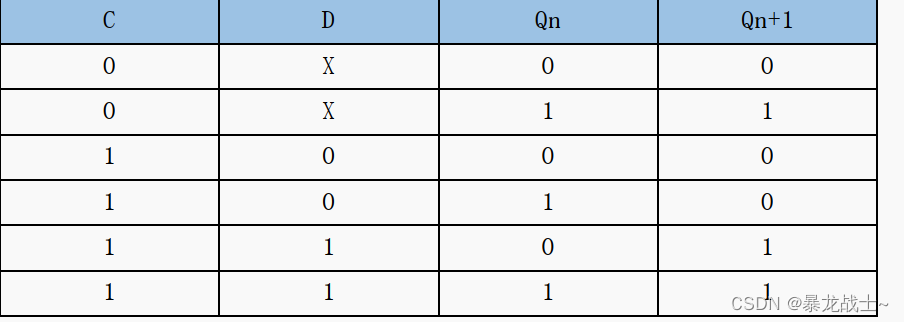

2.1锁存器的特性表

注:Qn表示的是现态,Qn+1表示的是次态:

可以很清楚的从表里看出C==0时刻,次态与现态保持一个状态,当C==1,次态的状态与D的输入保持一致。

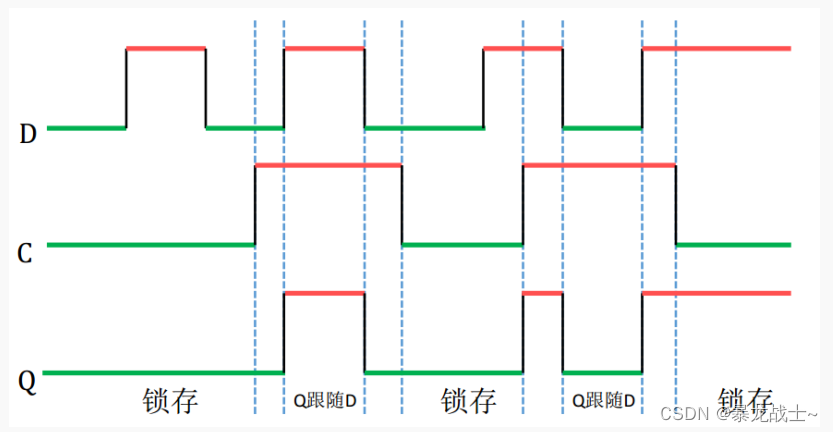

2.2锁存器的时序波形图

可以看出当处于锁存状态的时候,次态与上一个时刻现态的是一致的,高电平还处于高电平,低电平仍然处于低电平。当C拉高时候,Q跟随D;

2.3锁存器在电路设计中产生的危害

1、时序电路设计时候会产生问题

2,不能过滤掉毛刺和影响电路中时序分析工具的运用

3,进行电路设计时应该尽量避免锁存器的运用

3 具体设计例子( if_else结构为例)

//file name : latch.v

//file function : 设计一个锁存器

//file version : 1.0 version

//file date : 2023/3/31

//Author :ZihangNie

//*************************************************

module latch_1 (

//输入信号

input sys_clk ,

input a ,

input b ,

//输出信号

output reg y

);

always @ (*) begin

if ( a == 1 ) //使能1

y = b ;

end

endmodule

注明.文件名和工程名不能直接设置成latch,因为这里可能会与QuartusII中的关键词冲突,设置成

latch_1

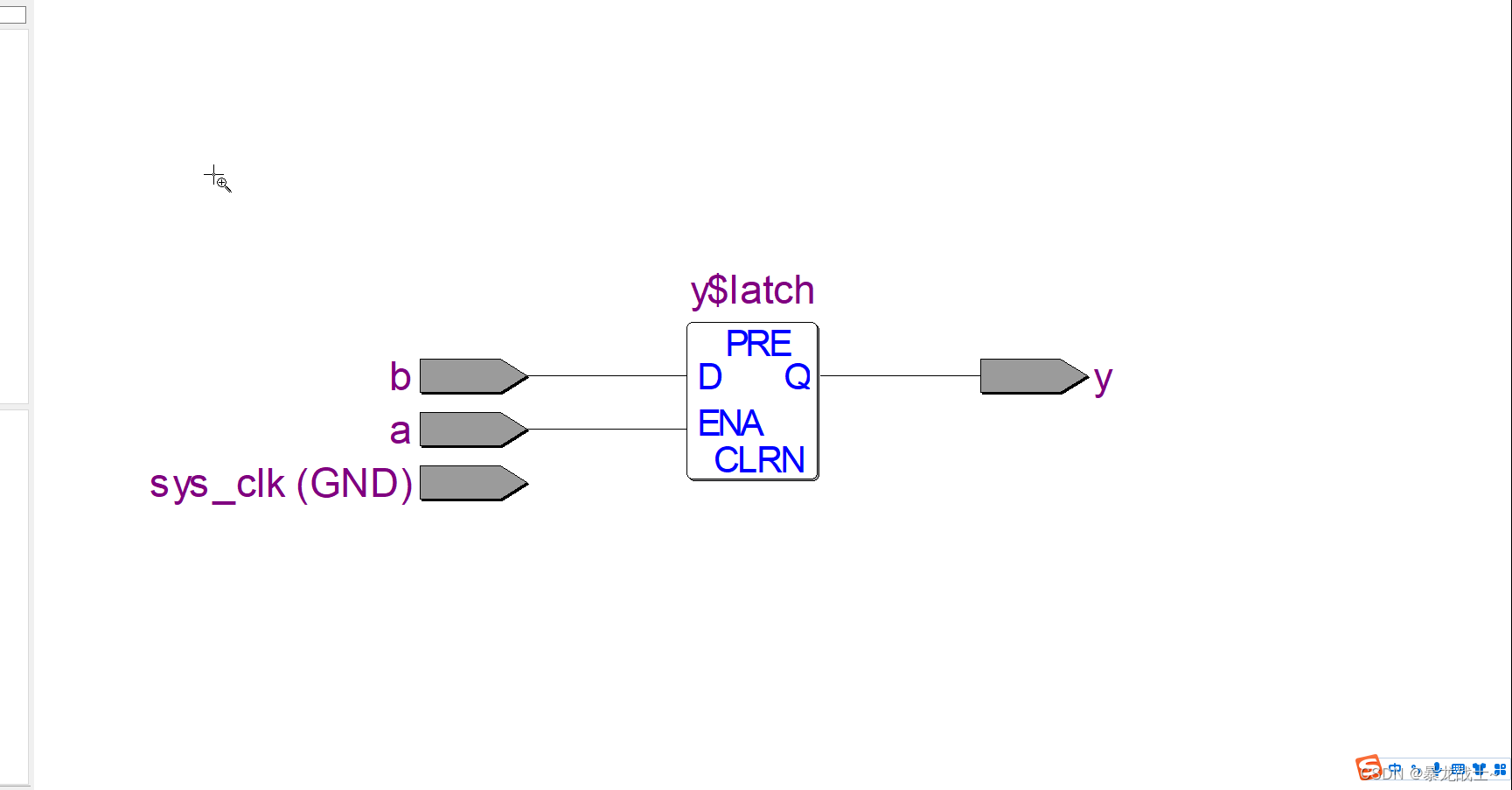

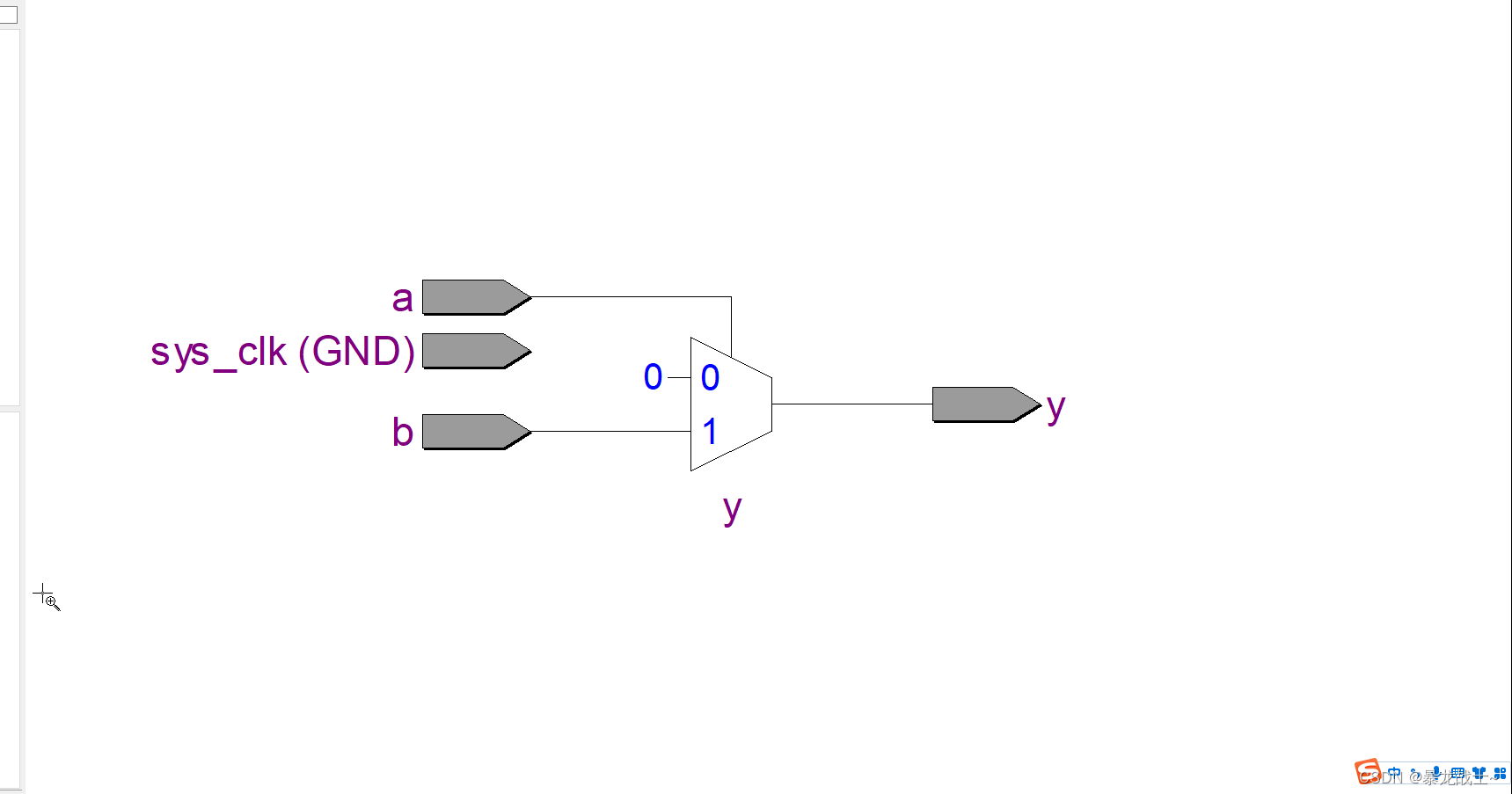

QuartusII RTLviewer观察图

从RTL图中可以产生了latch锁存器,这在电路设计的时候是尽可能要避免的。

//file name latch_2.v

//file function : 消除锁存器带来的电路影响

//file version : 1.0version

//file date :2023\3\31

//Author :ZihangNie

//*********************************************

module latch_2 (

//input signal

input sys_clk,

input a,

input b,

//output signal

output reg y

);

always@(*) begin

if ( a == 1) begin

y = b ;

end

else begin

y = 0;

end

end

endmodule

QuartusII RTLviewer观察图

从RTL图中可见latch锁存器已经消失了,if_else结构中一定一定要记得设计else语句,同时case:语句中也要有default语句,这样做可以很好的避免锁存器的产生!

文章介绍了锁存器的基本概念,以D锁存器为例阐述其结构和工作原理,并通过特性表和时序波形图辅助理解。讨论了锁存器在电路设计中的潜在问题,如时序问题和毛刺影响,并提供了消除锁存器影响的示例代码,强调在if-else结构中使用else语句的重要性。

文章介绍了锁存器的基本概念,以D锁存器为例阐述其结构和工作原理,并通过特性表和时序波形图辅助理解。讨论了锁存器在电路设计中的潜在问题,如时序问题和毛刺影响,并提供了消除锁存器影响的示例代码,强调在if-else结构中使用else语句的重要性。

1605

1605

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?