逻辑门的类型

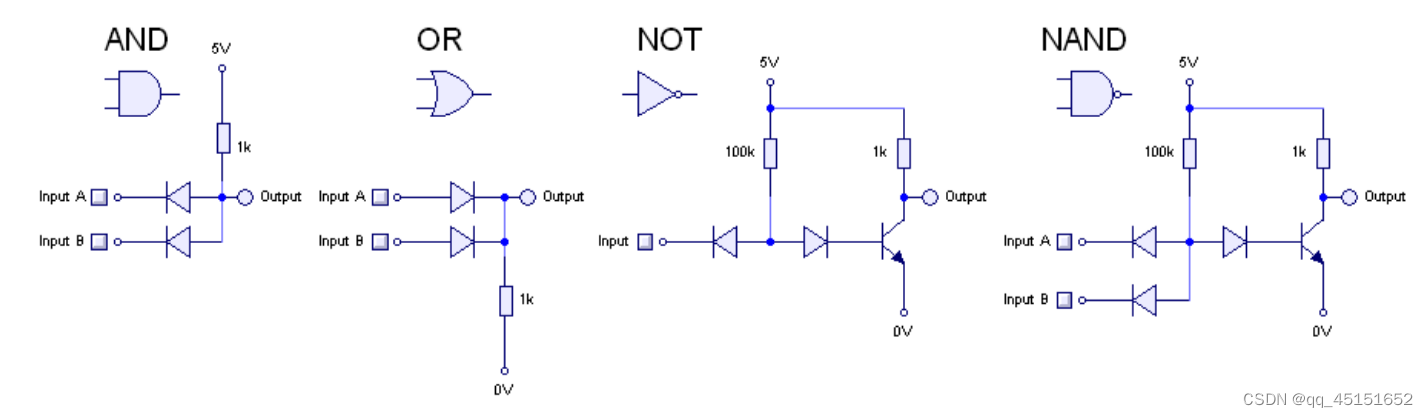

● 逻辑门 – 逻辑电路的基本构建块

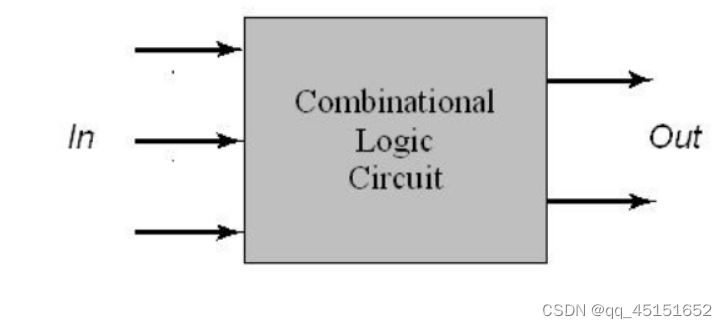

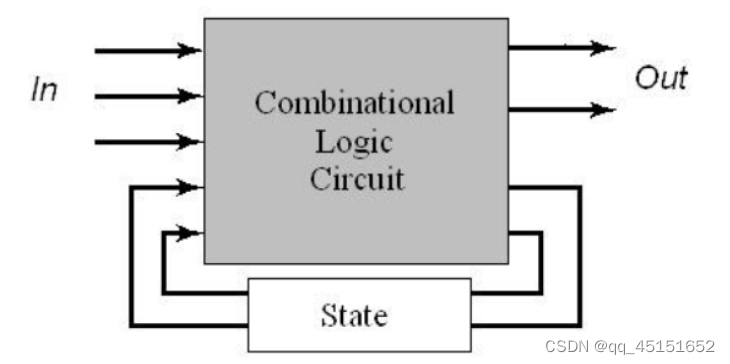

● 两种主要的逻辑类型 – 顺序 sequential 和 组合 combinational

组合combinational Output = f(In)

顺序sequential Output = f(In,Previous In)

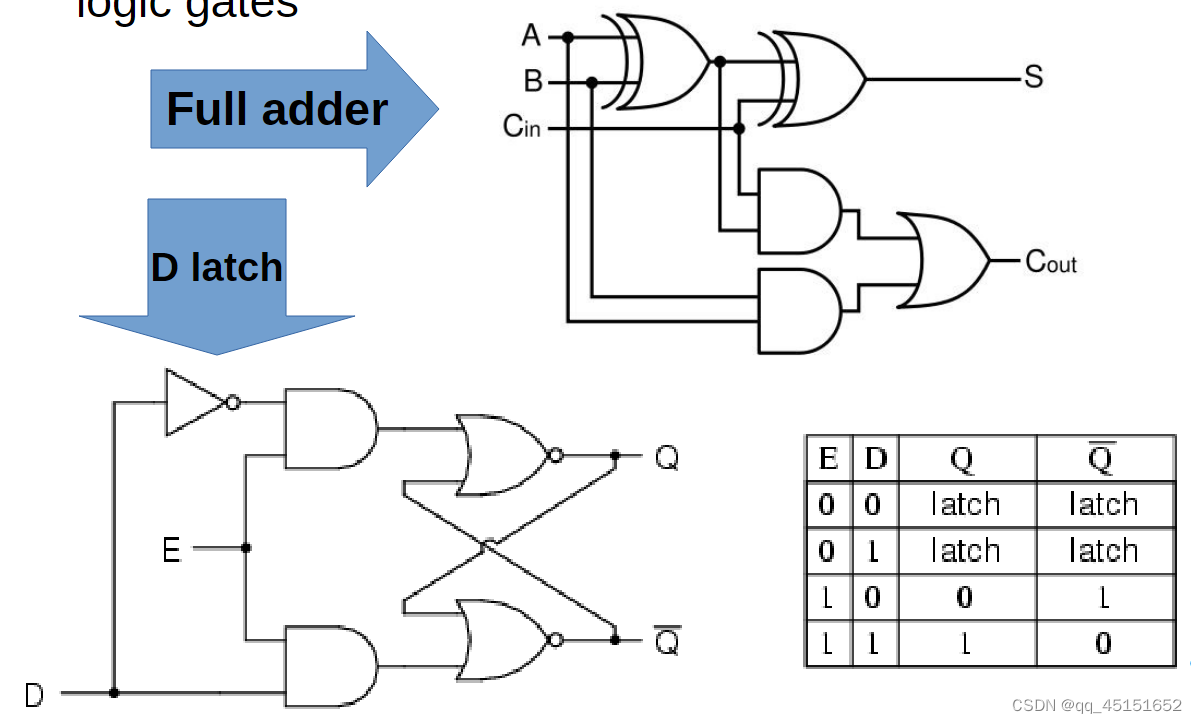

这两种类型的逻辑都可以用简单的基本逻辑门来构建

全加器和D锁存器

IC 数字逻辑系列:

RTL (Resistor-transistor logic)电阻晶体管逻辑

DTL (Diode-transistor logic)二极管晶体管逻辑

TTL (Transistor-transistor logic)晶体管-晶体管逻辑

ECL(Emitter-coupled logic)发射极耦合逻辑

MOS (Metal-oxide semiconductor)金属氧化物半导体

CMOS (Complementary metaloxide semiconductor)互补金属氧化物半导体

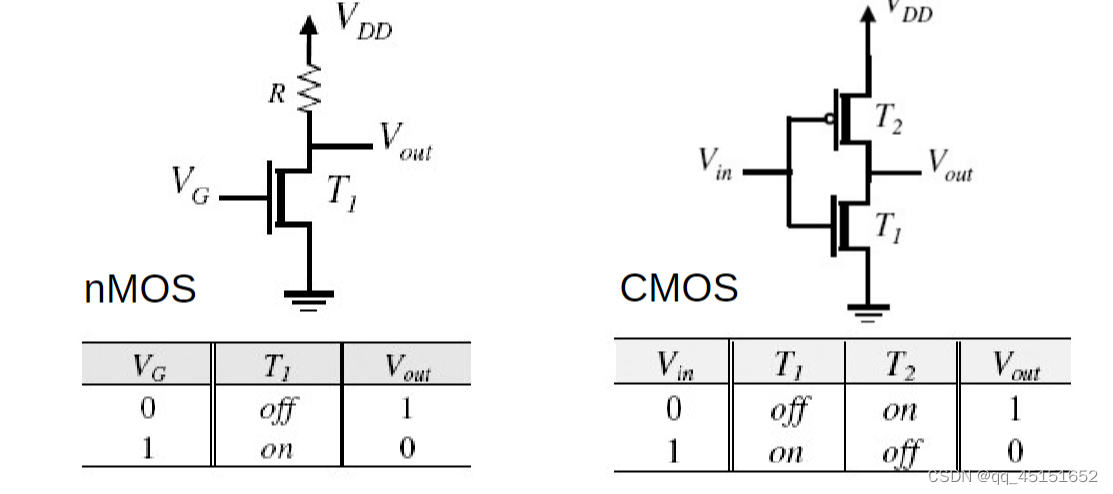

MOS晶体管作为开关

● 所有逻辑门都可以使用无源/有源元件(电阻器、二极管、电容器)构建

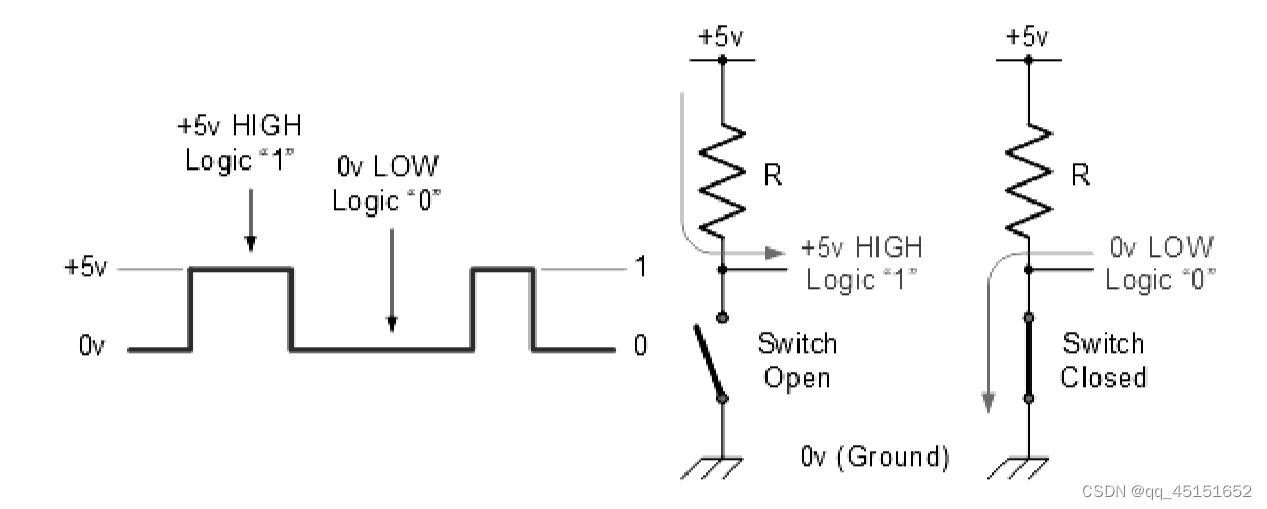

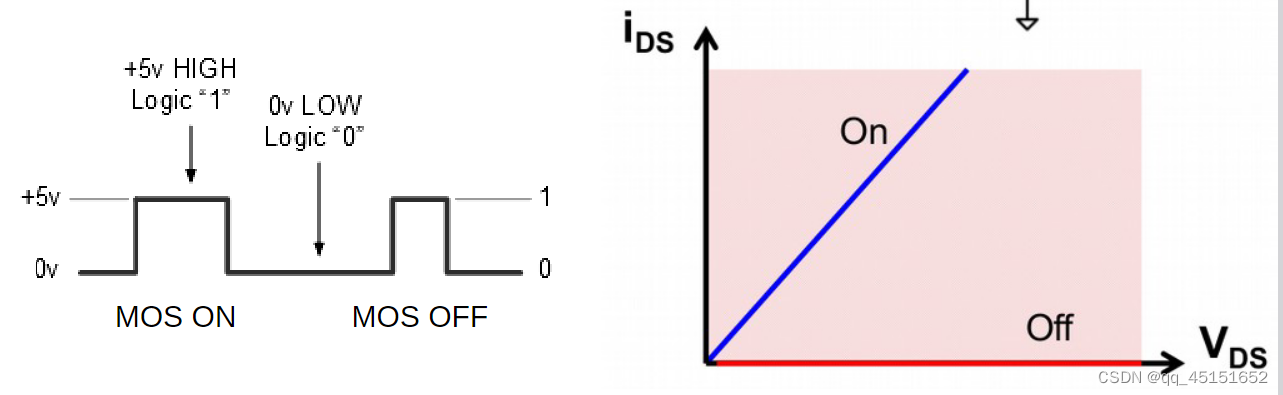

● 关键思想:将 n-MOS 晶体管视为开关;

示例 -> n-MOS 反相器

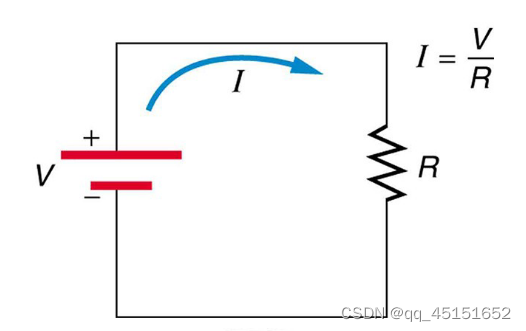

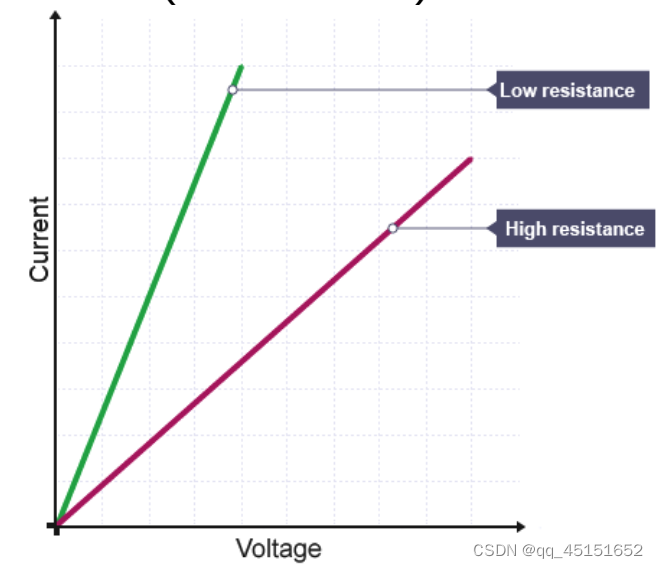

I-V 曲线示例 – 电阻器(欧姆定律):

●电流类似于水流;电阻就像水龙头一样工作。高电阻(水龙头关闭)导致低电流(水流)

● 电阻越高 - I-V 特性的斜率越高

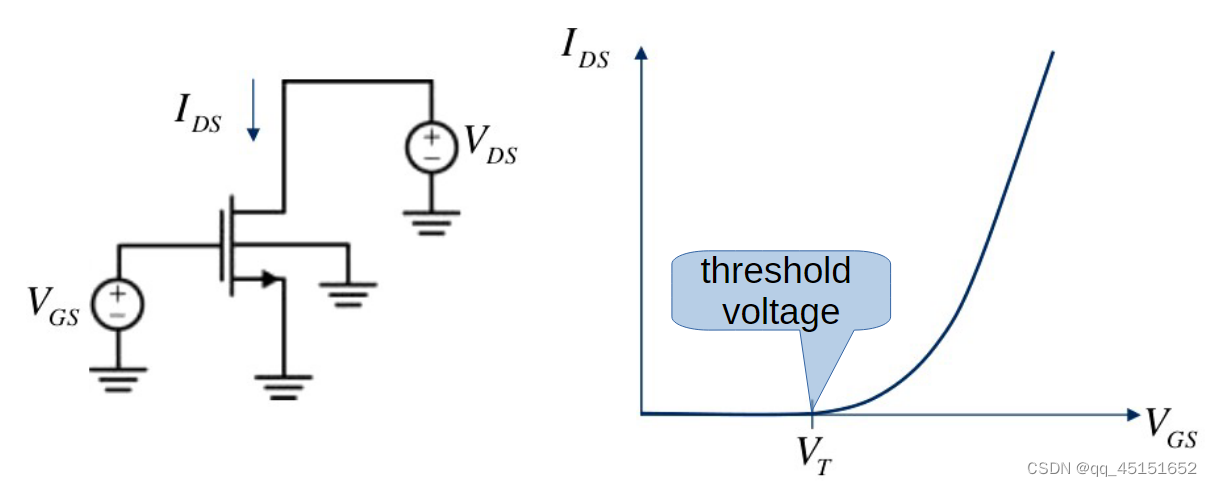

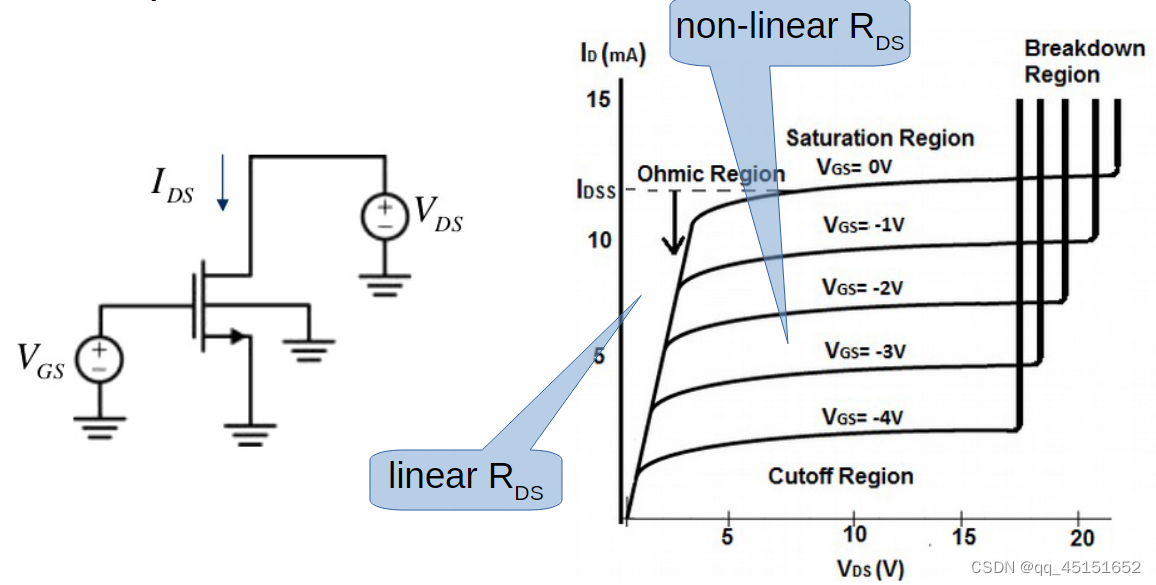

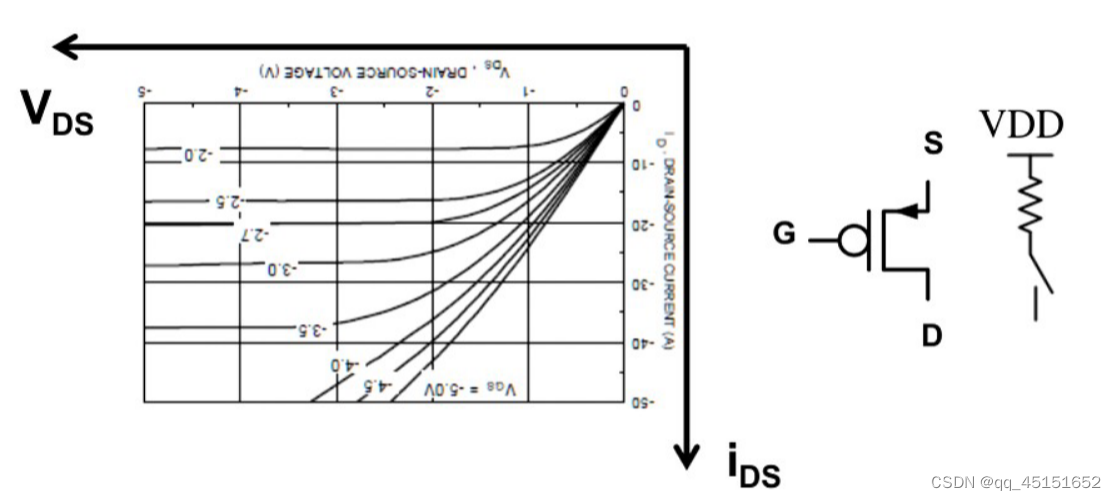

n-MOS管的I-V曲线:

(VGS<VT)->IDS~0;晶体管闭合

(VGS > VT) -> IDS >> 0;晶体管开路

threshold voltage 阈值电压

p-MOS的曲线与之类似(只是反转电源极性)

●对于低 VDS MOS 晶体管充当线性 RDS

● 对于高 VDS MOS 晶体管充当非线性 RDS

如果是这样,我们可以将 MOS 建模为可控 R!

n-MOS:

source = GND

- gate = GND -> VT off

- gate = VDD -> VT on

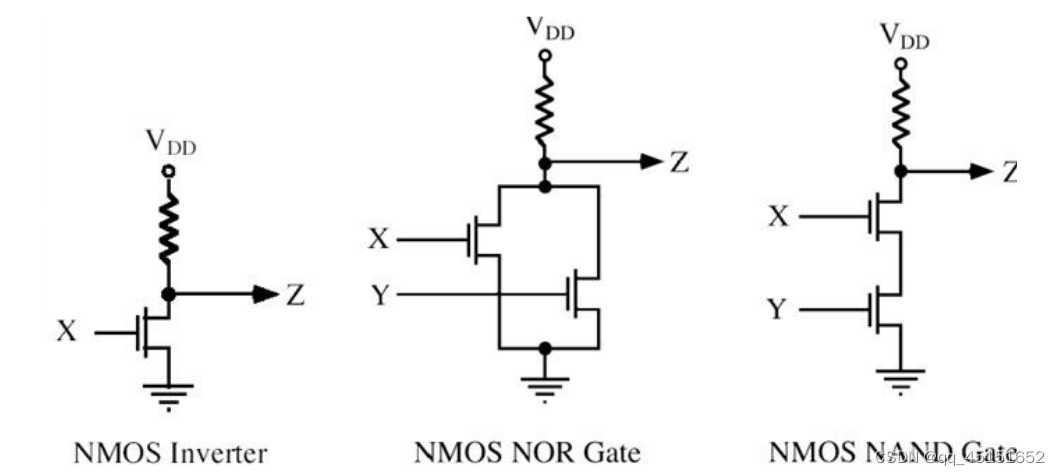

N-MOS 逻辑:示例

n-MOS vs CMOS

● n-MOS 适用于源极= GND 的原理图

● 如果我们想使用源极= VDD -> p-MOS 而不是n-MOS 的原理图

● 对于p-MOS VDS (VD-VS) 应该是负的。

● 所以,p-MOS和n-MOS是互补的

● n-MOS 逻辑:当 nMOS 打开时,静态直流电流从电源 VDD 流向 GND

● 解决方案:互补 MOS (CMOS) 逻辑

● 互补Complementary:具有互补上拉(p 型)/下拉(n 型)部件

● 无静态电流,速度相对较快(低欧姆 VT 通道)

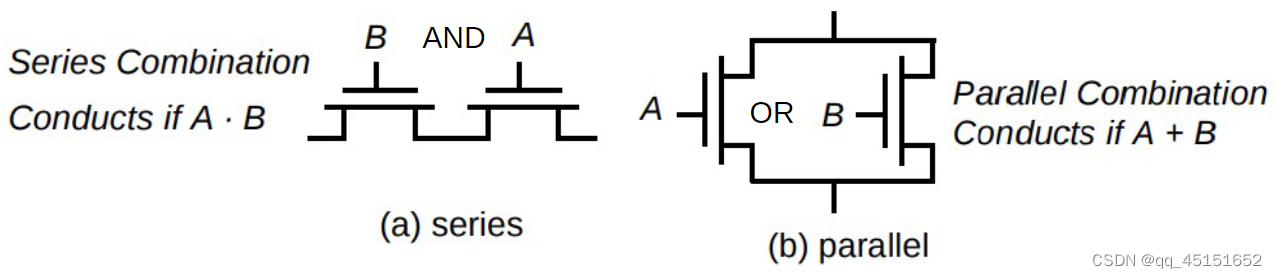

CMOS逻辑规则

● CMOS 逻辑包括上拉和下拉网络 (PUN/PDN) pull-up and pull-down network

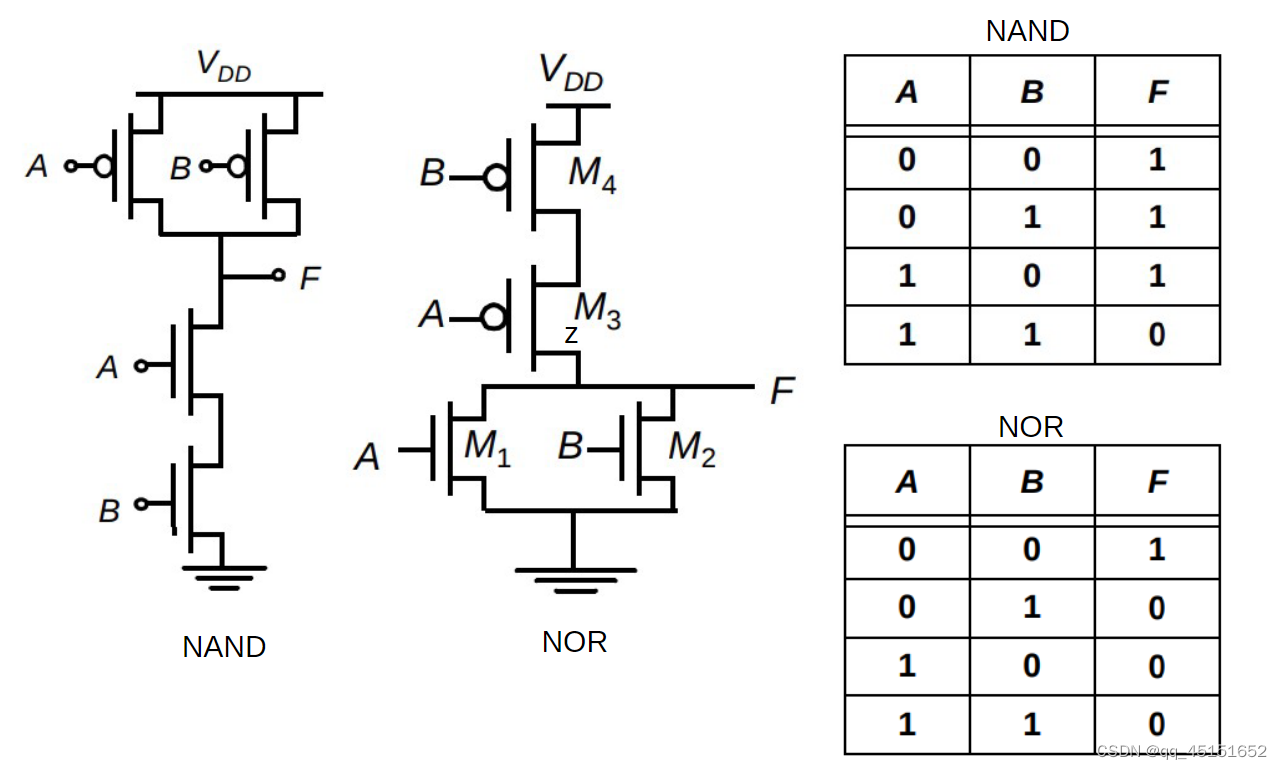

● NMOS PDN:串联 – AND、并联 – OR

pMOS PUN:串联 – NAND、并联 – NOR

PUN 中的晶体管并联 == 串联PDN 中的相应设备,反之亦然。

● 为了构建 CMOS 门,其中一个网络(例如 PDN)是使用串联和并联器件的组合来实现的。另一个网络(即 PUN)是使用对偶原理获得的

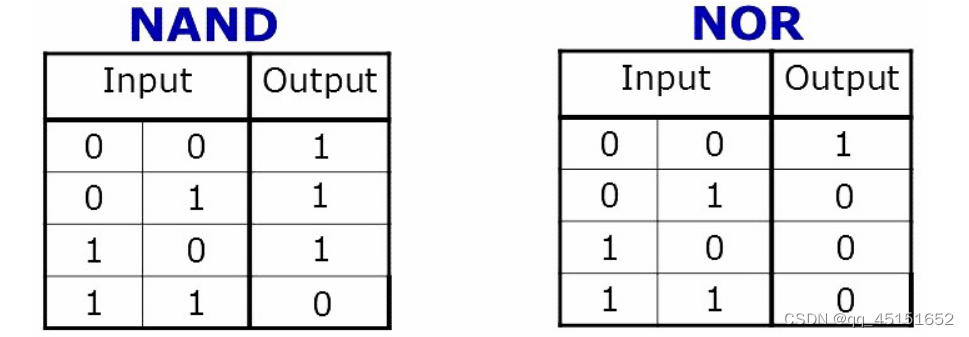

CMOS 逻辑示例 – NAND、NOR

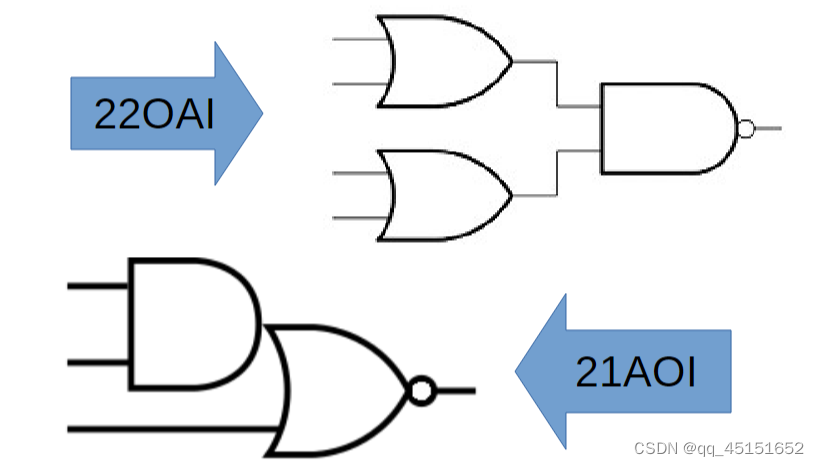

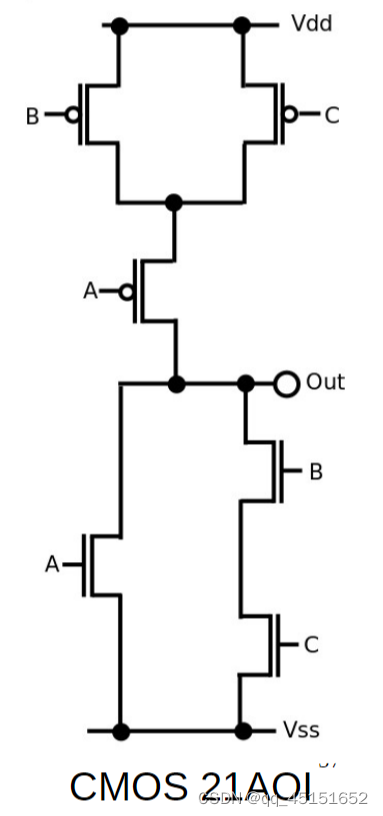

CMOS 逻辑示例 – AOI、OAI

● 通用复杂逻辑门“AND-OR-INVERT/OR-AND-INVERT”

● 可3路输入(21OAI、21AOI)、4路输入(22OAI、22AOI)等

● VT比单独实现小

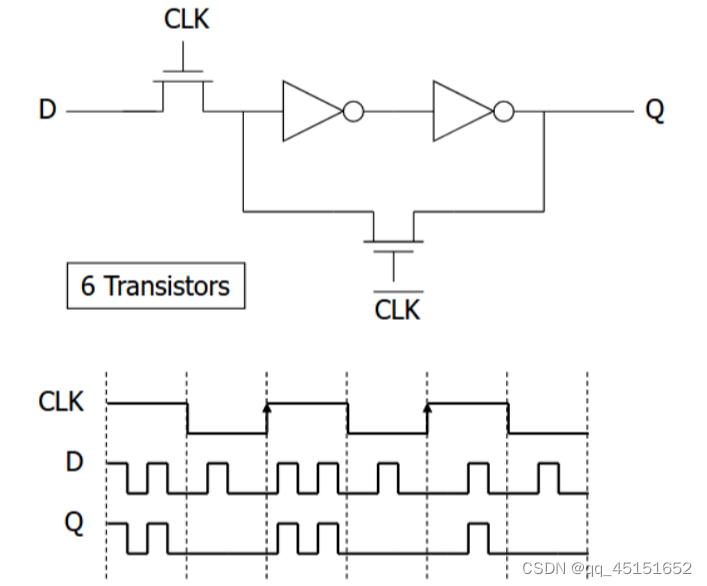

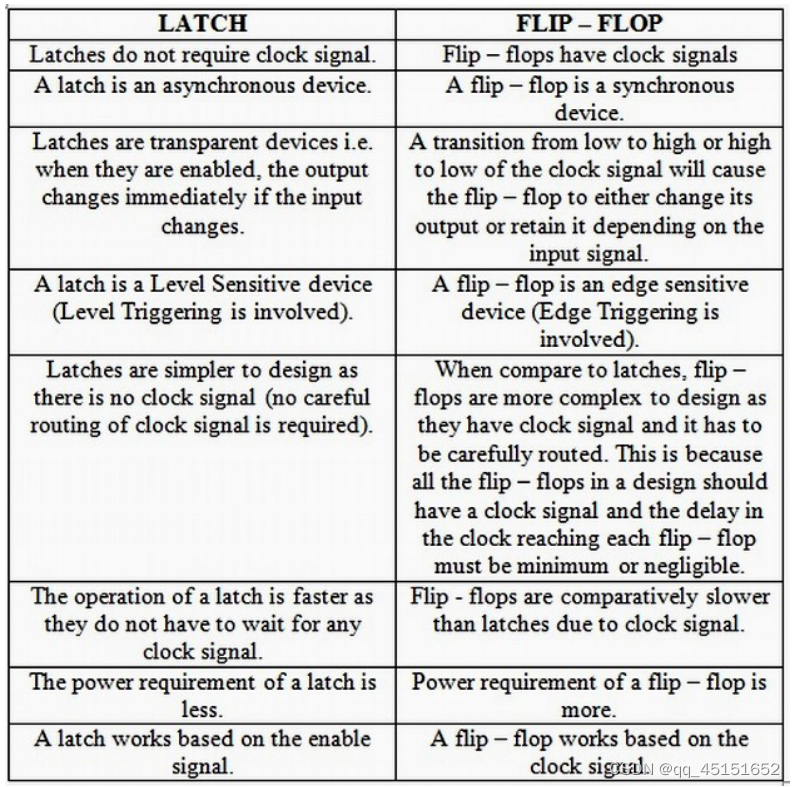

CMOS 逻辑示例 – D 锁存器(电平敏感)

● 当 CLK 处于活动状态(即高电平)时,锁存器是“透明的transparent”(D → Q)

● 当 CLK 处于非活动状态(低电平)时,在 Q 输出端保持 D 值

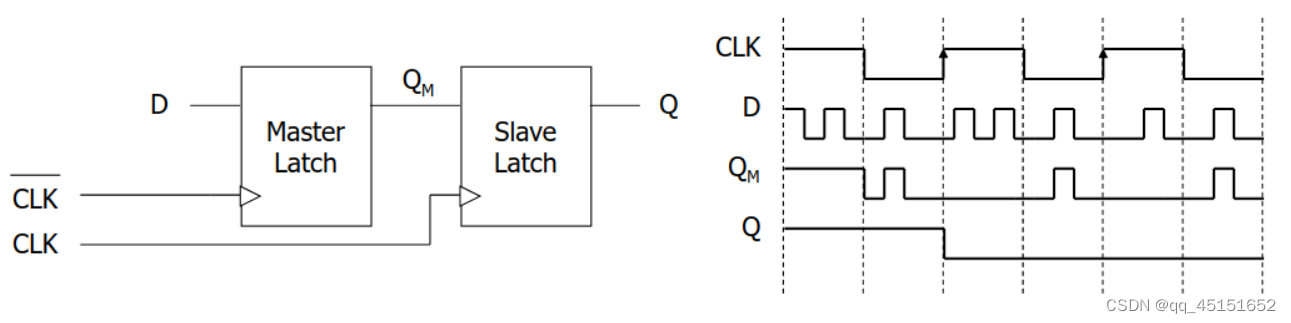

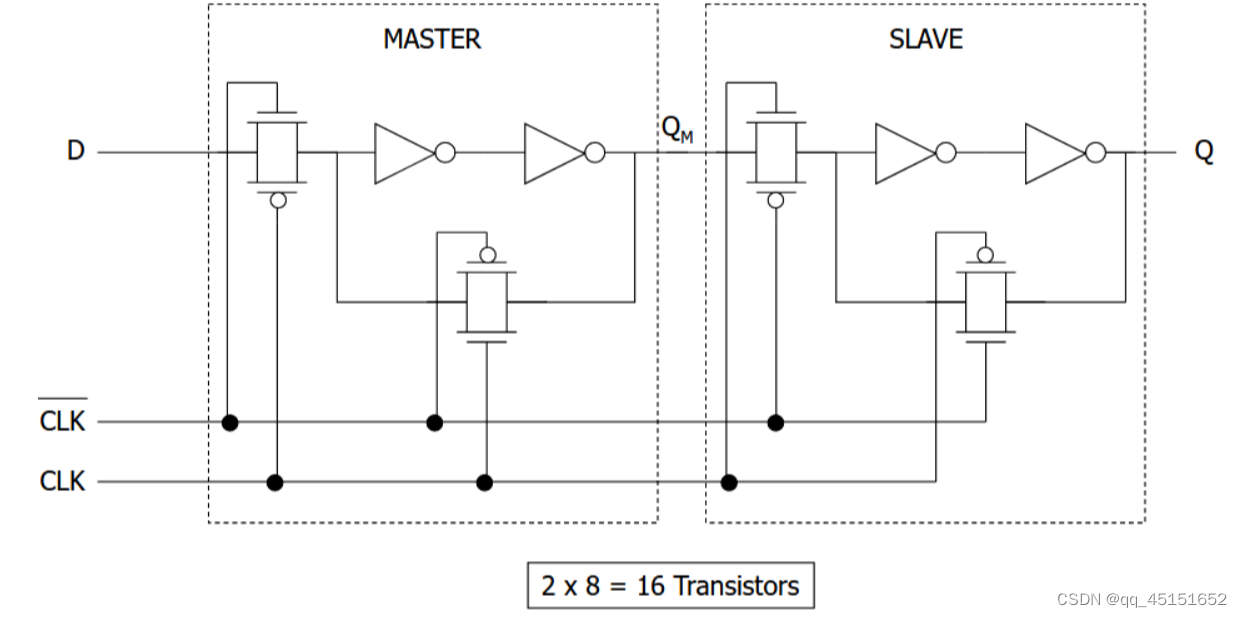

CMOS 逻辑示例 - D 触发器(边沿敏感)

● 在 CLK 的上升沿捕获(“采样”)D 输入并在 Q 输出上传播其值

● 保持 Q 输出上的 D 值直到下一个 CLK 边缘

● 最常用的顺序设备

基于两个串联的 D-latch 单元

CMOS 逻辑示例——触发器vs锁存器

4851

4851

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?