CMOS逻辑电路

目 录

PMOS管和NMOS管

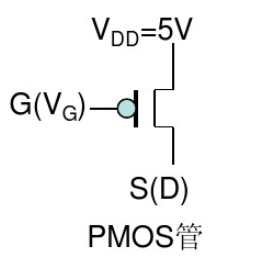

PMOS,指的是利用空穴來传导电性信号的金氧半导体。PMOS的电路符号如下图,而其结构则如右图所示,是由正型掺杂形成的漏极(drain)及源极(source),与闸极(gate)及闸极下面的氧化层所构成。

PMOS的特性,Vgs小于一定的值就会导通,适合用于源极接VCC时的情况(高端驱动)。但是,虽然PMOS可以很方便地用作高端驱动,但由于导通电阻大,价格贵,替换种类少等原因,在高端驱动中,通常还是使用NMOS。

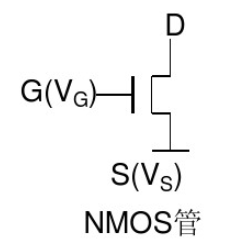

NMOS,指的是利用电子来传导电性信号的金氧半晶体管。NMOS的电路符号如下图,而其结构图如左图所示,是由负型掺杂形成的漏极与源极,与在氧化层上的闸极所构成。

NMOS的特性,Vgs大于一定的值就会导通,适合用于源极接地时的情况(低端驱动),只要栅极电压达到4V或10V就可以了。

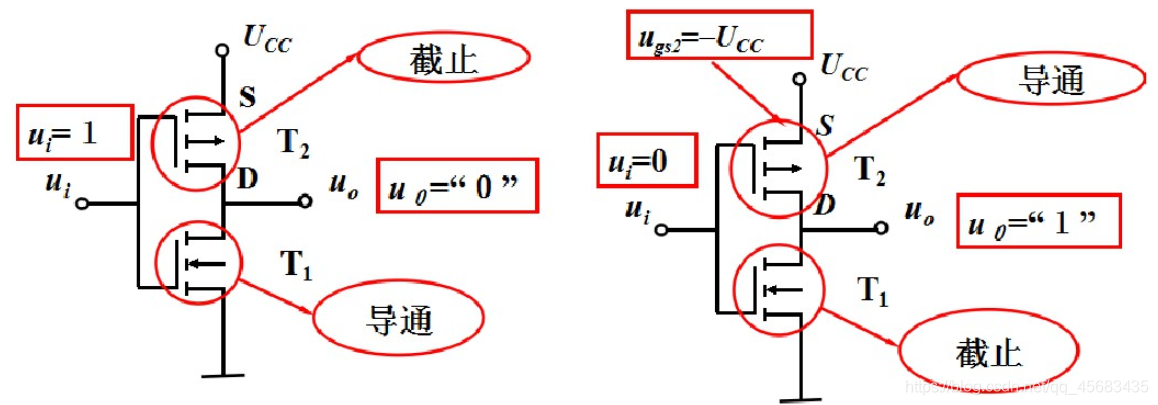

CMOS管

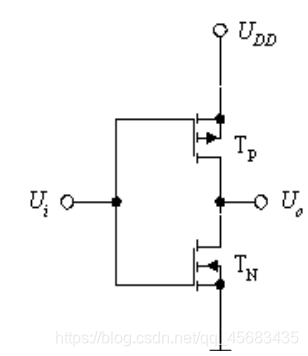

CMOS是Complementary Metal Oxide

Semiconductor(互补金属氧化物半导体)的缩写。CMOS管有NMOS管和PMOS管构成,也称为反相器。具有低功耗,抗干扰能力强特点。

反相器电路,当V-in输入为低电平时,PMOS导通,电容充电,V-out输出为高;当V-in为高电平时,PMOS管截至,NMOS管导通,电容放电,V-out输出为低。

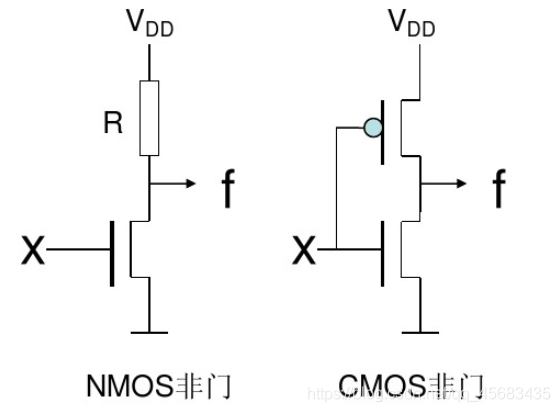

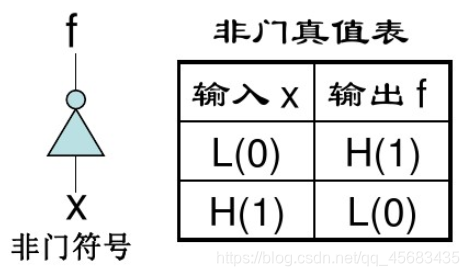

非门

非门对输入信号求反。

NMOS管非门:

输入X为高,NMOS导通,f输出为低。

输入X为低,NMOS截至,f输出为高。

CMOS管非门:

输入X为高,PMOS管截至,NMOS导通,f输出为低。

输入X为低,PMOS管导通,NMOS截至,f输出为高。

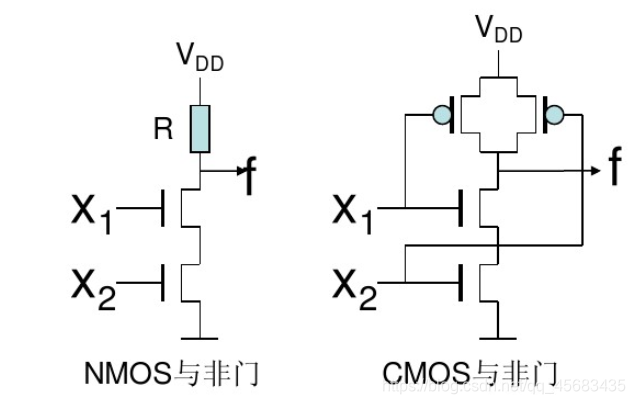

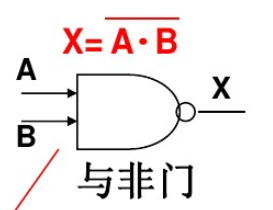

与非门

NMOS管与非门:

输入X1和X2都为高,NMOS导通,f输出为低。

其他情况,X1或X2有一个截至,f输出为高。

CMOS管与非门:

输入X1和X2都为高,两个PMOS管截至,两个NMOS导通,f输出为低。

其他情况,X1或X2有一个截至,f输出为高。

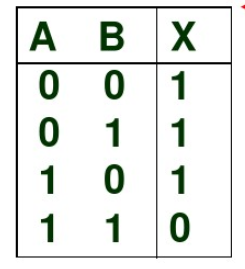

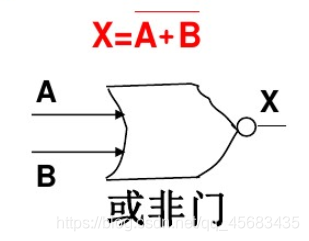

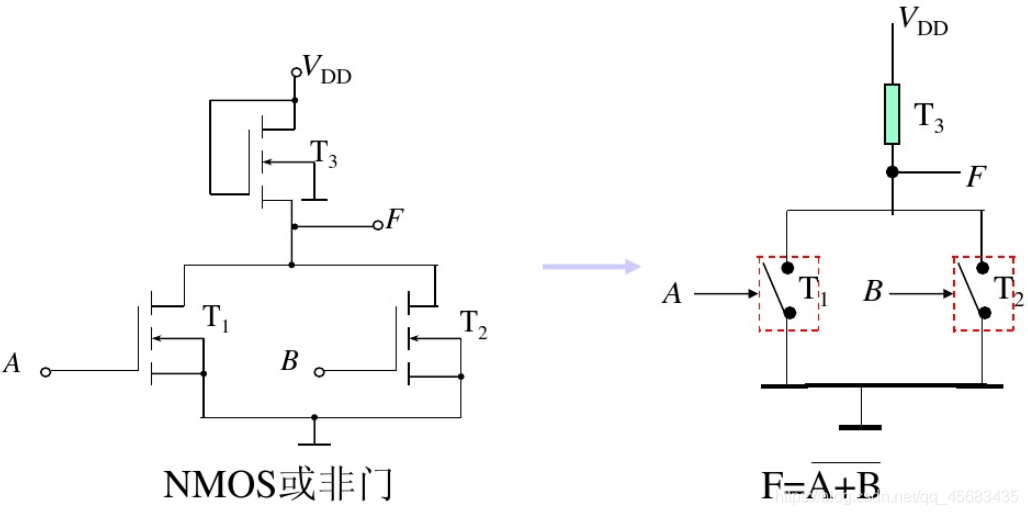

或非门

A和B有一个为1,输出为低。

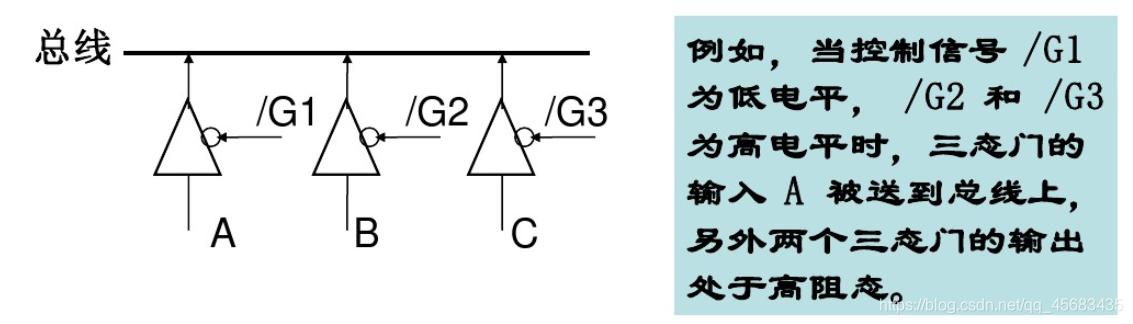

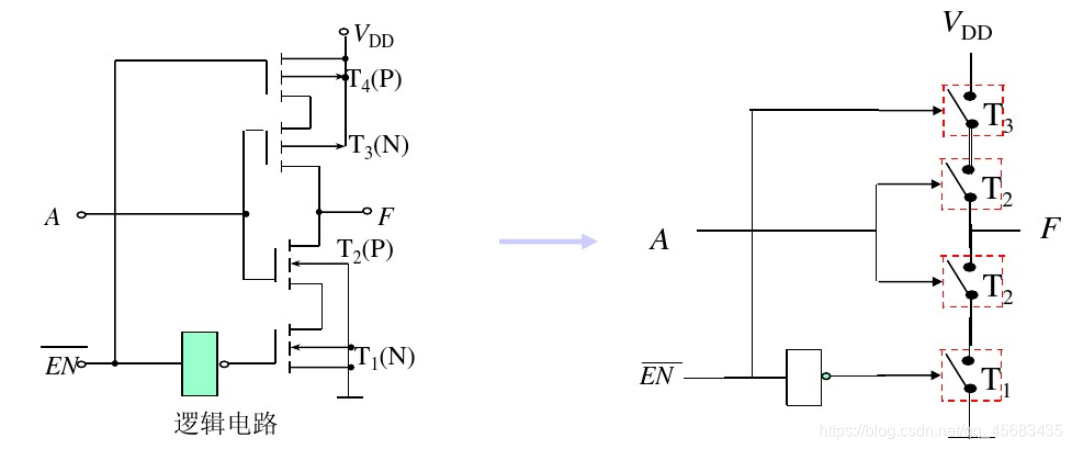

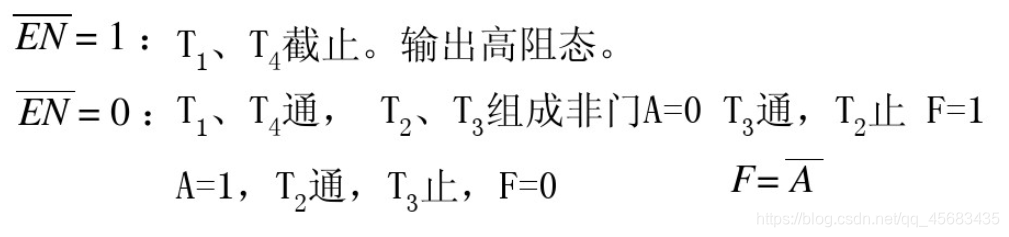

三态门

输出除了0和1,还可以输出高阻态。

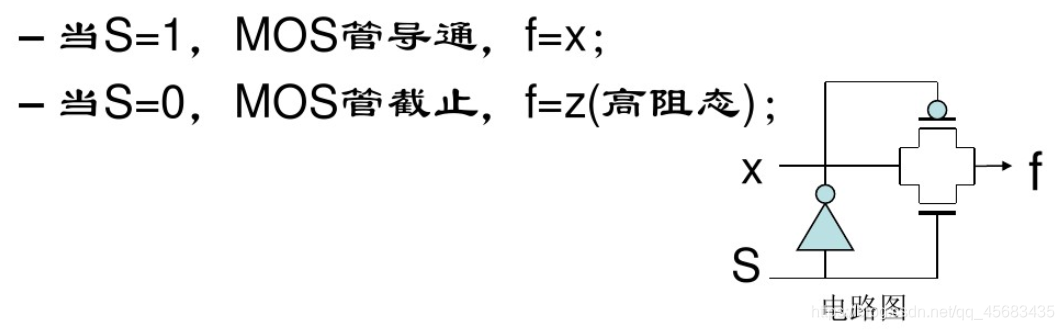

传输门

组合与时序逻辑电路

任何时刻输出仅取决于该时刻输入,没有记忆功能。

时序逻辑电路

任何时刻输出不仅取决于该时刻输入,而且与之前状态有关,有记忆功能。

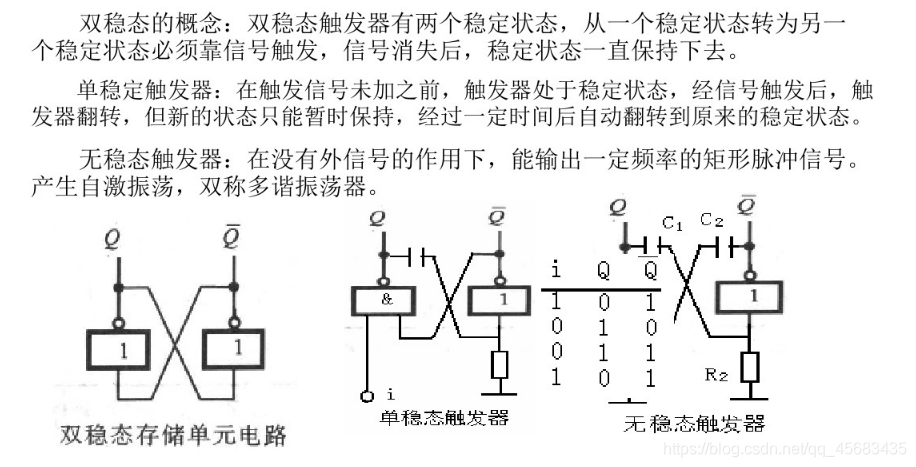

双稳态概念

锁存器和触发器

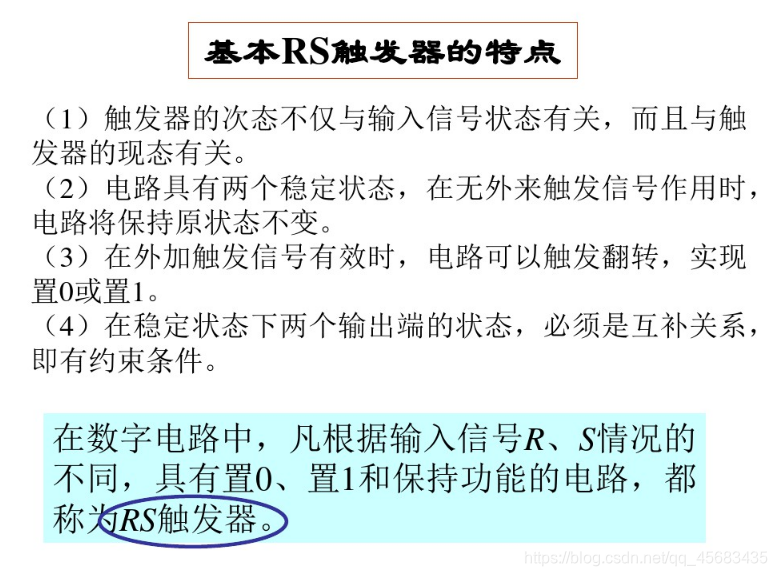

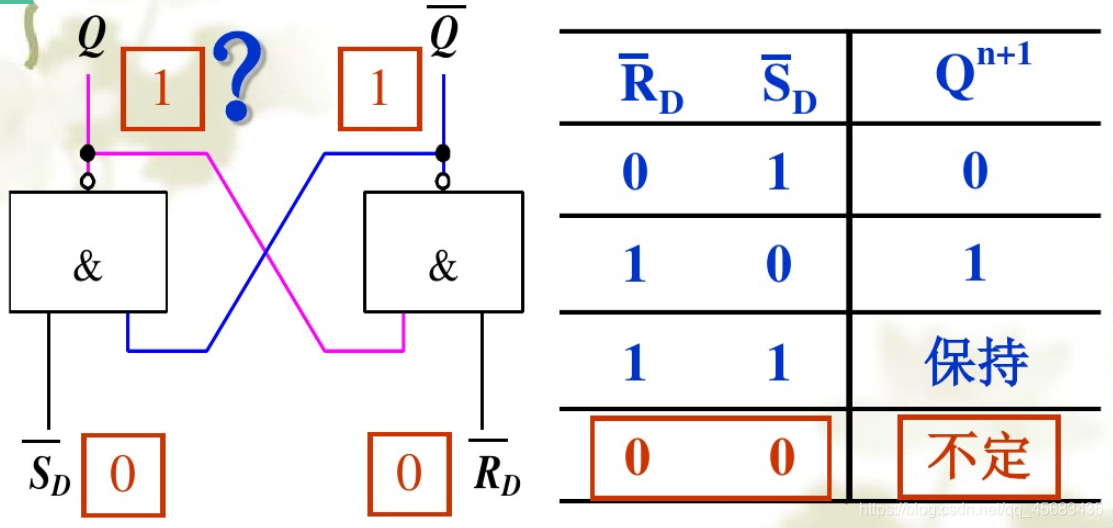

R-S锁存器

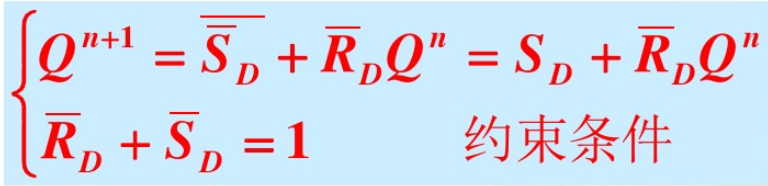

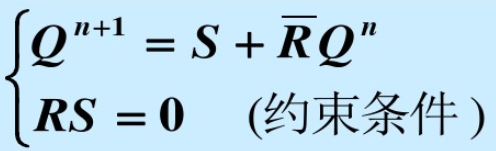

特征方程

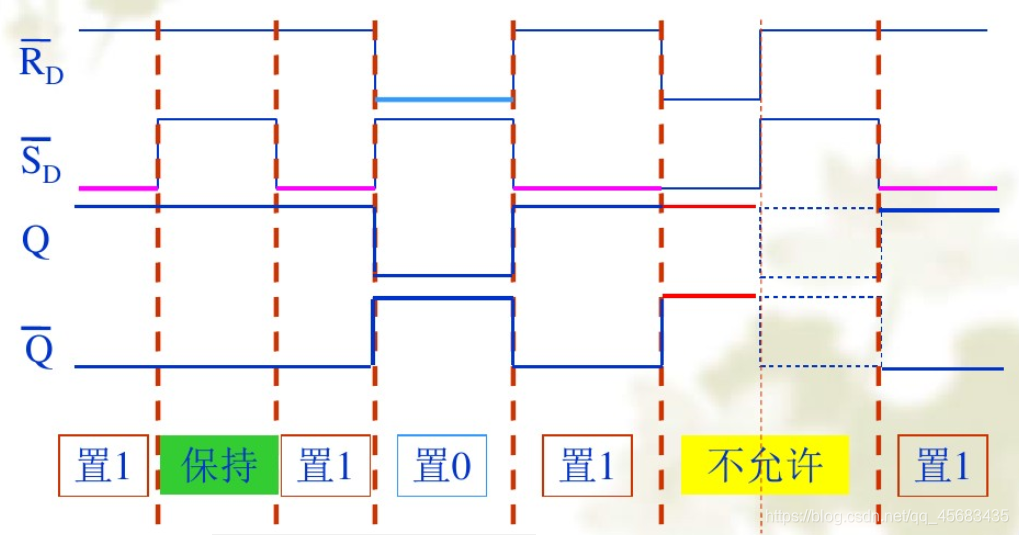

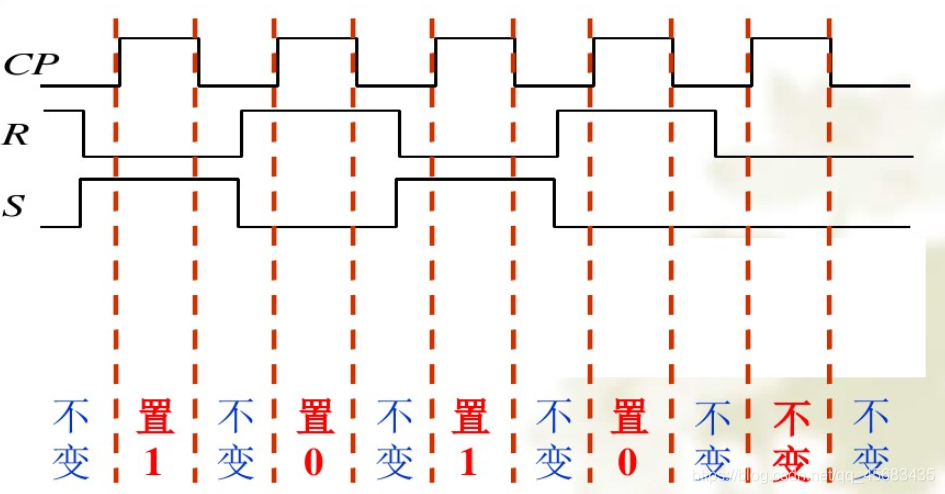

时序图

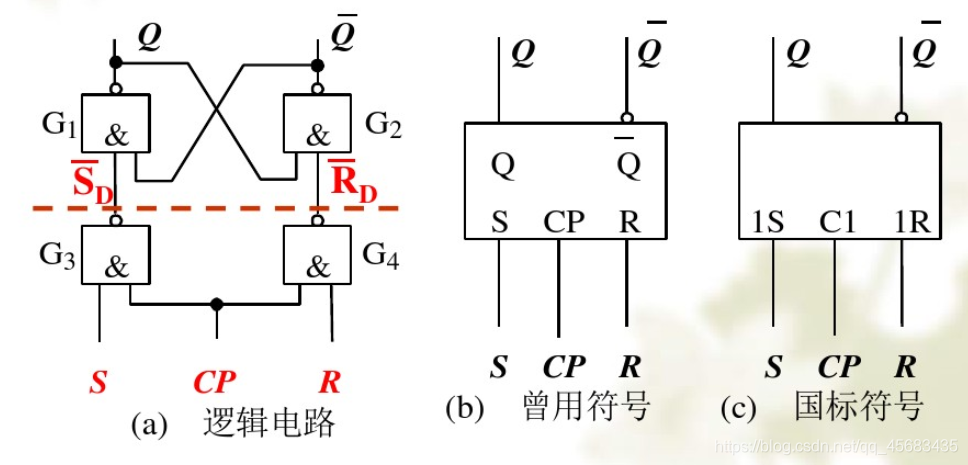

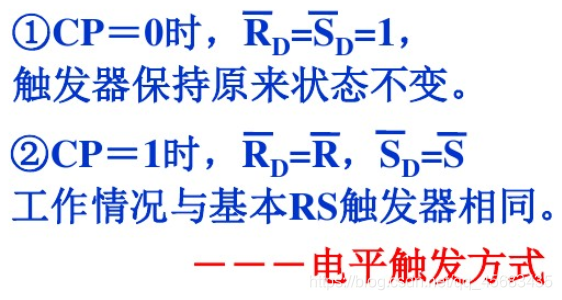

同步RS锁存器

时钟信号到达时,触发器状态才发生变化。

特征方程(CP=1)

真值表(CP=1)

时序图

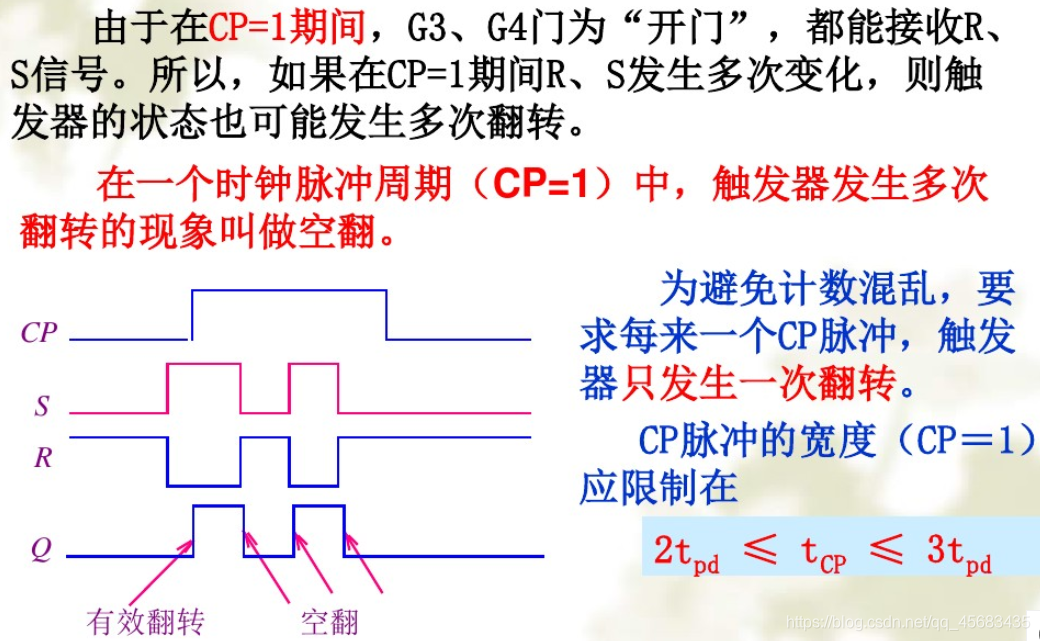

空翻现象

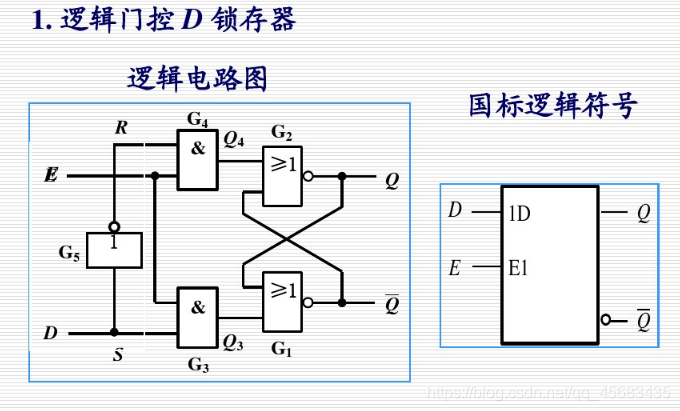

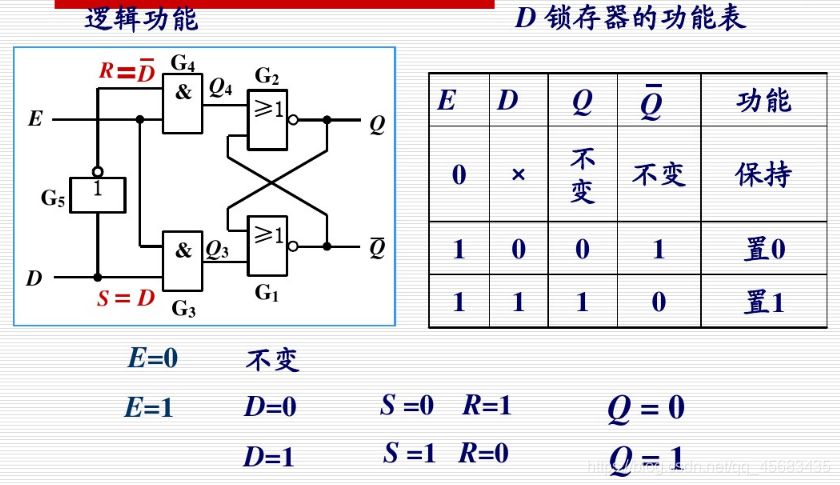

D锁存器

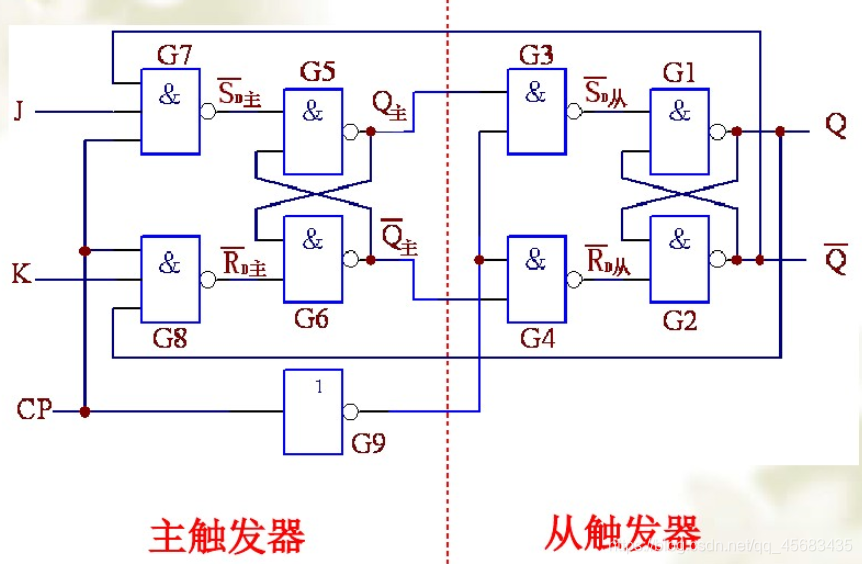

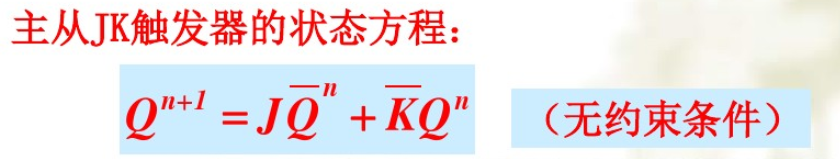

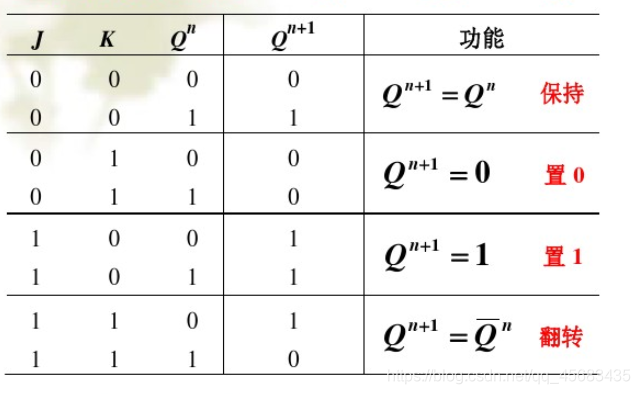

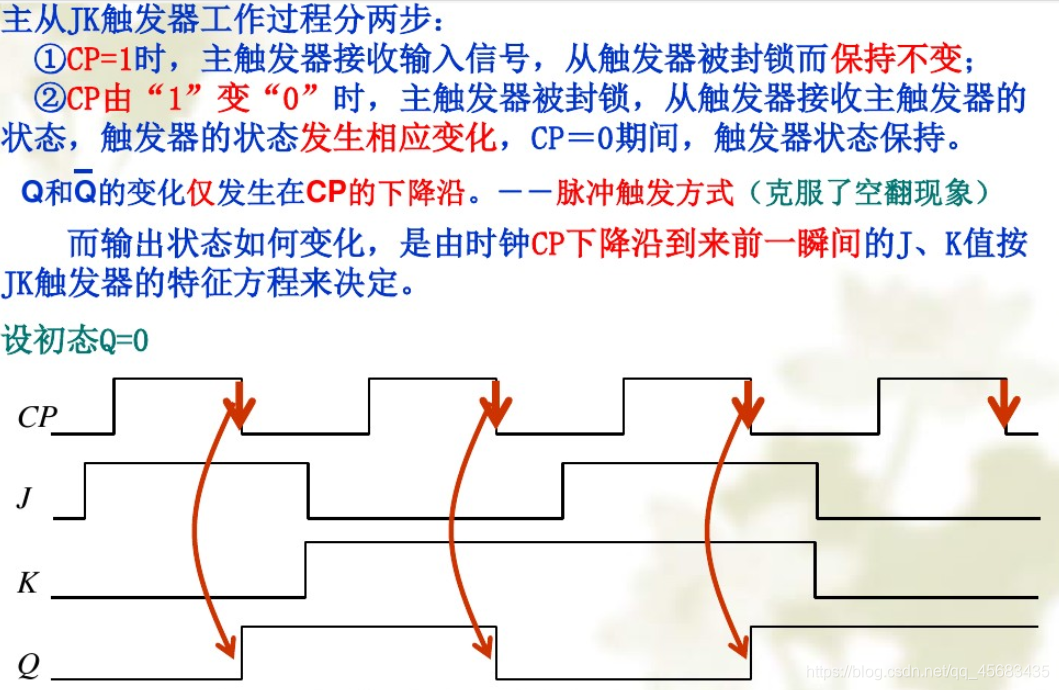

JK触发器

真值表

时序图

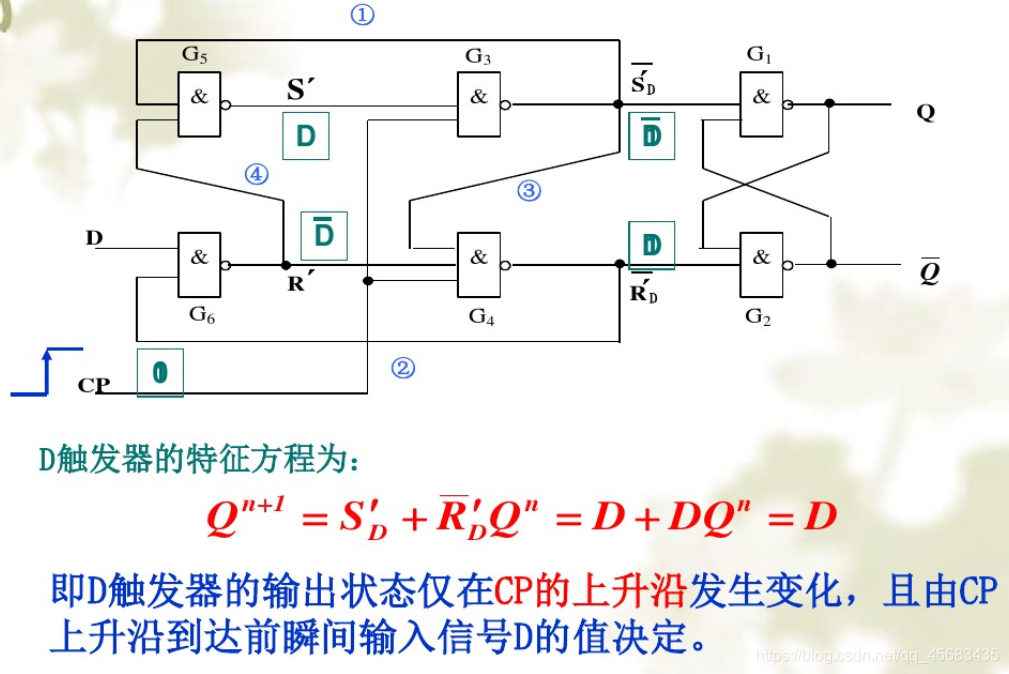

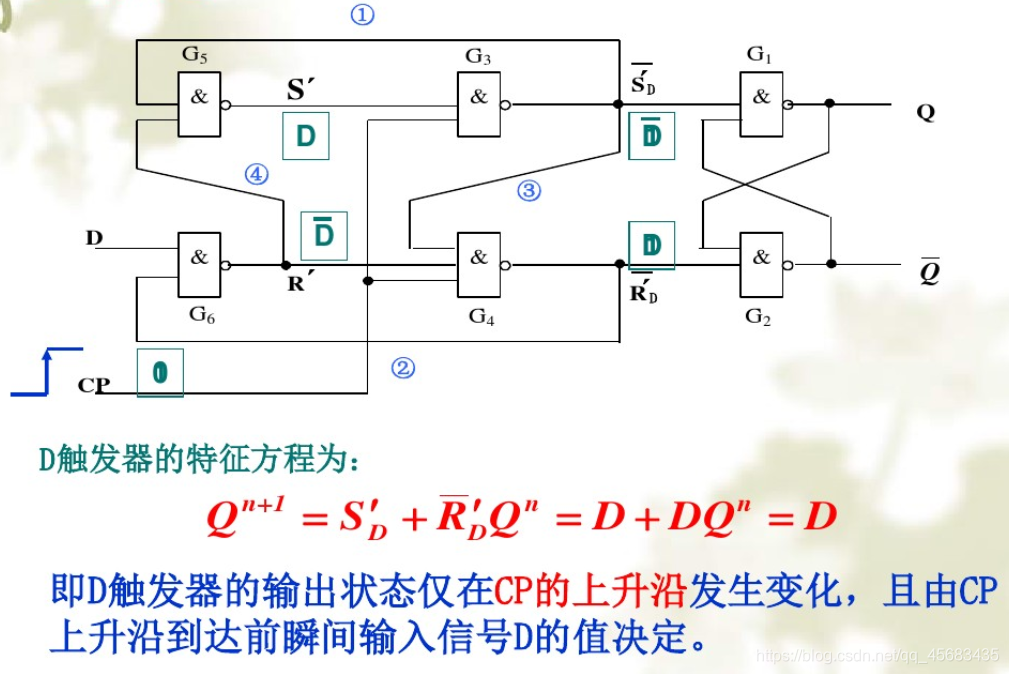

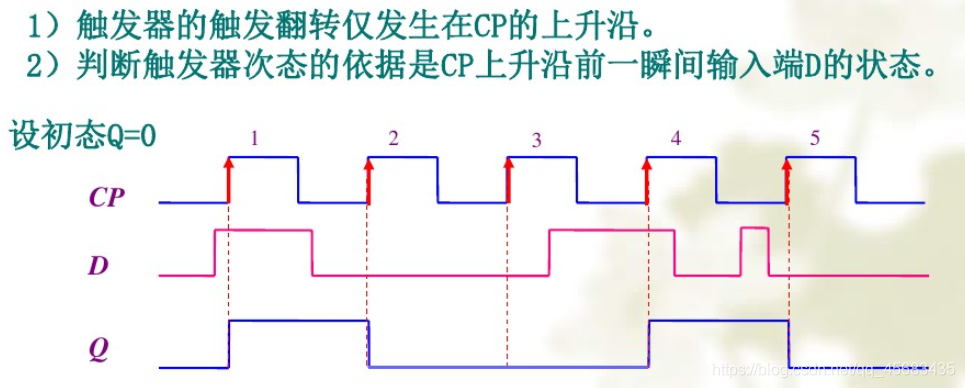

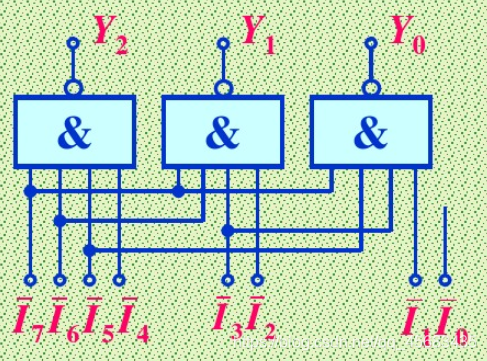

维持阻塞式D触发器

真值表

时序图

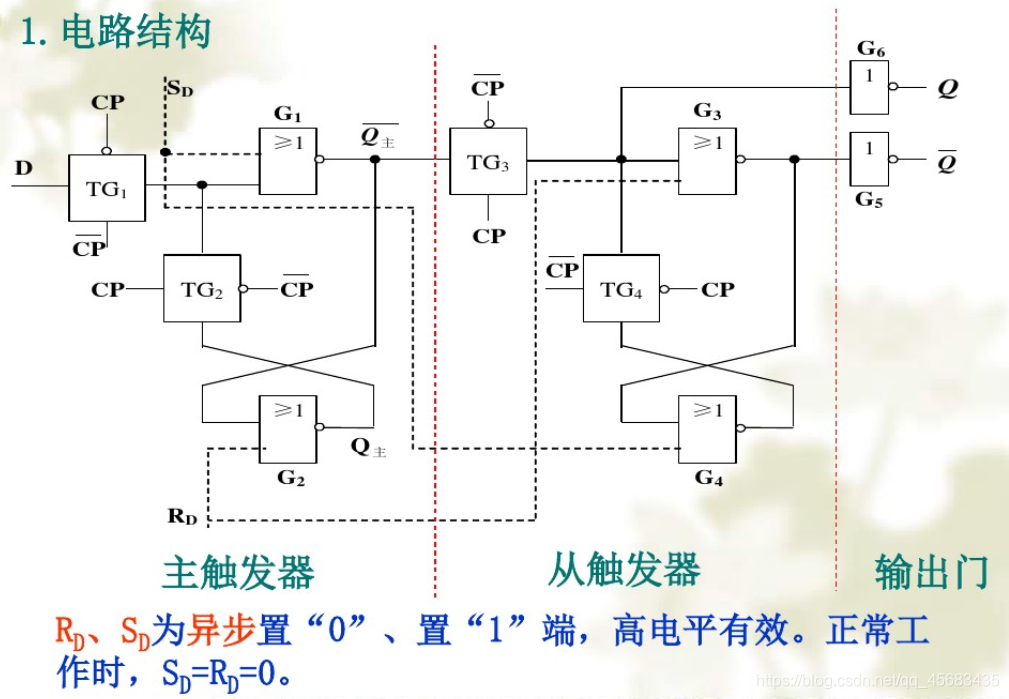

CMOS边沿D触发器

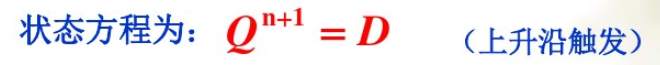

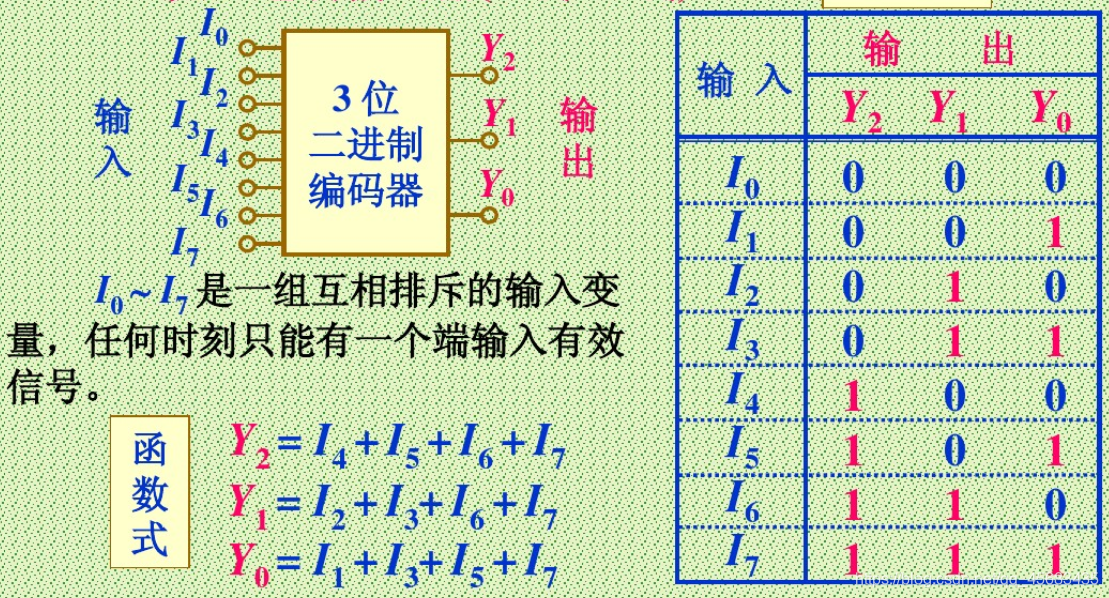

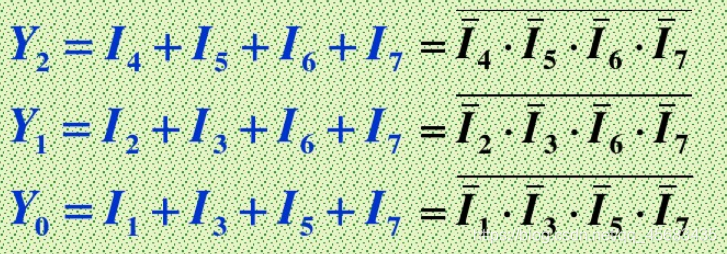

编码器

用n位二进制代码对N=2^N个信号进行编码的电路。

逻辑电路

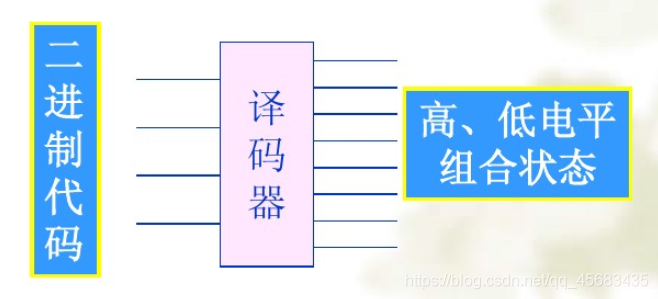

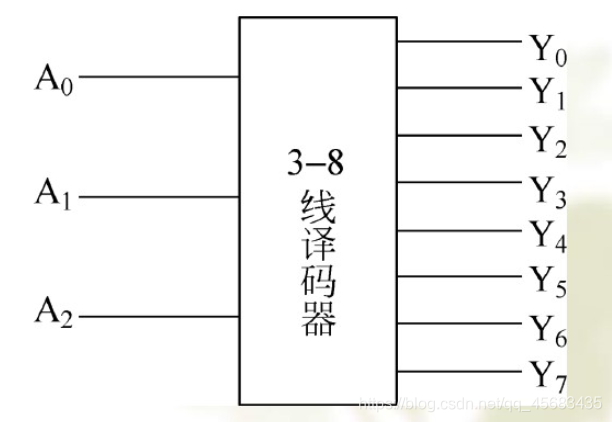

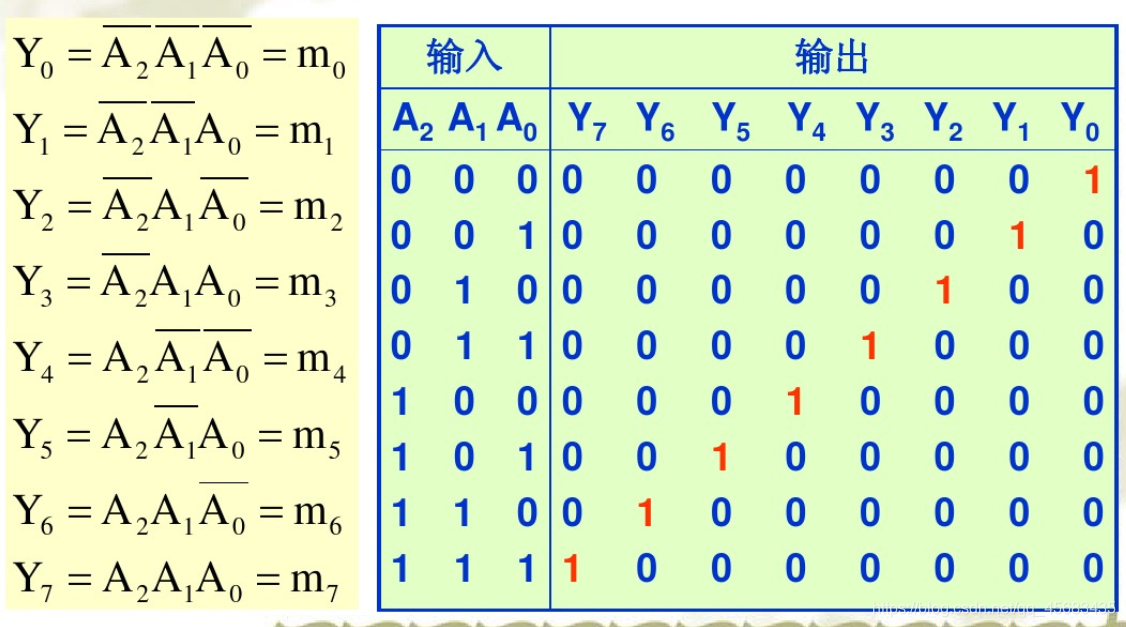

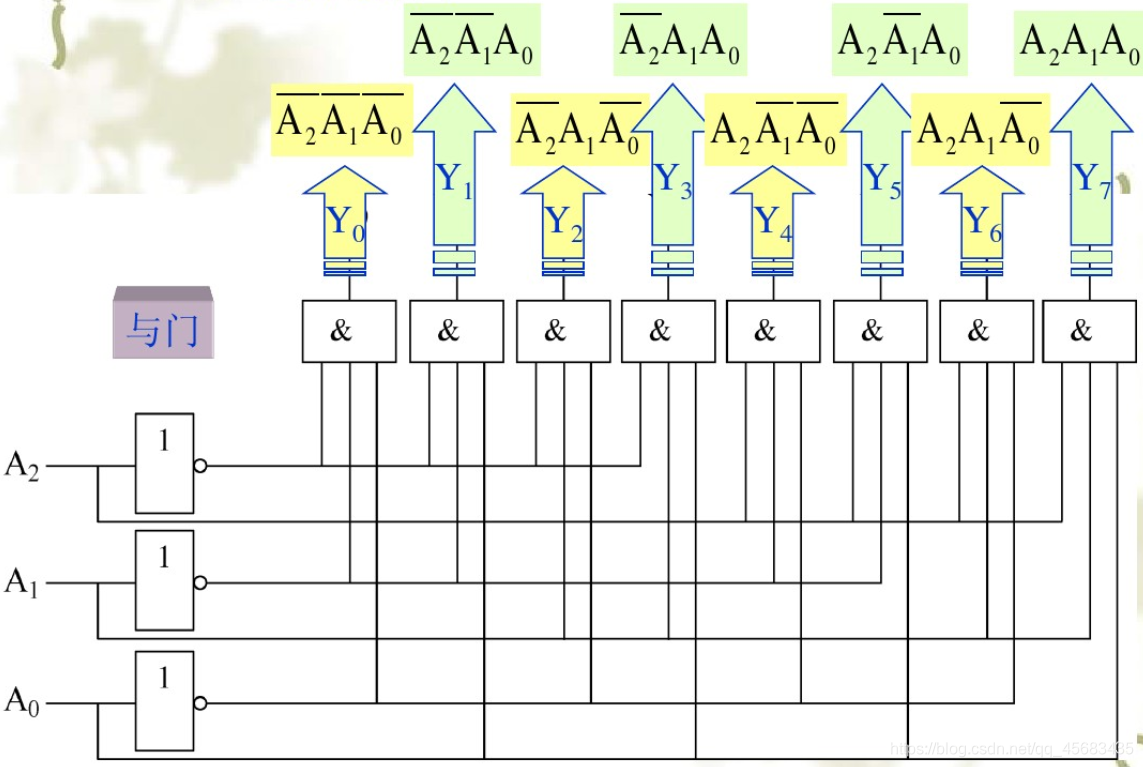

译码器

3-8译码器

逻辑电路

参考:电路基础课件

参考:电路基础课件

2700

2700

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?