储系统综合实验

一、 实验目的

-

熟悉 Logisim 软件平台;

-

熟悉 ROM、RAM 存储器的使用;

-

掌握存储器字扩展,位扩展的基本原理;

-

为 MIPS CPU 设计功能部件—寄存器文件;

二、 实验环境

Logisim 是一款数字电路模拟的教育软件,每一位用户都可以通过它来学习如何创建逻辑电路,方便简单。它是一款基于 Java 的应用程序,可运行在任何支持 JAVA 环境的平台,方便学生来学习设计和模仿数字逻辑电路。Logisim 中的主要组成部分之一就在于设计并以图示来显示 CPU。当然 Logisim 中还有其他多种组合分析模型来对你进行帮助,如转换电路,表达式,布尔型和真值表等等。同时还可以重新利用小规模的电路来作为大型电路的一部分。

三、 实验内容

1、存储扩展实验

**实验目的:**掌握存储扩展基本原理。

**实验内容:**设计字库文件,利用指定规格存储器进行存储器字扩展。

实验要求:

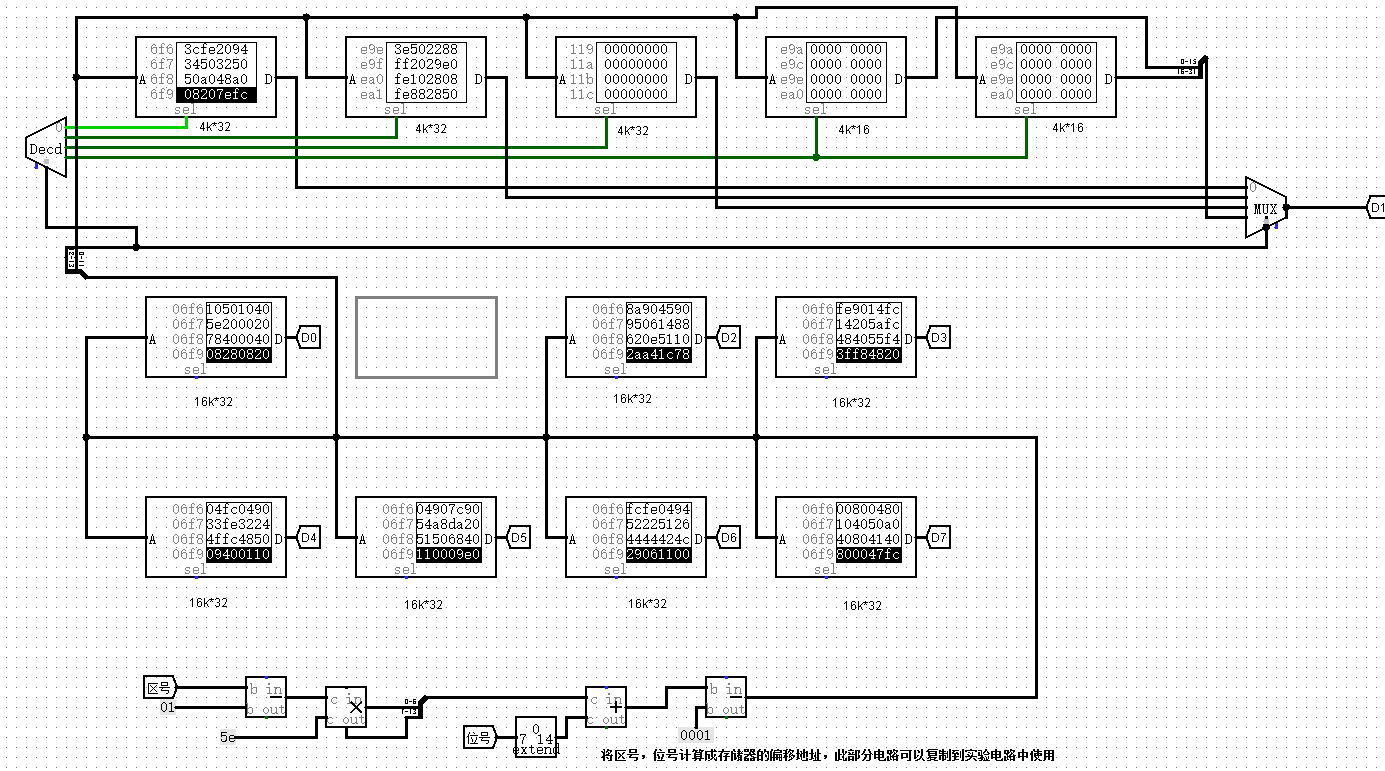

现有如下 ROM 部件,2个4K*16位ROM,3个4K*32 位ROM,7 个16K*32 位 ROM,请构建GB2312 1616 点阵字库存储器电路,电路输入为汉字区号和位号,由于16*16 点阵的字模码需要256 位点阵信息才能显示一个汉字,所以电路输出为 8*32 位

1) 电路图

2) 设计分析与说明

- 对区号和位号经过一系列处理之后计算出存储器的14位偏移地址

- 其中0-11位位地址线,12和13位为片选信号

- 2位片选信号用来决定选择4个4K*32中的哪一个

- 12位地址线用来选择相应ROM的地址

- 将选中地址内的数据输出到相应的数据线

- 8个输出引脚D0-D7,每个引脚输出32位数据,总计输出8*32=256位数据,从而可以表示16*16字形点阵所需要的256位信息

**输入:**汉字在GB2312编码中的区号和位号。

注意:这里区号引脚和位号引脚都只接受7个位数据,这是因为GB2312-80将汉字分为94个区和94个位,故7个位(可表示0-127)即可涵盖区间[0,94]。以“边”字为例,其GB2312编码为1763,17表示区号,63表示位号,故为了显示“边”,我们需要往区号引脚输入0010001(17),往位号引脚输入0111111(63)。

**输出:**GB2312区位码对应的汉字字形码。

电路总共有8个输出引脚D0-D7,每个引脚输出32位数据,总计输出8*32=256位数据,从而可以表示16*16字形点阵所需要的256位信息。

3) 实验结果的记录与分析

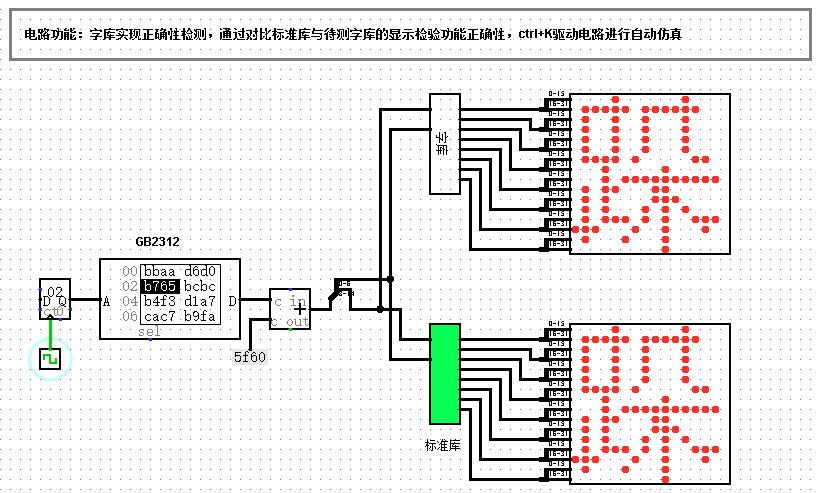

经测试,标准库与待测字库的显示一致,字库实现正确

4) 列出操作步骤及顺序

- 对区号和位号经过一系列处理之后计算出存储器的偏移地址,每个偏移地址对应一个16*16汉字点阵码

- 每次使用同一个存储器偏移地址同时对8个32位ROM进行寻址,单次寻址就可获得8*32=256位数据,其中每个32位ROM保存16*16点阵码的固定两行(表示一行需要16位,两行即32位)

- 将2个 4K*16 ROM位扩展成1个 4K*32 ROM(使用splitter)

- 将4个 4K*32 ROM字扩展成1个 16K*32 ROM(使用multiplexer)

- 字库电路的8个输出引脚(D0-D7)连接至16*16 LED点阵屏上,从而显示汉字的形状

2、MIPS 寄存器文件设计

**实验目的:**为MIPS CPU构造核心功能部件,进一步熟悉多路选择器,译码器,解复用器等Logisim部件的使用

**实验内容:**设计完成满足如下规格要求的 MIPS 通用寄存器组。

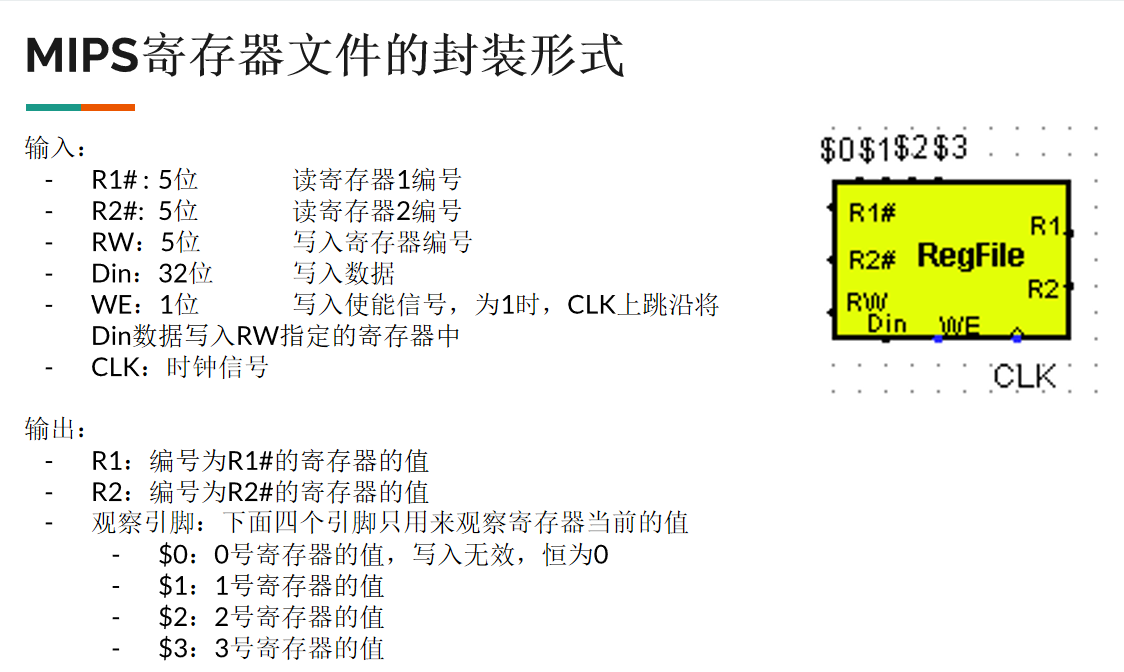

1)利用 logisim 平台构建一个 MIPS 寄存器组,内部包含 32 个 32 位寄存器,其具体功能如下,具体封装文件为 regfile.circ.

表 1 芯片引脚与功能描述

| 引脚 | 输入/输出 | 位宽 | 功能描述 |

|---|---|---|---|

| R1# | 输入 | 5 | 读寄存器 1 编号 |

| R2# | 输入 | 5 | 读寄存器 2 编号 |

| W# | 输入 | 5 | 写入寄存器编号 |

| Din | 输入 | 32 | 写入数据 |

| WE | 输入 | 1 | 写入使能信号,为 1 时,CLK 上跳沿将Din 数据写入 W#寄存器 |

| CLK | 输入 | 1 | 时钟信号,上跳沿有效 |

| R1 | 输出 | 32 | R1#寄存器的值 |

| R2 | 输出 | 32 | R2#寄存器的值 |

| $s0 | 输出 | 32 | 编号为 16 的寄存器的值 |

| $s1 | 输出 | 32 | 编号为 17 的寄存器的值 |

| $s2 | 输出 | 32 | 编号为 18 的寄存器的值 |

| $ra | 输出 | 32 | 编号为 31 的寄存器的值 |

-

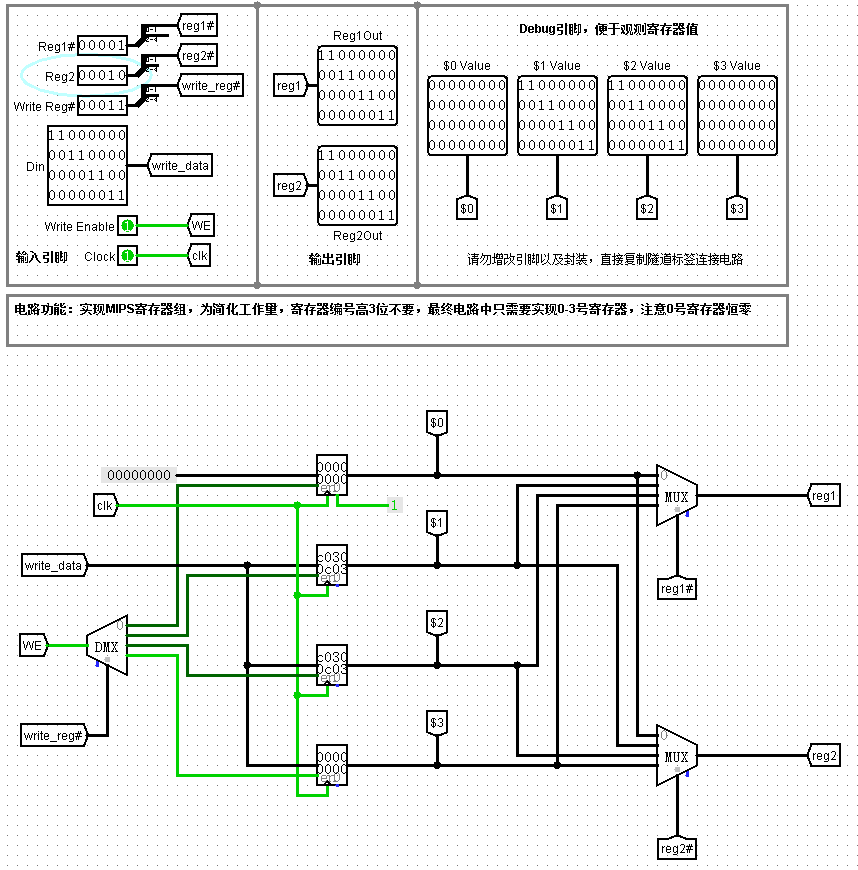

为减少实验中画图工作量,实验工程文件中对 5 位寄存器地址进行了简化,具体见引脚示意图,最终只需实现 4 个寄存器,0 号寄存器功能仍然是恒零。后续实验中如需要使用 32 个寄存器的 MIPS 寄存器文件组,将提供标准组件。

-

注意时钟信号和电平信号不要混连,时钟仅仅触发状态改变。

实验要求:

- 利用logisim平台构建一个MIPS寄存器组,内部包含32个32位寄存器(实际4个)

- 为减少实验中画图工作量,实验工程文件中对5位寄存器地址进行了简化,具体见引脚示意图,最终只需实现4个寄存器(0-3号),0号寄存器恒为0

- 注意时钟信号和电平信号不要混连,时钟仅仅触发状态改变

1) 电路图

2) 设计分析与说明

3) 实验结果的记录与分析

经测试,符合条件,电路设计正确

4) 列出操作步骤及顺序

输入引脚:

- 分别通过reg1# reg2# write_reg#获得输入的三个寄存器编号,因为实验只要求实现0-3号寄存器,所以只需提取5位编号输入的低2位(00/01/10/11)

- 通过 write_data 获取要写入寄存器的32位数据

- 通过 WE 获取写入标志

- 通过 clk 获取时钟信号

输出引脚:

- 将读寄存器1的值输出到reg1

- 将读寄存器2的值输出到reg2

- 将4个寄存器当前保存的值输出到$0,$1,$2,$3

寄存器选择输出:

- 利用多路复用器(multiplexer),多路复用器可以通过select bits选择多个输入中的一个进行输出

- 将四个寄存器的输出引脚同时接到多路复用器的输入引脚上,将reg1#和reg2#作为多路复用器的select bits,从而选择指定输入进行输出。

寄存器选择写入:

- 利用解复用器(demultiplexer),解复用器可以将输入只通过select bits指定的线路输出。

- 将write_data同时连接到四个寄存器的data引脚(由于0号寄存器恒为0,因此可以忽略data引脚,或者将en置0)

- 将we引脚作为解复用器的输入

- 将write_reg#作为解复用器的select bits

- 通过解复用器将要写入数据的寄存器的enable引脚置1,下个时钟信号到来时,只有该写入寄存器的enable引脚为1,因此wrtie_data数据只会写入到该寄存器中(其余寄存器enable引脚为0,时钟信号不会触发寄存器写入),从而实现寄存器选择写入

四、实验收获和体会

通过存储扩展实验,我了解到了存储器字位拓展的具体实现,掌握了存储扩展基本原理。之前知识会在纸上画画简单的电路图,使用logisim设计电路图之后,更加了解了电路的一些细节设计,掌握了一些器件的用法已经各引脚的功能。

通过MIPS 寄存器文件设计进一步熟悉多路选择器,译码器,解复用器等Logisim部件的使用。

五、实验中碰到的问题和解决的方法

1.寄存器的引脚比较多,可能会连错线

解决方法:每次连线的时候的要认真看每一个引脚的名称,掌握其具体功能

2.存储扩展的输出引脚显示不了部分字形阵

通过MIPS 寄存器文件设计进一步熟悉多路选择器,译码器,解复用器等Logisim部件的使用。

五、实验中碰到的问题和解决的方法

1.寄存器的引脚比较多,可能会连错线

解决方法:每次连线的时候的要认真看每一个引脚的名称,掌握其具体功能

2.存储扩展的输出引脚显示不了部分字形阵

解决方法:注意每一个ROM的表示范围。由于数据已经导入到ROM中,所以顺序固定为从左到右地址增加,在进行字扩展时,要注意地址区间的划分

2611

2611

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?