努力是为了不平庸~

学习的最大理由是想摆脱平庸,早一天就多一份人生的精彩;迟一天就多一天平庸的困扰。

需要代码答案的同学请直接点击目录跳到下方解答处!!

目录

实验目的

理解存储系统进行位扩展、字扩展的基本原理,能利用相关原理解决实验中汉字字库的存储扩展问题,并能够使用正确的字库数据填充。

实验内容

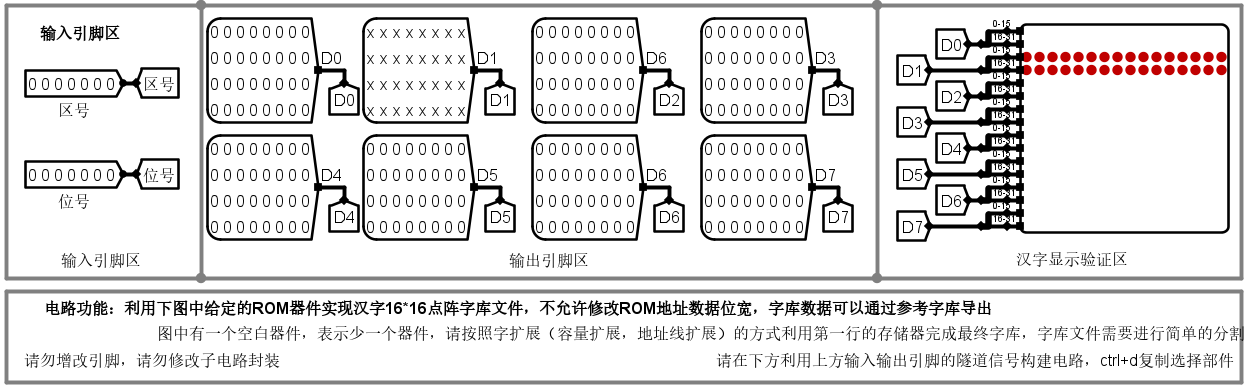

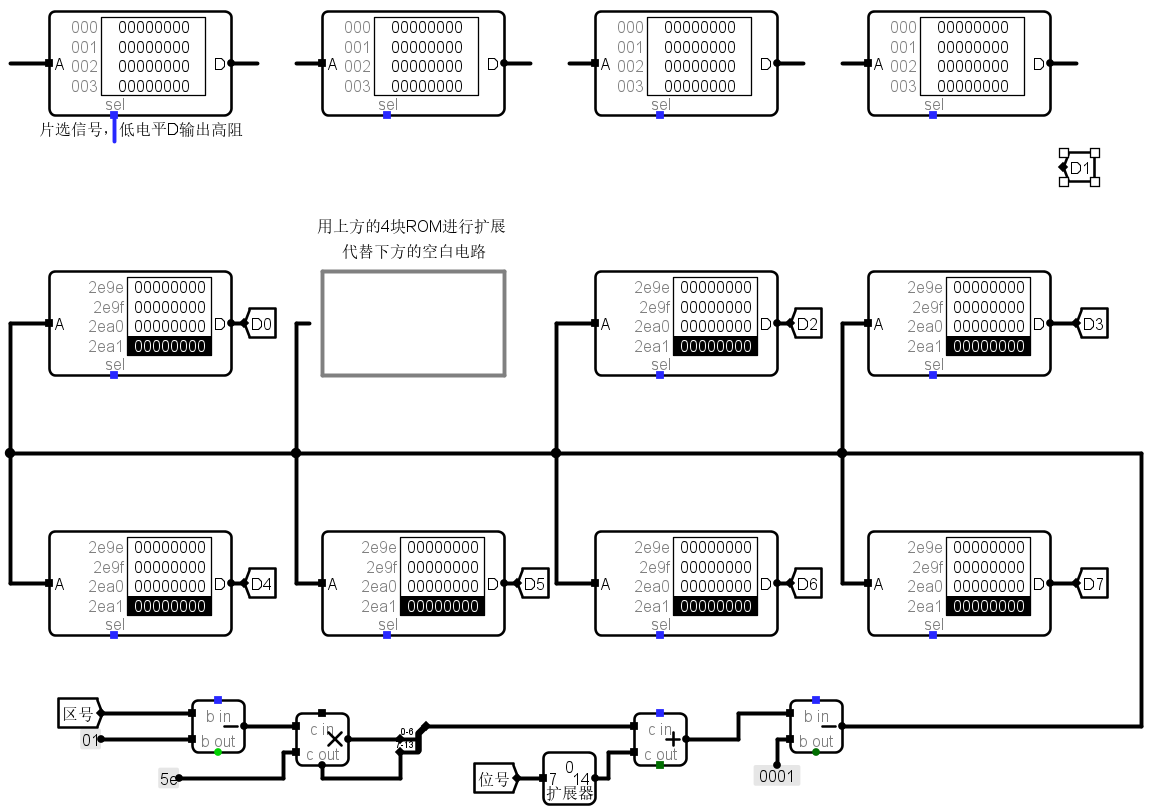

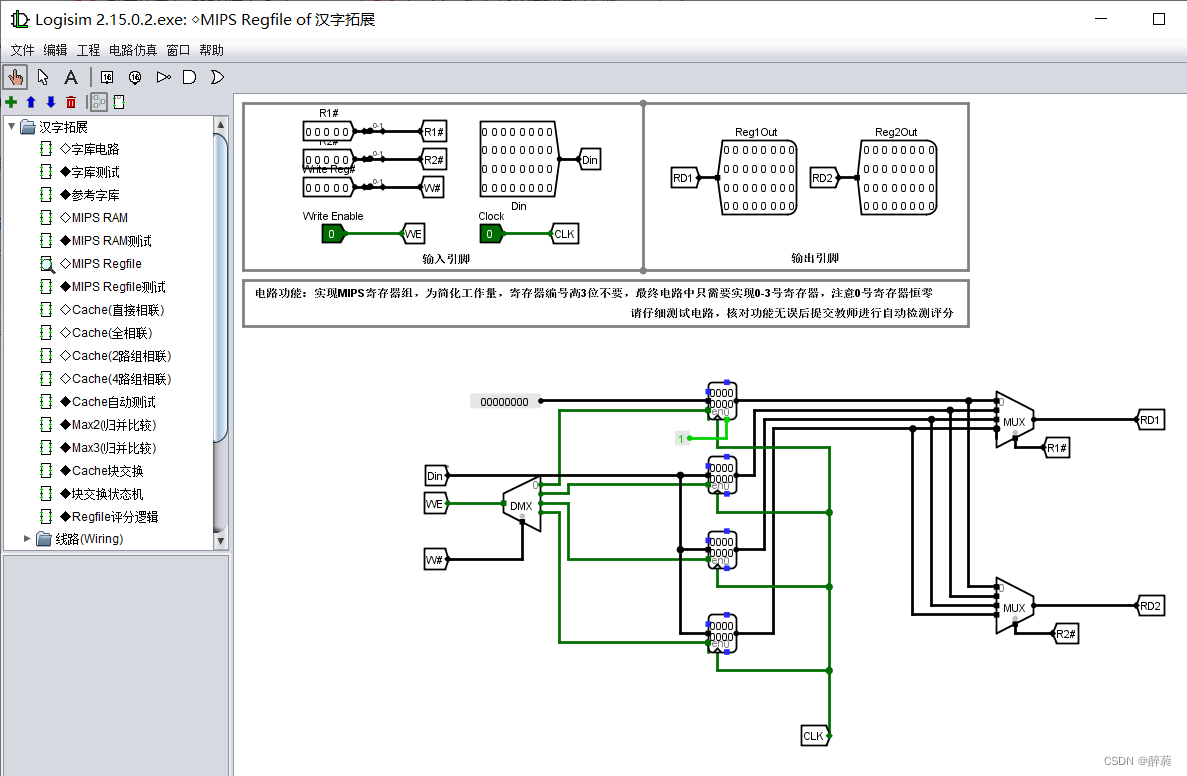

现有如下 ROM 组件,4片4K*32位 ROM ,7片 16K*32位 ROM,请在 Logisim 平台构建 GB2312 汉字编码的16K*16点阵汉字字库,电路输入为汉字区号和位号,电路输出为8×32位(16K*16=256 位点阵信息),待完成的字库电路输入输出引脚见后图,具体参见工程文件中的 storage.circ 文件,图中左侧是输入引脚,分别对应汉字区位码的区号和位号,中间区域为8个32位的输出引脚,可一次性提供一个汉字的256位点阵显示信息,右侧是实际显示区域,用于观测汉字显示是否正常。待完成字库子电路封装已经完成,请勿修改以免影响后续自动测试功能。

电路框架

storage.circ

电路引脚

| 信号 | 输入/输出 | 位宽 | 说明 |

|---|---|---|---|

| 区号Qu | 输入 | 7 位 | 汉字区位码的区号 |

| 位号Wei | 输入 | 7 位 | 汉字区位码的位号 |

| Di | 输出 | 32 位 | 汉字点阵信息 |

电路测试

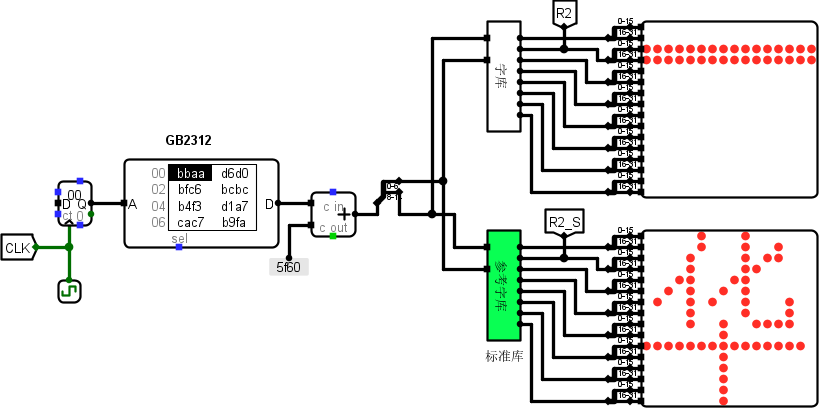

完成存储扩展设计后,可以在字库测试电路中进行对比测试,如下图所示:

实验完成后,可利用文本编辑工具打开 storage.circ ,将所有文字信息复制粘贴到 Educoder 平台的 storage.circ 文件中,再点击评测按钮即可进行本关测试,平台会对你设计的电路进行自动测试,为方便测试,请勿修改子电路封装,本关测试用例如下:

CNT Qu Wei Chip1Data00 1b 0a 0860085801 36 30 7ffe010402 1f 26 0850f89003 1c 1c 13fc104804 14 53 0100010005 31 07 0020111006 2a 27 0fe0082007 19 5a 5ff4402408 1c 32 40027ffe09 1d 2c 09447f40

图解:

代码题解(已上传资源):

Logisim头歌汉字字库存储芯片扩展实验图解及代码(计算机组成原理)直接打开文件,全选然后直接复制粘贴使用、可以私信提资源-CSDN文库

586

586

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?