一、本文内容

内容:掌握Quarters工程的建立方法

版本:Quartus II 13.1(64-bit)

二、建立步骤

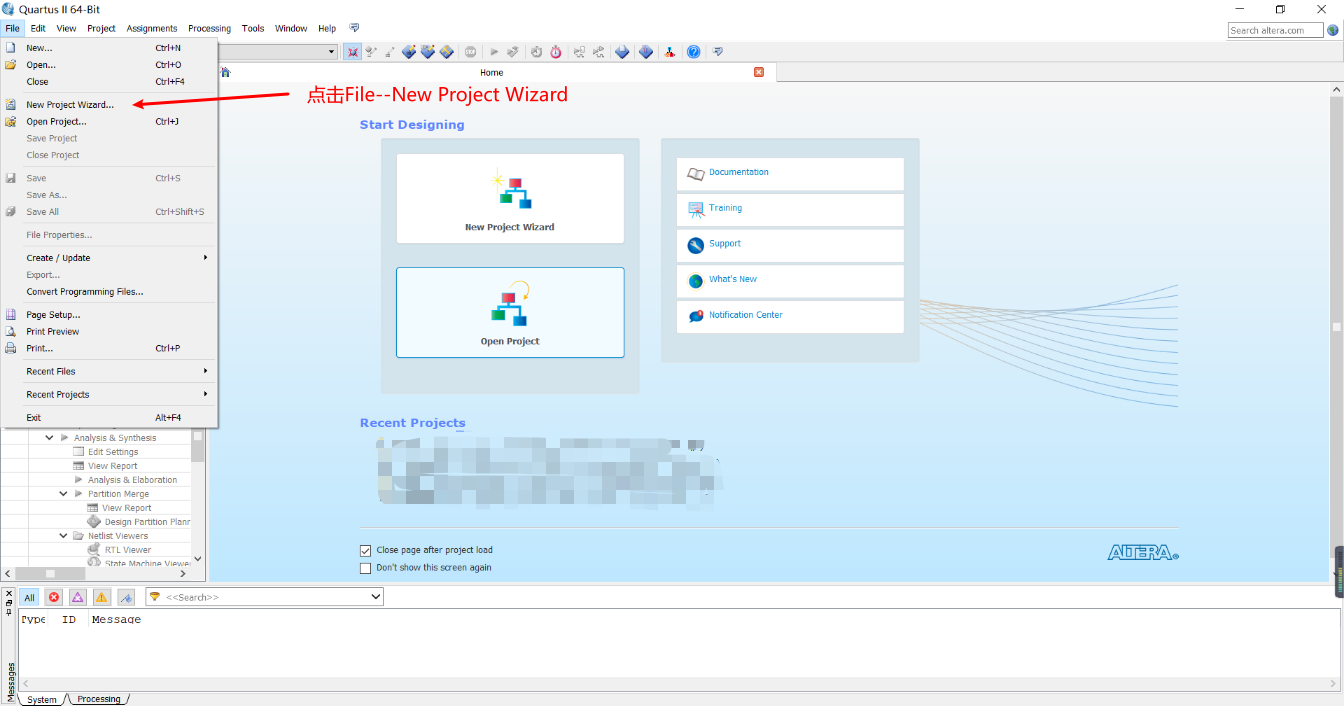

1、 打开软件

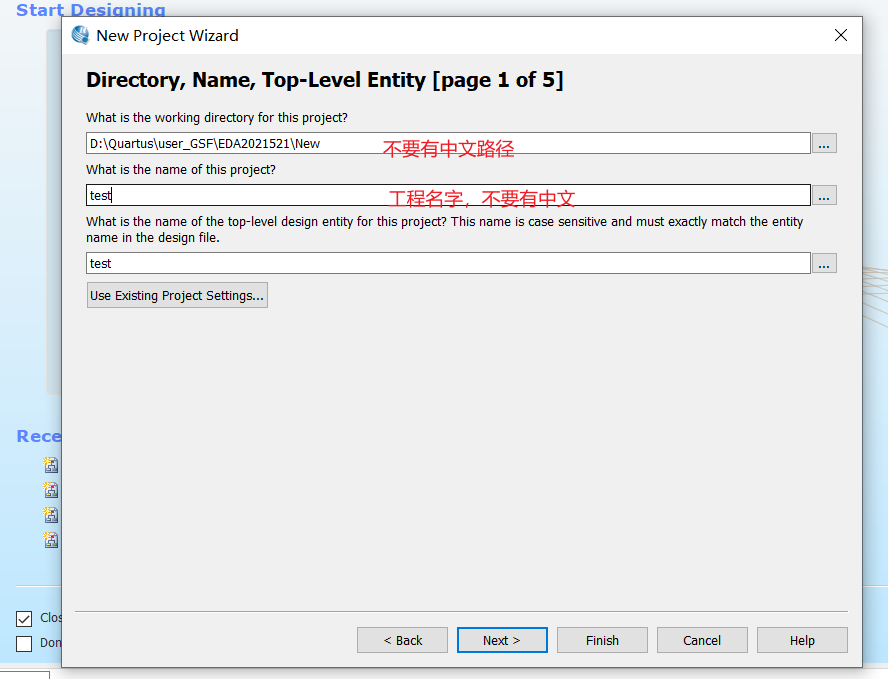

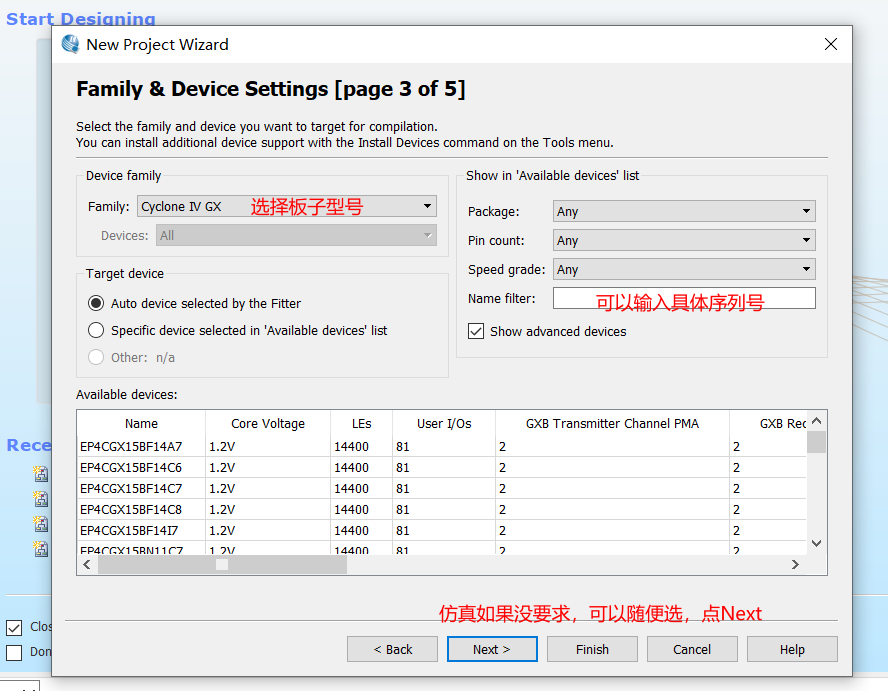

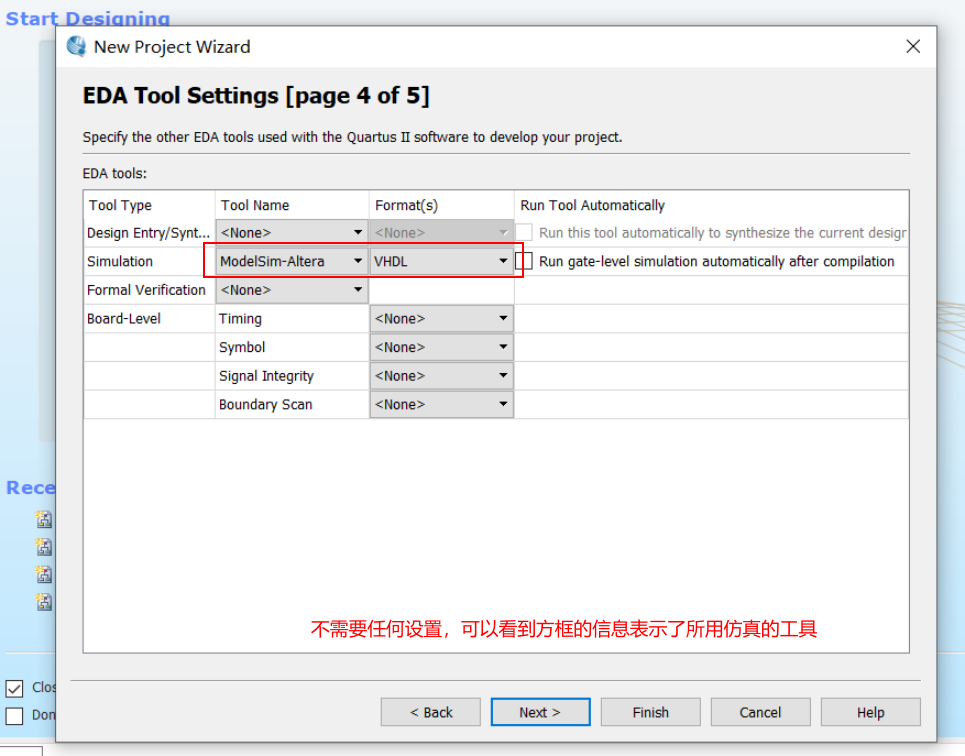

2、 工程设置

工程名字和后边文件的顶层模块名字以及顶层模块所在文件的名字要保持一致,需要注意,后边会有具体说明

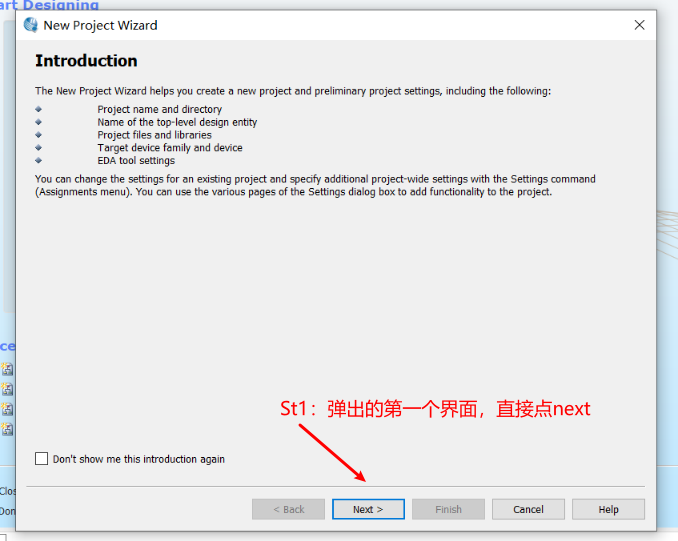

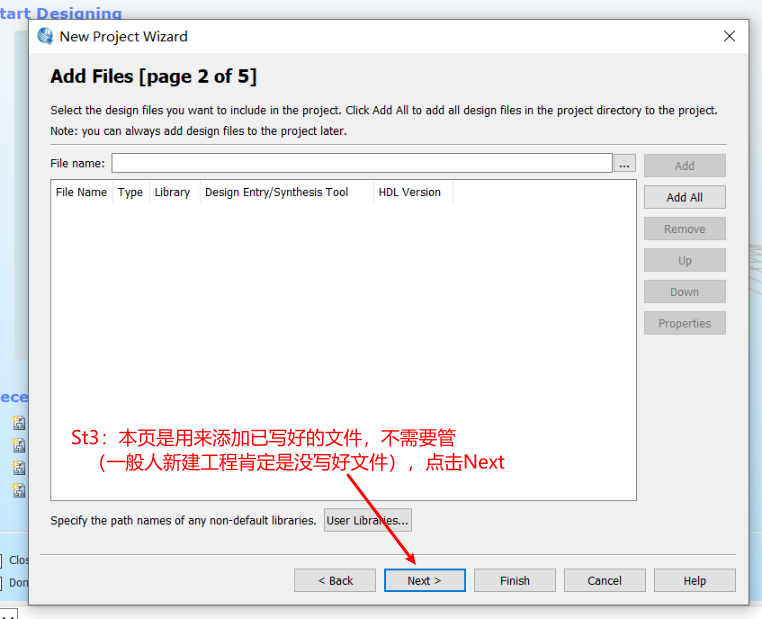

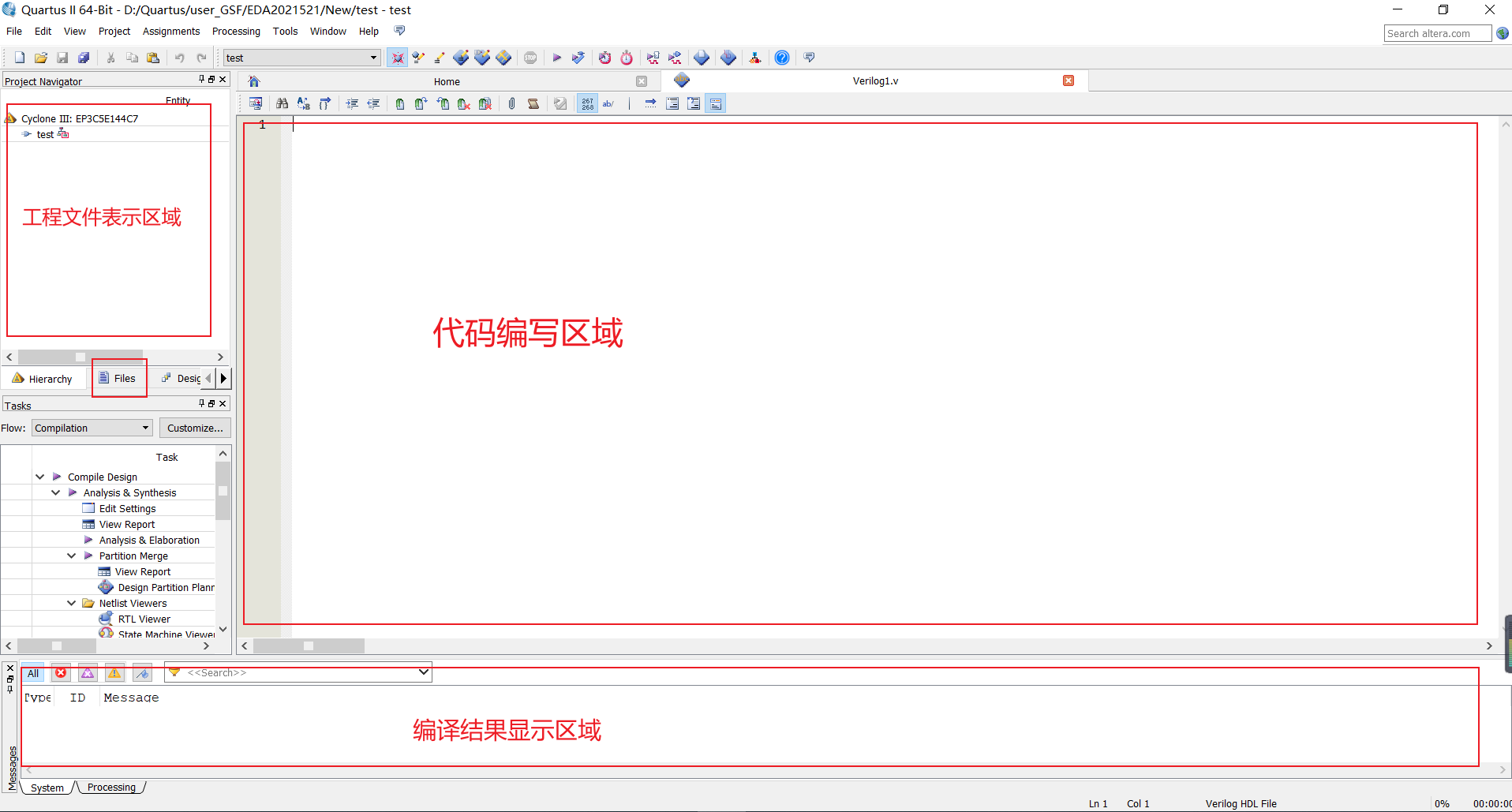

3、新建工程文件

4、结果

三、代码编译、仿真

1、示例代码

module FenPin(

input clk,

input rst,

output wire clk_10k

);

parameter f=8; //偶分频的分频数

reg [11:0] count=0; //存储分频计数

reg clk_10k_tmp=0;

assign clk_10k = clk_10k_tmp;

// ret未被按下,为高电平;按下为低电平,后回复为高电平

always @(posedge clk, negedge rst)

begin

if (!rst)

begin

clk_10k_tmp = 0;

count = 0;

end

else

begin

if (count == f/2-1) //分频系数确定:偶分频数/2 - 1

begin

clk_10k_tmp = ~clk_10k_tmp;

count = 0;

end

else

begin

count = count + 1;

end

end

end

endmodule

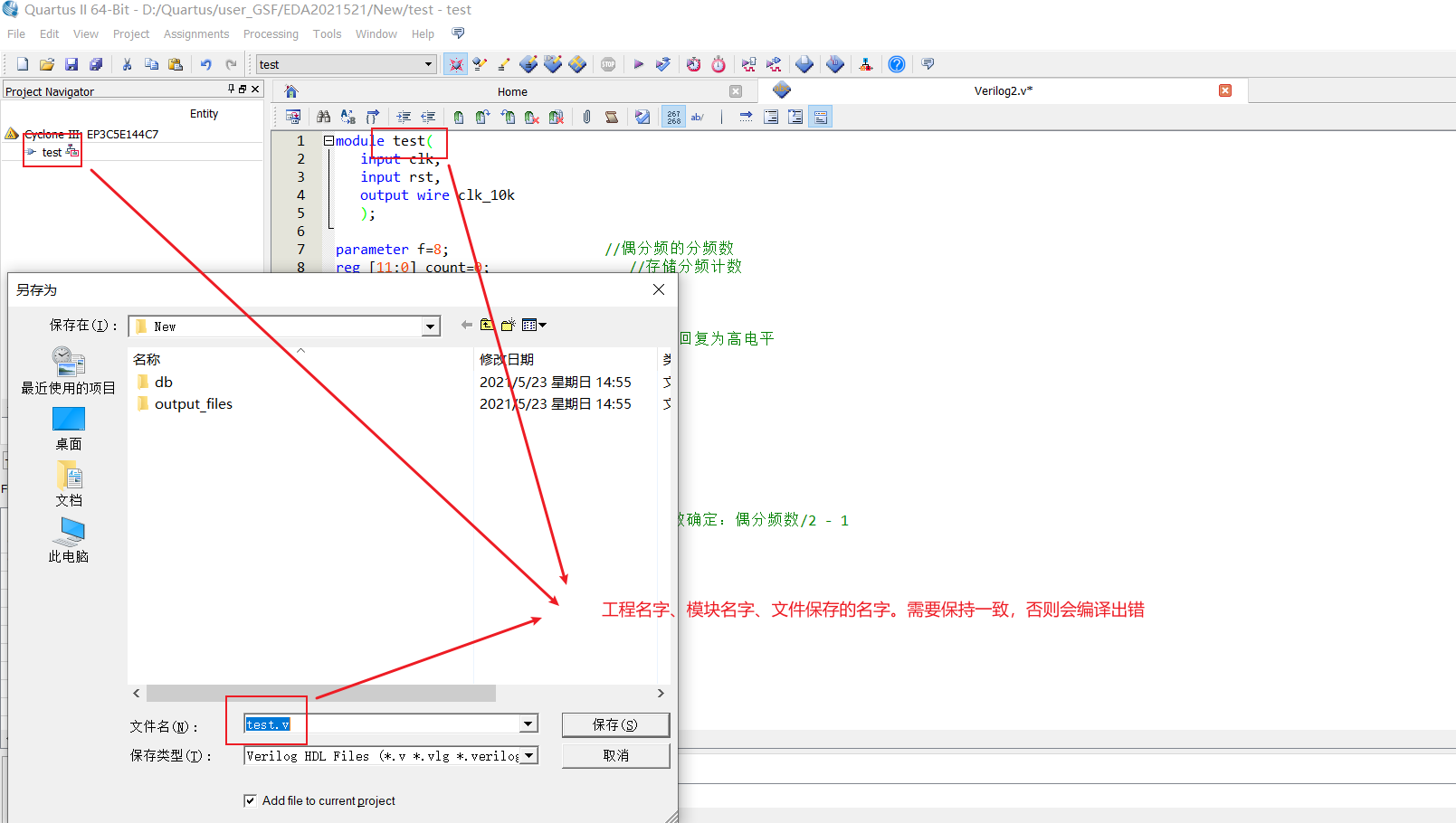

2、文件保存

所以在新建工程的时候要注意工程的名字!!!

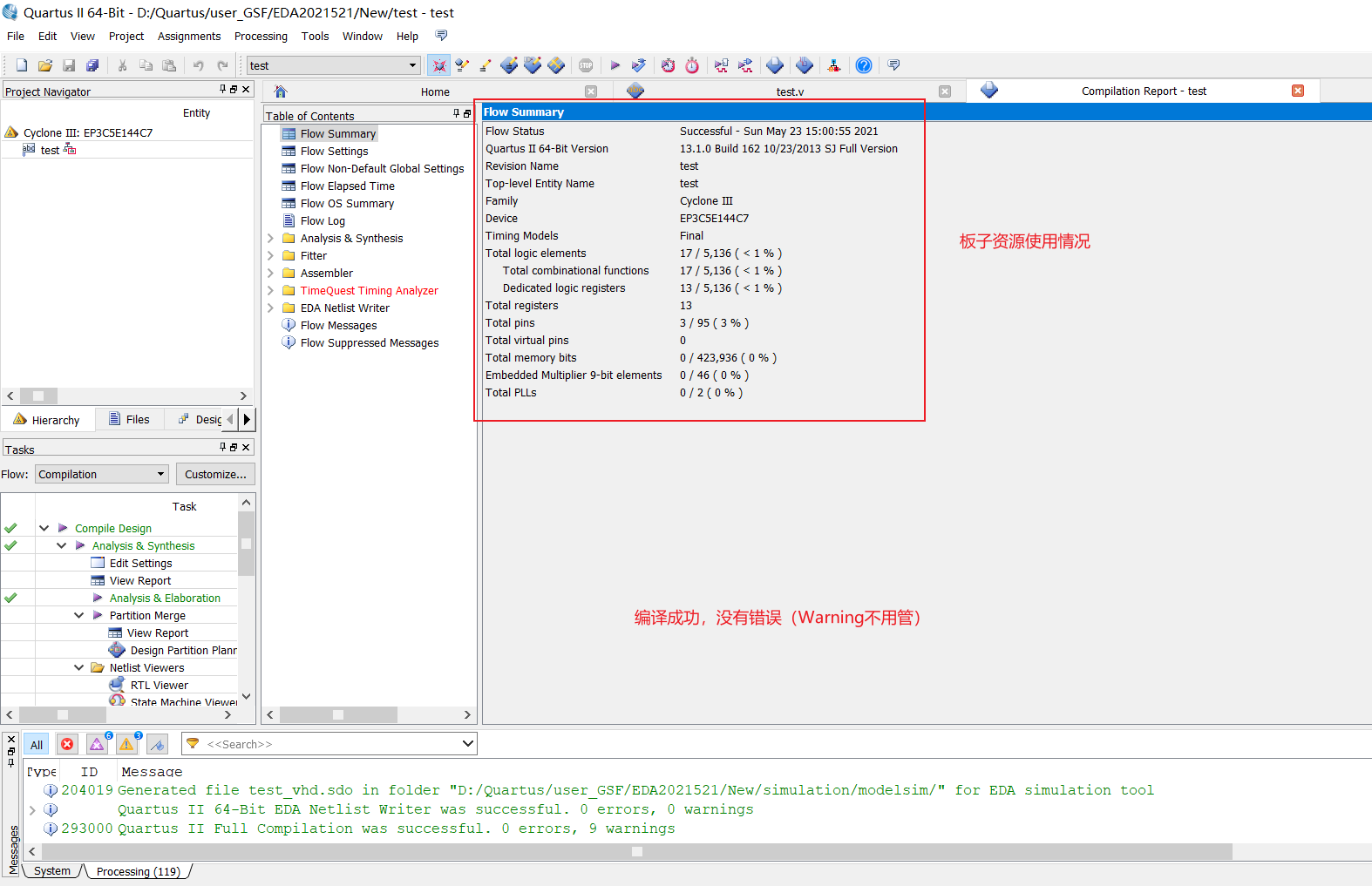

3、代码编译

4、简单的仿真

新建文件

早期版本的Quartus软件没有提供这种文件,也就无法用此方法进行简单仿真

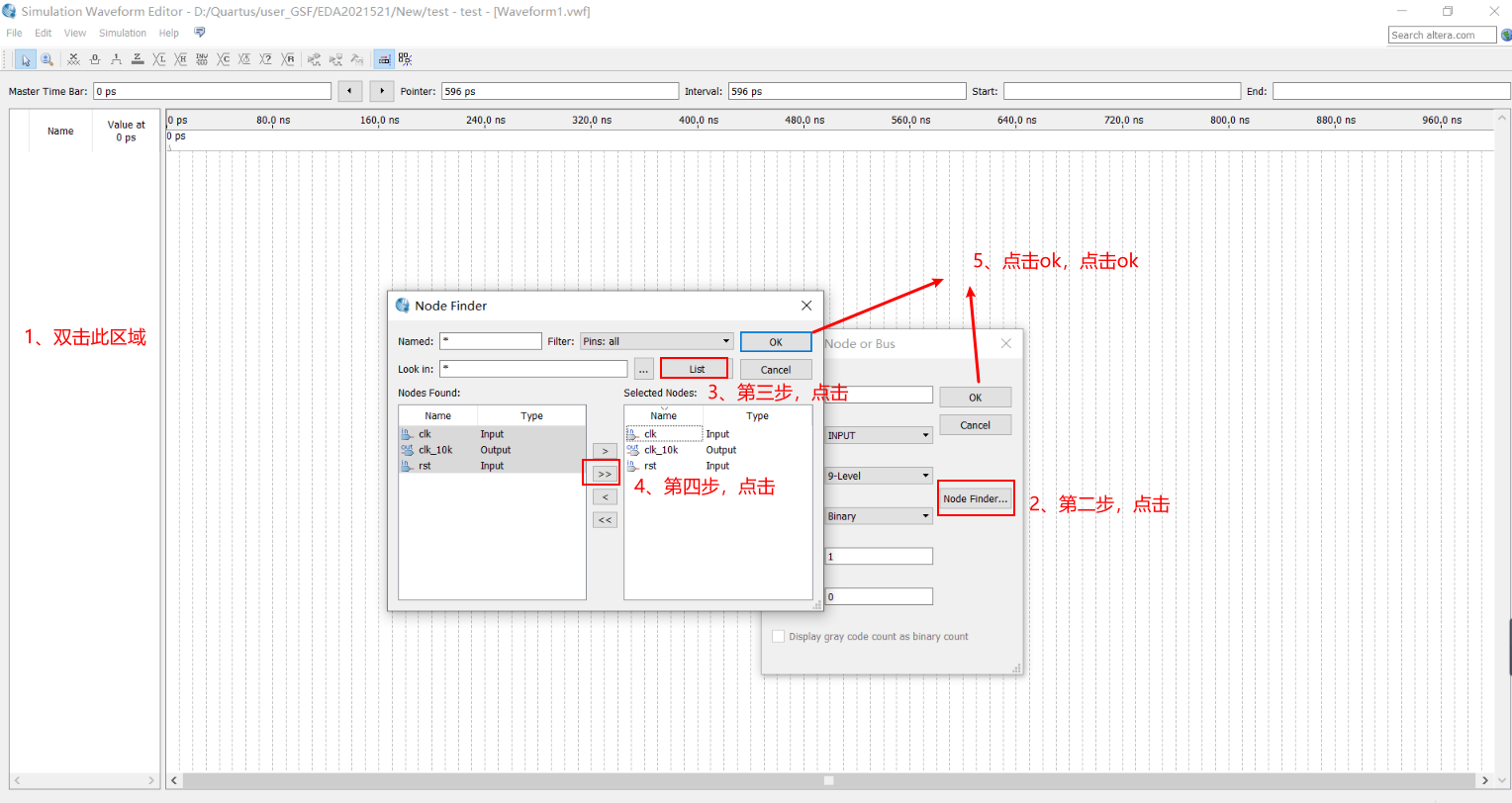

添加输入输出信号

设置输入信号的格式

1、功能介绍

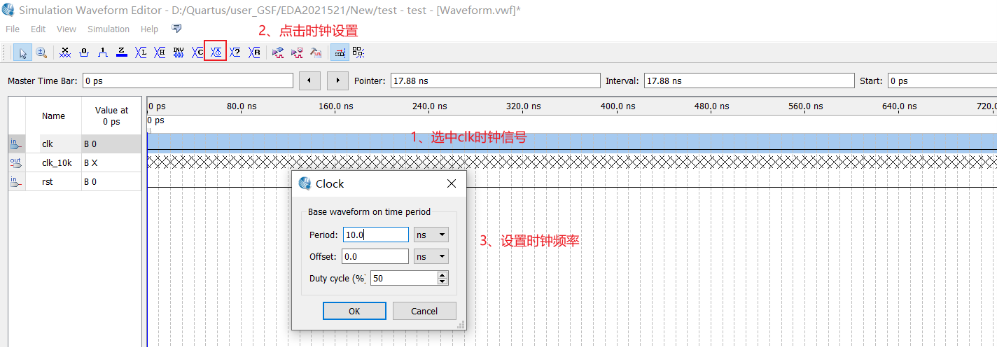

2、设置时钟频率

3、时钟信号设置结果

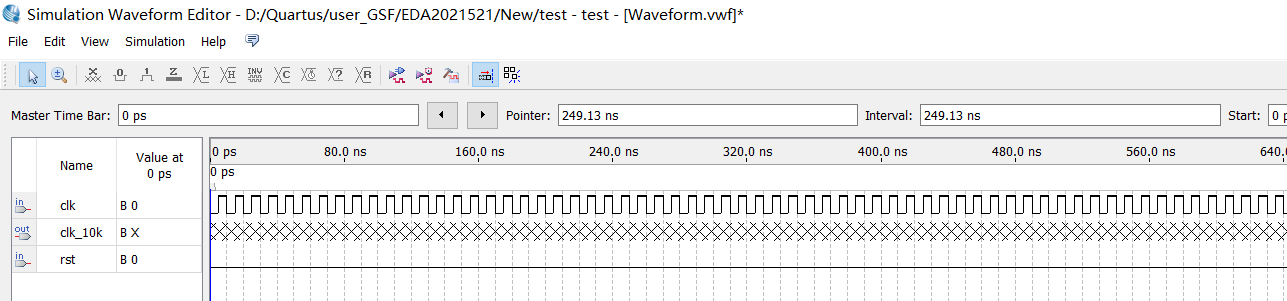

4、设置rst复位信号

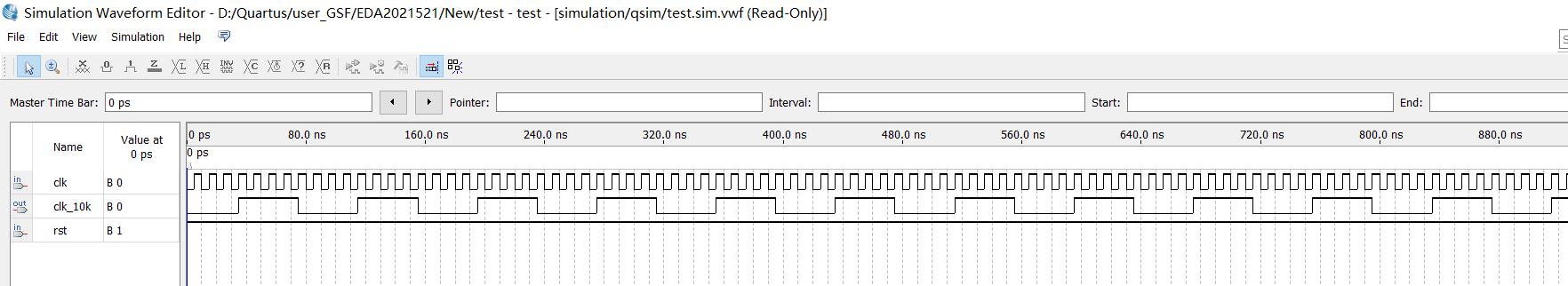

仿真结果

可以看到输出信号clk_10k的时钟频率是clk时钟信号的1/8,正确实现分频功能

总结

这种形式的仿真过于简单,只能在初始时候,设置输入信号的格式,后续就不能更改

再更改信号的格式就需要重新设置,重新仿真

更为广泛的仿真方式:Modelsim仿真

1799

1799

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?