设计任务:

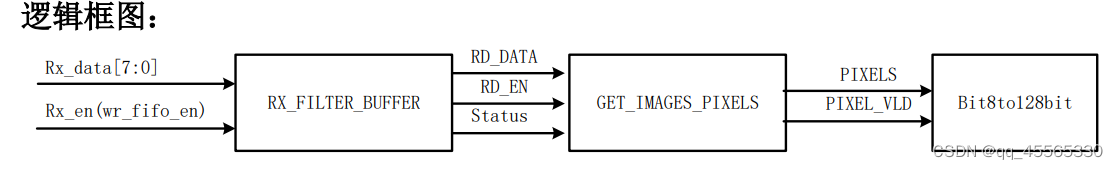

本项目使用 PC 机将图像数据信息通过千兆以太网发送给 FPGA,FPGA 接 收后需要对 CRC 校验和过滤无效帧传递给下一级模块。 经过 CRC 校验的数据写入之前写好的 8bit 转 128bit 的缓冲模块中,从而写入到 DDR 存储器中。

项目目的:

学习 Matlab 读取 AVI 视频流并转换为 16bit 模式二进制数据,通过以太网发送给板卡,板卡接收并显示。

千兆RX 端获取有效像素,滤除包头 CRC 等附加数据信息

第一:根据 status 的包长度把固定包头和 crc 信息滤除,传递给 Bit8to128bit,这样就是与之前课程级联起来,完成图像到 DDR3 的缓冲。

第二:matlab 中读取 AVI 格式视频,按照 BIT16 的像素格式转换为视频数据, 并通过以太网发送。

获取像素模块波形图:

千兆数据流存储和 Matlab 视频数据转换和发送

千兆数据流存储和 Matlab 视频数据转换和发送

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

749

749

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?