一、二选一多路器

module mux2(

a,

b,

sel,

out

);//端口声明用逗号,最后一个不用

//端口定义用分号

//sel = 0;out = a;

//sel =1; out = b;

input a;

input b;

input sel;

output out;

assign out = (sel == 0)?a:b;

endmodule仿真测试代码:

`timescale 1ns/1ns

module mux2_tb();

//输入信号

reg s0;

reg s1;

reg s2;

//输出信号

wire mux2_out;

mux2 mux2(

.a(s0),//例化连接

.b(s1),

.sel(s2),

.out(mux2_out)

);

initial begin //产生激励信号

s0=0;s1=0;s2=0;

#20;//在仿真时间上延迟20纳秒(和开头相符)

s2=0;s1=0;s0=1;

#20;

s2=0;s1=1;s0=0;

#20;

s2=0;s1=1;s0=1;

#20;

s2=1;s1=0;s0=0;

#20;

s2=1;s1=0;s0=1;

#20

s2=1;s1=1;s0=0;

#20;

s2=1;s1=1;s0=1;

#20;

end

endmodule

二、三八译码器

module decoder_3_8(

A0,

A1,

A2,

Y0,

Y1,

Y2,

Y3,

Y4,

Y5,

Y6,

Y7

);

input A0;

input A1;

input A2;

output reg Y0;

output reg Y1;

output reg Y2;

output reg Y3;

output reg Y4;

output reg Y5;

output reg Y6;

output reg Y7;

always @(*)

case ({A2,A1,A0})

3'b000: {Y7,Y6,Y5,Y4,Y3,Y2,Y1,Y0} = 8'b0000_0001;

3'b001: {Y7,Y6,Y5,Y4,Y3,Y2,Y1,Y0} = 8'b0000_0010;

3'b010: {Y7,Y6,Y5,Y4,Y3,Y2,Y1,Y0} = 8'b0000_0100;

3'b011: {Y7,Y6,Y5,Y4,Y3,Y2,Y1,Y0} = 8'b0000_1000;

3'd4: {Y7,Y6,Y5,Y4,Y3,Y2,Y1,Y0} = 8'b0001_0000;

3'd5: {Y7,Y6,Y5,Y4,Y3,Y2,Y1,Y0} = 8'b0010_0000;

3'd6: {Y7,Y6,Y5,Y4,Y3,Y2,Y1,Y0} = 8'b0100_0000;

3'd7: {Y7,Y6,Y5,Y4,Y3,Y2,Y1,Y0} = 8'b1000_0000;

default:{Y7,Y6,Y5,Y4,Y3,Y2,Y1,Y0} = 8'b0000_0000;

endcase

endmodule

仿真测试代码:

`timescale 1ns/1ns

module decoder_3_8_tb();

reg A0;

reg A1;

reg A2;

wire Y0;

wire Y1;

wire Y2;

wire Y3;

wire Y4;

wire Y5;

wire Y6;

wire Y7;

decoder_3_8 decoder_3_8_inst0(

.A0(A0),

.A1(A1),

.A2(A2),

.Y0(Y0),

.Y1(Y1),

.Y2(Y2),

.Y3(Y3),

.Y4(Y4),

.Y5(Y5),

.Y6(Y6),

.Y7(Y7)

);

initial begin

A2=0;A1=0;A0=0;

#20;

A2=0;A1=0;A0=1;

#20;

A2=0;A1=1;A0=0;

#20;

A2=0;A1=1;A0=1;

#20;

A2=1;A1=0;A0=0;

#20;

A2=1;A1=0;A0=1;

#20;

A2=1;A1=1;A0=0;

#20;

A2=1;A1=1;A0=1;

#20;

end

endmodule

三、跑马灯

module led_run(

Clk,

Reset_n,

Led

);

input Clk;

input Reset_n;

output reg [7:0]Led;

//实现500ms计数

reg [24:0] counter;

always@(posedge Clk or negedge Reset_n)

if (!Reset_n)

counter <=0;

else if (counter == 25'd25_000_000 -1)

counter <=0;

else

counter <= counter + 1'd1;

always@(posedge Clk or negedge Reset_n)

if (!Reset_n)

Led <= 8'b0000_0001;

else if (counter == 25'd25_000_000 - 1) begin

if((Led == 8'b0000_0000)||Led == 8'b1000_0000)

Led <= 8'b0000_0001;

else

Led <= Led << 1;

end

endmodule

仿真测试代码:

`timescale 1ns/1ns

module led_run_tb();

reg Clk;

reg Reset_n;

wire [7:0] Led;

led_run led_run(

.Clk(Clk),

.Reset_n(Reset_n),

.Led(Led)

);

initial Clk =1;

always #10 Clk = ~Clk;

initial begin

Reset_n = 0;

#201;

Reset_n = 1;

#4_000_000_0;

$stop;

end

endmodule

四、多个Led按不同频率闪烁

1.单个闪烁

module led_twinkle(

Clk,

Reset_n,

Led

);

input Clk;

input Reset_n;

output reg Led;

parameter MCNT = 25_000_000 - 1;

reg [24:0] counter;

always@(posedge Clk or negedge Reset_n)

if (!Reset_n)

counter <= 0;

else if (counter ==MCNT)

counter <=0;

else

counter <= counter +1'd1;

always@(posedge Clk or negedge Reset_n)

if (!Reset_n)

Led <= 0;

else if (counter ==MCNT)

Led <= !Led;

endmodule

2.多个闪烁

调用单个闪烁模块

module led_twinkle_4(

Clk,

Reset_n,

Led

);

input Clk;

input Reset_n;

output [3:0]Led;

led_twinkle led_twinkle_inst0(

.Clk(Clk),

.Reset_n(Reset_n),

.Led(Led[0])

);

led_twinkle

#(

.MCNT(12_500_000 - 1)

)

led_twinkle_inst1(

.Clk(Clk),

.Reset_n(Reset_n),

.Led(Led[1])

);

defparam led_twinkle_inst2.MCNT = 6_250_000 - 1;

led_twinkle led_twinkle_inst2(

.Clk(Clk),

.Reset_n(Reset_n),

.Led(Led[2])

);

defparam led_twinkle_inst3.MCNT = 2_500_000 - 1;

led_twinkle led_twinkle_inst3(

.Clk(Clk),

.Reset_n(Reset_n),

.Led(Led[3])

);

endmodule

仿真测试代码:

`timescale 1ns/1ns

module led_twinkle_4_tb();

reg Clk;

reg Reset_n;

wire [3:0]Led;

led_twinkle_4 led_twinkle_4(

.Clk(Clk),

.Reset_n(Reset_n),

.Led(Led)

);

initial Clk = 1;

always #10 Clk = ~Clk;

initial begin

Reset_n = 0;

#201;

Reset_n = 1;

#2_000_000_000;

$stop;

end

endmodule五、根据外部输入控制Led闪烁

1.连续变化

module led_ctrl2(

Clk,

Reset_n,

sw,

Led

);

input Clk;

input Reset_n;

input [7:0] sw;

output reg [1:0]Led;

parameter MCNT = 12_500_000 - 1;

reg [26:0] counter0;

reg [2:0] counter1;

always@(posedge Clk or negedge Reset_n)

if(!Reset_n)

counter0 <= 0;

else if (counter0 == MCNT)

counter0 <= 0;

else

counter0 <= counter0 + 1'd1;

always@(posedge Clk or negedge Reset_n)

if(!Reset_n)

counter1 <= 0;

else if (counter0 == MCNT) begin

if (counter1 == 7)

counter1 <= 0;

else

counter1 <= counter1 + 1'd1;

end

always@(posedge Clk or negedge Reset_n)

if(!Reset_n)

Led <= 2'b11;

else begin

case (counter1)

0: Led <= ((sw[0] == 1) ? 2'b11 : 2'b00);

1: Led <= ((sw[1] == 1) ? 2'b11 : 2'b00);

2: Led <= ((sw[2] == 1) ? 2'b11 : 2'b00);

3: Led <= ((sw[3] == 1) ? 2'b11 : 2'b00);

4: Led <= ((sw[4] == 1) ? 2'b11 : 2'b00);

5: Led <= ((sw[5] == 1) ? 2'b11 : 2'b00);

6: Led <= ((sw[6] == 1) ? 2'b11 : 2'b00);

7: Led <= ((sw[7] == 1) ? 2'b11 : 2'b00);

default:Led <=Led;

endcase

end

endmodule

仿真测试代码:

`timescale 1ns/1ns

module led_ctrl0_tb();

reg Clk;

reg Reset_n;

reg [7:0] sw;

wire Led;

led_ctrl2 led_ctrl2(

.Clk(Clk),

.Reset_n(Reset_n),

.Led(Led),

.sw(sw)

);

// defparam led_ctrl1.TIME = 1;

defparam led_ctrl2.MCNT = 125_00-1;

initial Clk = 1;

always #10 Clk = ~Clk;

initial begin

Reset_n = 0;

sw = 8'b1010_1010;

#201;

Reset_n = 1;

#4_000_000;

sw = 8'b0000_0001;

#4_000_000;

$stop;

end

endmodule

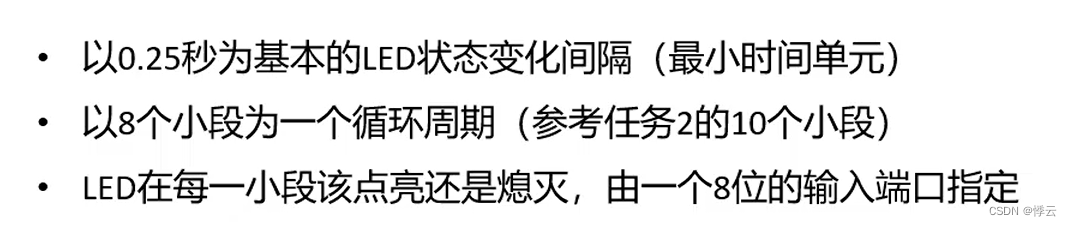

2.间隔一段时间变化

module led_ctrl3(

Clk,

Reset_n,

sw,

Led

);

input Clk;

input Reset_n;

input [7:0] sw;

output reg Led;

reg [26:0] counter0;

reg [2:0] counter1;

reg [27:0] counter2;

reg en_counter2;

reg en_counter0;

parameter MCNT0 = 12_500_000 - 1;//0.25s

parameter MCNT2 = 50_000_000 - 1;//1s

//空闲1秒的计数

always@(posedge Clk or negedge Reset_n)

if(!Reset_n)

counter2 <= 0;

else if(en_counter2) begin

if(counter2 == MCNT2)

counter2 <= 0;

else

counter2 <= counter2 + 1'd1;

end

else

counter2 <= 0;

//en_counter2

always@(posedge Clk or negedge Reset_n)

if(!Reset_n)

en_counter2 <= 1;

else if((counter1 == 7 )&&(counter0 == MCNT0))

en_counter2 <= 1;

else if (counter2 == MCNT2)

en_counter2 <= 0;

//en_counter0

always@(posedge Clk or negedge Reset_n)

if(!Reset_n)

en_counter0 <= 0;

else if((counter1 == 7 )&&(counter0 == MCNT0))

en_counter0 <= 0;

else if (counter2 == MCNT2)

en_counter0 <= 1;

//0.25秒的计数

always@(posedge Clk or negedge Reset_n)

if(!Reset_n)

counter0 <= 0;

else if(en_counter0) begin

if (counter0 == MCNT0)

counter0 <= 0;

else

counter0 <= counter0 + 1'd1;

end

else

counter0 <= 0;

//8个状态

always@(posedge Clk or negedge Reset_n)

if(!Reset_n)

counter1 <= 0;

else if (counter0 == MCNT0) begin

if (counter1 == 7)

counter1 <= 0;

else

counter1 <= counter1 + 1'd1;

end

//开关控制8个状态的亮灭

always@(posedge Clk or negedge Reset_n)

if(!Reset_n)

Led <= 0;

else if(en_counter0 == 0)

Led <=0;

else begin

case (counter1)

0: Led <= sw[0];

1: Led <= sw[1];

2: Led <= sw[2];

3: Led <= sw[3];

4: Led <= sw[4];

5: Led <= sw[5];

6: Led <= sw[6];

7: Led <= sw[7];

default:Led <=Led;

endcase

end

endmodule

1427

1427

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?