来自正点原子的学习笔记

LED闪烁实验

1 LED简介

发光二极管

2 硬件设计

核心板原理图

ZYNQ的LED分为PL和PS的部分,入门需要掌握的是PL的LED

ZYNQ的LED分为PL和PS的部分,入门需要掌握的是PL的LED

3 程序设计

实验任务:使用底板上的两个PL端LED,实现交替闪烁的效果。

本次实验程序设计的思路,假设点亮都时间为0.5s

下面开始

(1) 创建工程文件(暂不导入源文件)

小白的话建议从我这个博客看起:Vivado 2018.3入门教程:创建工程+新建源文件.

依次点击create project 、next

注意勾选,现在不指定源文件,待会儿我们自己添加

注意勾选,现在不指定源文件,待会儿我们自己添加

我的ZYNQ7020的开发板,对应的芯片型号是xc7z020clg400-2

我的ZYNQ7020的开发板,对应的芯片型号是xc7z020clg400-2

2代表速度等级,丝印上是看不到的。选1其实也可以

再依次点击next、finish

到这里,工程已经创建完毕了

(2) 新建源文件

添加或者新建一个设计源文件

点击create file

输入创建的源文件的名称

点击finish

然后自动弹出来这个框,用于指定输入输出端口(暂时不配置IO)

我们先不在这里定义了,点击yes

现在可以看到,源文件已经创建成功了

.v表示使用的是Verilog语言

然后双击打开

把前面部分全删掉

把前面部分全删掉

第一行是有关编译的,跟仿真有关,可以先删除掉

`timescale 1ns / 1ps

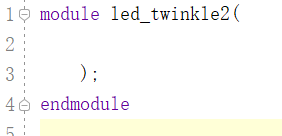

删完后,只剩底下一个module模块

(3)逻辑编写(笔记都在注释里哦)

module led_twinkle2(

//这里面定义输入输出端口,如果刚才定义了这儿就会自动生成

);

//编写用户逻辑代码

endmodule//模块结束

下面开始编写逻辑

module led_twinkle2(

//这里面定义输入输出端口,如果刚才定义了这儿就会自动生成

input clk,

input rst_n,//_n是低电平有效

output [1:0] led//建议对齐

);

//编写用户逻辑代码

reg [25:0] cnt ;

//此处需要计算,50MHz的时钟频率,1s中就要计数50000000次,换算成二进制的位宽为26位

//(2)部分

assign led = (cnt < 26'd2500_0000)? 2'b01 : 2'b10 ;

//(1)计数器部分

always @ (posedge clk or negedge rst_n)begin

if(!rst_n)//复位信号低电平有效的阶段

//当复位的时候,需要给计数器清零

cnt <= 26'd0;

else if(cnt < 26'd5000_0000)//复位结束之后,就是进行计数

cnt <= cnt + 1'b1;//是b不是d,直接over

else //等于50000000的时候,

cnt <= 26'd0; //清零,重新开始计数

end

endmodule//模块结束

(4) 管脚IO分配(前面跳过了)

然后进行管脚分配(很重要的一个步骤!)

然后,管脚分配的页面需要我们手动去打开!

然后,管脚分配的页面需要我们手动去打开!

layout->IO planning

或者直接右上角(建议!!)

或者直接右上角(建议!!)

如果对于约束文件里的 管脚分配 不太明白的,可以看看我这个博客

也就是J15 H18的选择

constraints约束文件.

上面两个图里生成的IO口配置文件内容

看这里!.

先给一张正确的图

(5)生成比特流文件

然后点击生成比特流文件

点击yes,

生成的过程需要一定的时间哦!

再点击OK

此时可以看到右上角有一个转动的圆圈,说明正在生成中

点击这个键,可以查看进度

点击这个键,可以查看进度

成功生成之后,会自动弹出这个图,看到这个图的时候,说明比特流文件生成成功!

如果不成功的话点击这儿哦,可以看看报错来解决.

(6)硬件调试

打开硬件调试窗口

方法一:直接点击"cancel",然后手动打开左下角的硬件调试串口

方法二:如图所示,然后点击OK

连接好硬件,打开电源

连接好硬件之后,open target -> autoi connect

这个表示识别出来了!

直接点击即可

直接点击即可

最后,应该就能看到两个等交替闪烁的现象了!

最后,应该就能看到两个等交替闪烁的现象了!

注意,如果在硬件调试窗口改动代码,是没有用的!

关键在于,你已经生成了一个比特流文件(类似于编译)

修改代码当然没有用了

所以正确做法:(硬件调试期间)如果修改了代码,那就得重新生成了新的比特流文件了

至于每次生成比特流文件的时间

没办法咯!

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?