Channal Link

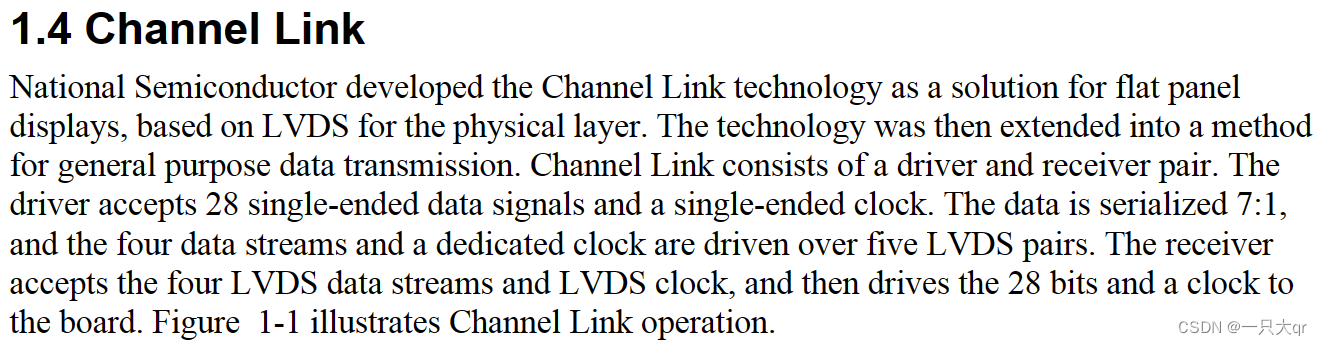

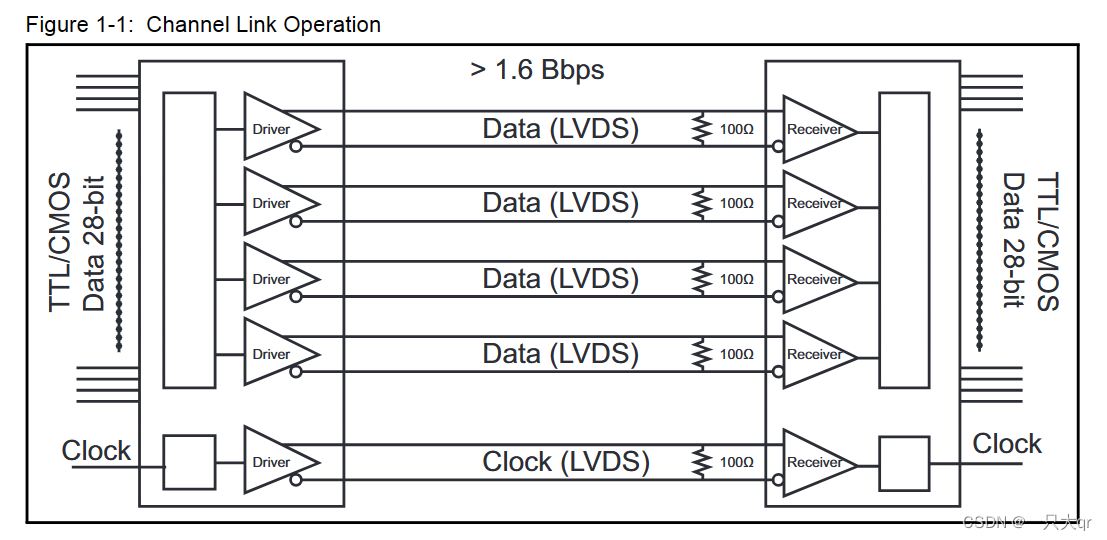

Channel-Link使用LVDS,并且配置有三个,四个或八个并行数据传输通道,以及每个配置的源同步时钟。在有线应用中,它使用一对双绞线来传输时钟信号,而在其余差分对上,它以7倍于时钟信号频率的比特率传输数字数据。除了使用差分走线而不是双绞线之外,背板应用的工作方式相同。

三个Channel-Link芯片组配置提供不同的用户界面。例如,三通道芯片组拥有21个用于用户接口的单端输入和输出,而四通道芯片组则具有28个单端输入和输出。八通道芯片组具有48个单端输入和输出,因为它使用7个串行比特/通道中的一个来对另外6个比特进行DC平衡。

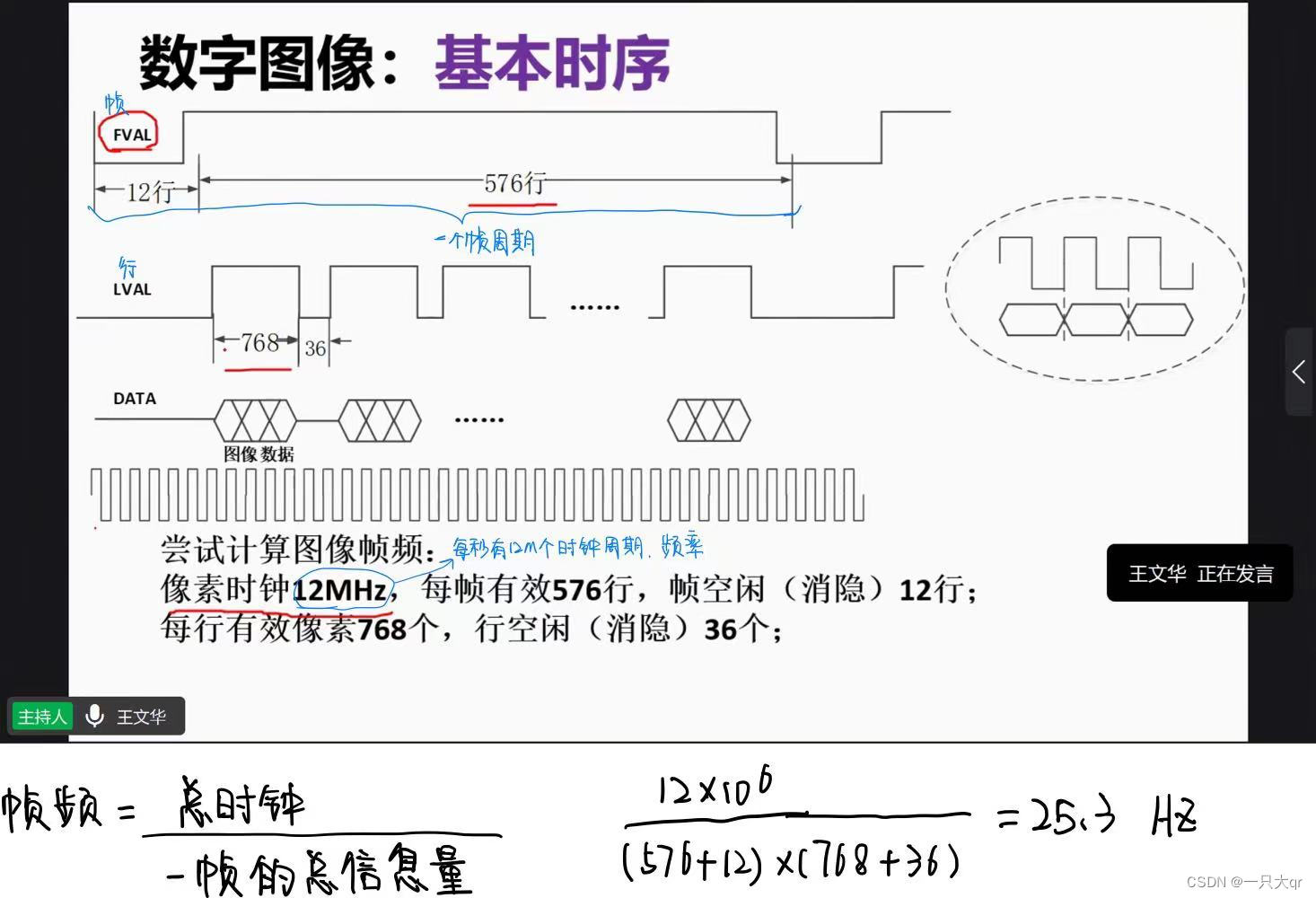

FVAL LVAL DVAL Spare

API

百度定义:API(Application Programming Interface,应用程序编程接口)是一些预先定义的函数,目的是提供应用程序与开发人员基于某软件或硬件得以访问一组例程的能力,而又无需访问源码,或理解内部工作机制的细节。

从编程角度来讲,就是一个封装好的函数

用编程语言FPGA实现cameralink接口芯片

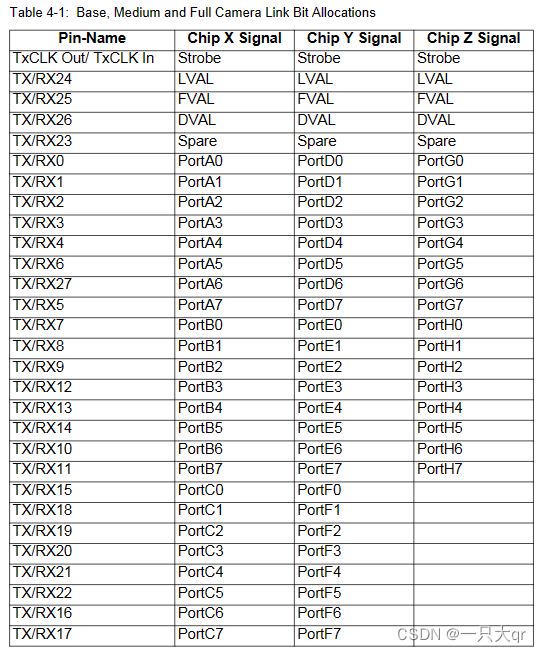

- 在cameralink v2.0 数据手册中查找 channel link 芯片管脚分配(bit allocation)

标准 cameralink 8 taps

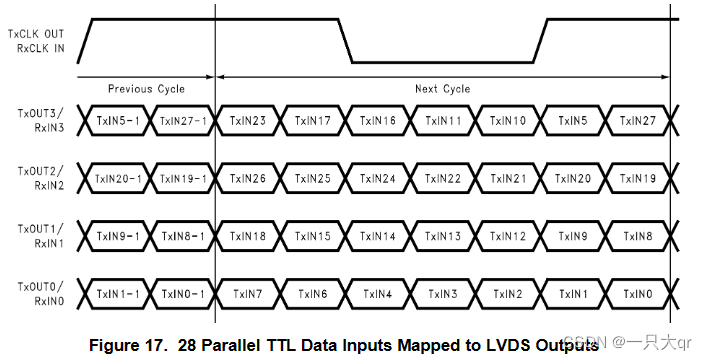

- 在channel link 芯片(如DS90CR285)手册中找到 28位并行TTL数据输入与LVDS输出的映射关系(通用)

- 根据 bit分配和映射关系 编写Verilog程序,实现(代替)芯片功能

---standard Camlink 8 taps

cx_data3 <='0' & chan_2(7) & chan_2(6) & chan_1(7) & chan_1(6) & chan_0(7) & chan_0(6) ;

cx_data2 <='0' & FVAL & LVAL & chan_2(5) & chan_2(4) & chan_2(3) & chan_2(2) ;

cx_data1 <=chan_2(1) & chan_2(0) & chan_1(5) & chan_1(4) & chan_1(3) & chan_1(2) & chan_1(1) ;

cx_data0 <=chan_1(0) & chan_0(5) & chan_0(4) & chan_0(3) & chan_0(2) & chan_0(1) & chan_0(0) ;

cy_data3 <='0' & chan_5(7) & chan_5(6) & chan_4(7) & chan_4(6) & chan_3(7) & chan_3(6) ;

cy_data2 <='0' & FVAL & LVAL & chan_5(5) & chan_5(4) & chan_5(3) & chan_5(2) ;

cy_data1 <=chan_5(1) & chan_5(0) & chan_4(5) & chan_4(4) & chan_4(3) & chan_4(2) & chan_4(1) ;

cy_data0 <=chan_4(0) & chan_3(5) & chan_3(4) & chan_3(3) & chan_3(2) & chan_3(1) & chan_3(0) ;

cz_data3 <='0' & '0' & '0' & chan_7(7) & chan_7(6) & chan_6(7) & chan_6(6) ;

cz_data2 <='0' & FVAL & LVAL & '0' & '0' & '0' & '0' ;

cz_data1 <='0' & '0' & chan_7(5) & chan_7(4) & chan_7(3) & chan_7(2) & chan_7(1) ;

cz_data0 <=chan_7(0) & chan_6(5) & chan_6(4) & chan_6(3) & chan_6(2) & chan_6(1) & chan_6(0) ;

PortA–PortH 对应 chan_0–chan_7 共8个taps

TxIN0 位置对应芯片管脚 X信号的PortA0(chan_0(0))、Y信号的PortD0(chan_3(0))、Z信号的PortG0(chan_6(0))

TxIN14 位置对应芯片管脚 X信号的PortB5(chan_1(5))、Y信号的PortE5(chan_4(5))、Z信号的PortH5(chan_7(5))

2775

2775

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?