提示:文章写完后,目录可以自动生成,如何生成可参考右边的帮助文档

提示:以下是本篇文章正文内容,下面案例可供参考

一、数字识别方法

目前数字识别的方法有:模板匹配、画线取交点特征、cnn等,都是对数字的相关特征进行提取比较。本文介绍其中的画线取交点特征的方法,这种方法实现简单,适合刚开始学习的小白。

二、画线取交点特征的方法

此方法引用自:https://www.cnblogs.com/leegod/p/8929678.html

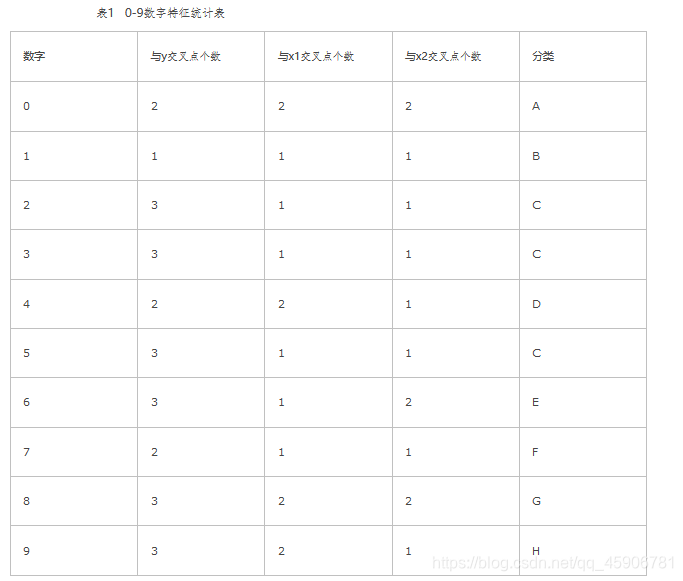

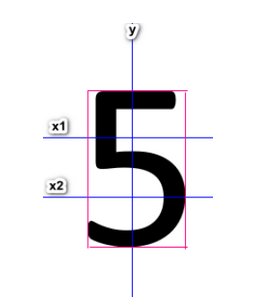

横向画两条线,纵向画一条线,提取交点特征,列表如下:

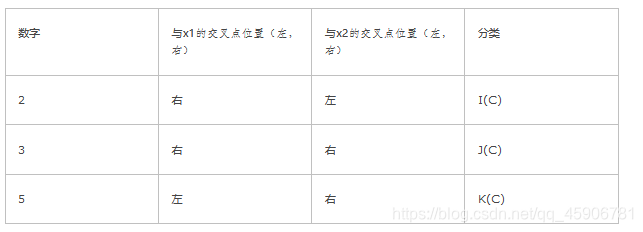

这里看到此方法中三个特征不足以区分10个数字,其中2、3、5交点数一样,所以交点位置也作为一个特征来区分这三个数字。区分后列表如下:

在FPGA实现时,需要先进行每个数字的边界定位,然后再对每个数字进行识别。

边界检测的状态机部分的代码:

state machine

always@(*)

begin

case(cur_state)

IDLE:

begin

if(lcd_de)

next_state <= U_DETECT;

else

next_state <= IDLE;

end

U_DETECT:

begin

if(u_done)

next_state <= L_DETECT;

else

next_state <= U_DETECT;

end

L_DETECT:

begin

if(l_done)

next_state <= R_DETECT;

else if((pixel_xpos == row - 1) && (pixel_ypos == col - 5))

next_state <= DETECT_DONE;

else

next_state <= L_DETECT;

end

R_DETECT:

begin

if(pixel_xpos < row - 1)

if(r_done || (pixel_ypos == col - 1))

next_state <= L_DETECT;

else

next_state <= R_DETECT;

else

next_state <= DETECT_DONE;

end

DETECT_DONE:

begin

next_state <= WAIT;

end

WAIT:

begin

if(frame_done == 1'b1)

next_state <= IDLE;

else

next_state <= WAIT;

end

default:

begin

next_state <= IDLE;

end

endcase

end

数字识别部分代码:

//y x1_l x1_r x2_l x2_r

localparam num_0 = 6'b10_1_1_1_1; //2 1 1 1 1

localparam num_1 = 6'b01_1_0_1_0; //1 1 0 1 0

localparam num_2 = 6'b11_0_1_1_0; //3 0 1 1 0

localparam num_3 = 6'b11_0_1_0_1; //3 0 1 0 1

localparam num_4 = 6'b10_1_1_1_0; //2 1 1 1 0

localparam num_5 = 6'b11_1_0_0_1; //3 1 0 0 1

localparam num_6 = 6'b11_1_0_1_1; //3 1 0 1 1

localparam num_7 = 6'b10_0_1_1_0; //2 0 1 0 1

localparam num_8 = 6'b11_1_1_1_1; //3 1 1 1 1

localparam num_9 = 6'b11_1_1_0_1; //3 1 1 0 1

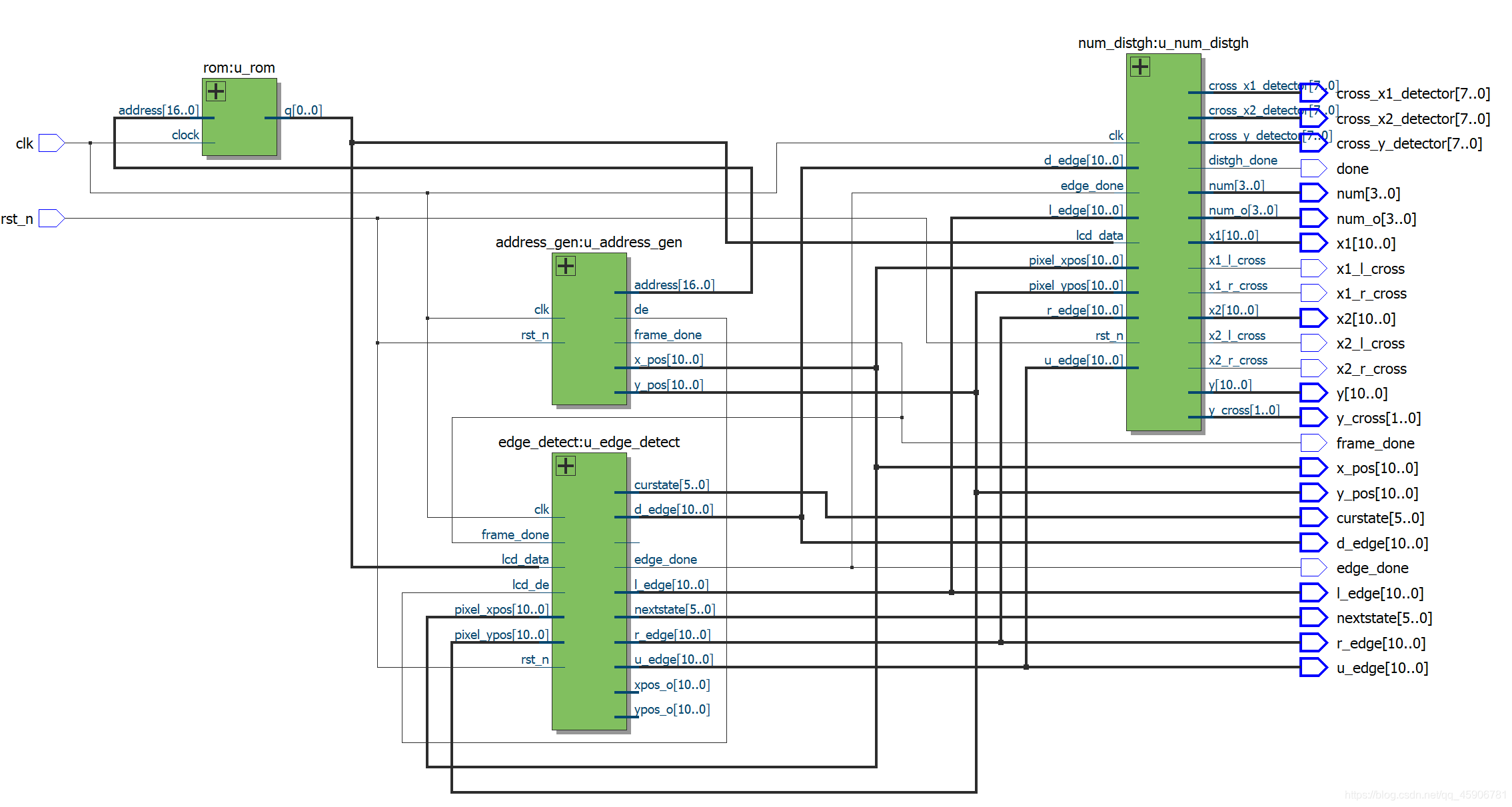

三、总体测试框图

这里展示用于软件仿真测试的结构框图:

这里的部分输出仅仅为了方便观察仿真结果。

这里的部分输出仅仅为了方便观察仿真结果。

全部verilog代码下载链接:https://download.csdn.net/download/qq_45906781/20326235

3891

3891

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?