实验目的:

通过实验掌握下列知识:

- 理解原码一位乘法器的原理;

- 理解补码一位乘法器的原理;

- 掌握Logisim中寄存器组件的使用;

- 理解简单数据通路和数据通路控制

- 设计8位×8位的无符号一位乘法器

- 设计实现8位×8位的补码一位乘法器

实验内容:

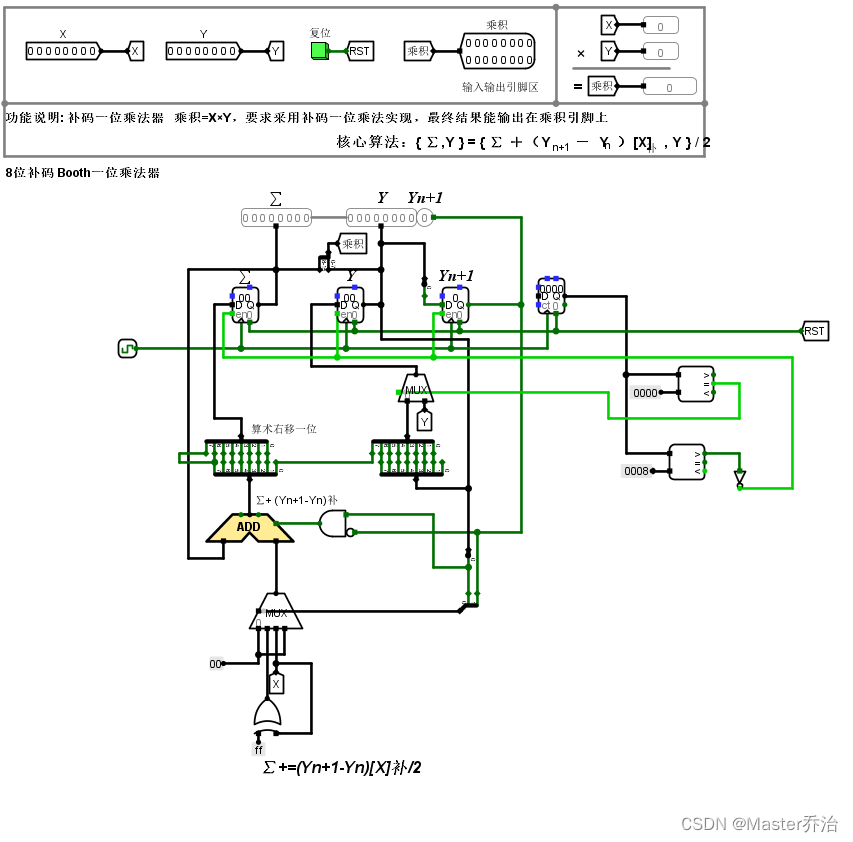

1、 设计实现8位×8位的无符号一位乘法器:

设计思路: 由原码一位乘的过程(依次对乘数的Yi进行判断,为1则部分积加上被来数,为0就不加,然后通过将乘数和部分积逻辑右移一位实现来法)来添加电路: -逻辑移位部分:用错开的两个分离器将8位数分开,8*8就需要4个分离器,前两个组合的分离器连到部分积,后两个组合的分离器通过数据选择器连到Y,每个时钟都要右移一位: -加法部分:用Y的最低位来判断部分积是否加上被乘数X,需要用到数据选择器,考虑到从Y那里输出的位宽问题,八位中的高七位不能选,就需要用到分离器; -时钟周期部分:需要用到计数器,第一个时钟周期输入Y的值到寄存器中,其他的周期进行黑加和移龙操作,操作完成要停机,所以要用到比较器设置时序信号STOP,用隧道实现; -运算完成:要将寄存器使能端置0,用一个非门实现.

电路图:

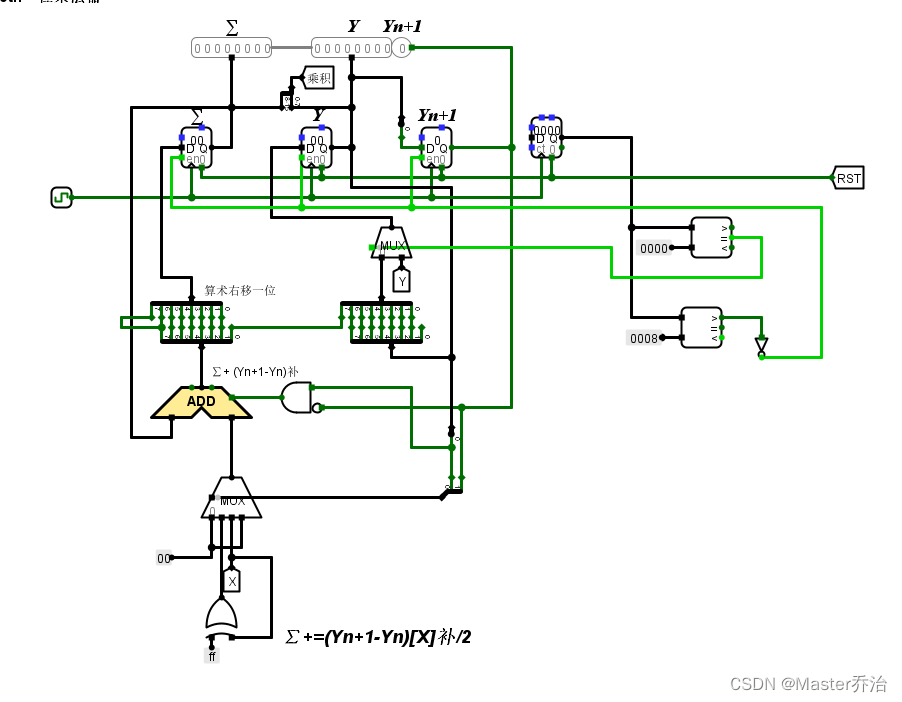

2、 设计实现8位×8位的无符号一位乘法器:

设计思原理:在计算两个补码相乘时,可以通过Booth 算法来实现定点补码一位乘的功能。布斯(Booth) 算法采用相加和相减的操作计算补码数据的乘积,Booth 算法对乘数从从低位开场判断,根据后两个数据位的情况决定进展加法、减法还是仅仅进展移位操作。讨论当相乘的两个数中有一个或二个为负数的情况,在讨论补码乘法运算时,对被乘数或局部积的处理上与原码乘法有某些类似,差异仅表现在被乘数和局部积的符号位要和数值一起参加运算。Booth 乘法规那么如下:假设X、Y都是用补码形式表示的机器数,[补和[Y]补=YS.Y1Y2…Yn,都是任意符号表示的数。比拟法求新的局部积,取决于两个比拟位的数位,即 Yit1Yi的状态。

首先设置附加位 Yn+1=0,局部积初值(Z0]补=0。当几大0时,判断 YnYn+1,假设 YnYn+1-00 或11,即相邻位一样时,上次局部积右移一位,直接得局部积。假设 YnYn+1=01,上次局部积加口]补,然后右移一位得新局部积。

假设 YnYn+1=10,上次局部积加[-X]补,然后右移一位得新局部积。

当口0时,判YnYnt1(对应于 YOY1),运算规那么同(1)只是不移位。即在运算的最后一步,成绩不在右移。

设计思路:

首先要采用原码值输入,乘数和被乘数皆为8位。而且根据补码一位乘法运

算规那么:(1)如果yn=yntl,局部积[zi〕加0,再右移一位:(2)如果ynt1=01,局部积加[x ]补,再右移一位:(3)如果yn ynt1=10,局部积加[-×]补,再右移一位:这样重复进展 吐1 步,但最后一步不移位。包括一位符号位,所得乘积为 2n+1 位,其中口为尾数位数,设计一个二输入三选一选择器对可能的三种情况进展选择。中选择器中输入为 YiYi+1为00 或者11时,由一存放器一端接 GND,另一端对其进展零输入中选择器中输入为 Yi Yit1 为01时,对其进展【]补输入:中选择器中输入为 YiYit1为10时,对(X补输入端加一非门和一加法器对其进展取反加1输入。输出结果与一个一端接GND 初始署零的存放器相连接于一个加法器,实现局部积加法运算:计算结果存放于两个一样的移位存放器中,当局部积相加之后,由两个移位存放器同时对局部积的和进展移位操作。最后由两个移位存放器的输出端连接至选择器重新选择进展循环操作,直到局部积移位完牛。 具体实现如下所示:

思考和总结:

通过实验理解原码一位乘法器的原理,并且理解补码一位乘法器的原理两者是相差不多的。掌握Logisim中寄存器组件的使用;理解简单数据通路和数据通路控制。成功设计8位×8位的无符号一位乘法器,并且成功设计实现8位×8位的补码一位乘法器

实验资源在这里:

https://download.csdn.net/download/qq_46037206/87340324

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?